M7A3P1000-2FG144ES View Datasheet(PDF) - Unspecified

Part Name

Description

Manufacturer

M7A3P1000-2FG144ES Datasheet PDF : 196 Pages

| |||

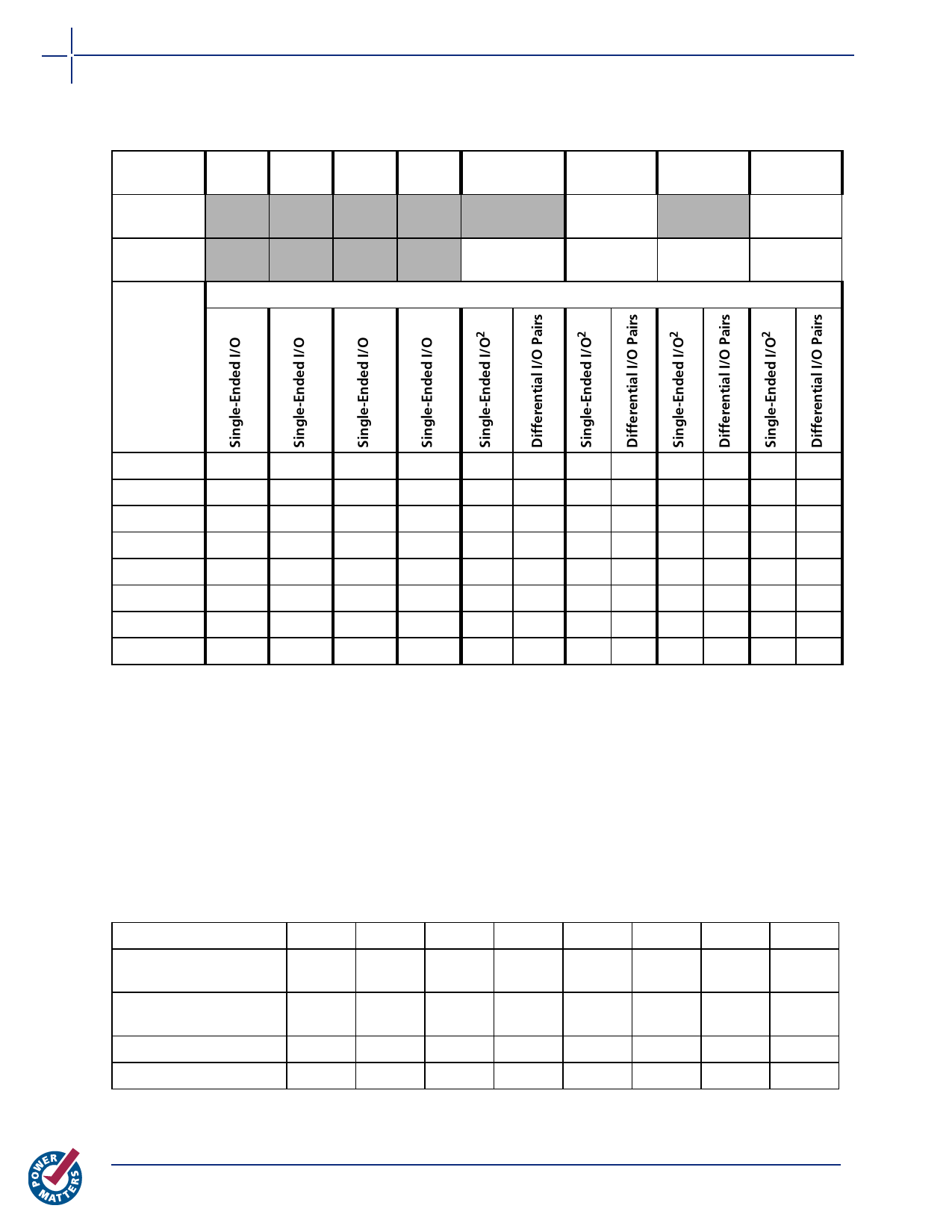

I/Os Per Package1

ProASIC3

Devices

ARM7

Devices

Cortex-M1

Devices

A3P015 A3P030 A3P060 A3P125 A3P250 3

A3P400 3

A3P600

A3P1000

M7A3P1000

M1A3P250 3,6 M1A3P400 3 M1A3P600 M1A3P1000

I/O Type

Package

QN68

49

–

–

–

–

–

–

–

–

–

–

QN132

–

81

80

84

87

19

–

–

–

–

–

VQ100

–

77

71

71

68

13

–

–

–

–

–

TQ144

–

–

91

100

–

–

–

–

–

–

–

–

PQ208

–

–

–

133 151 34 151 34 154 35 154 35

FG144

–

–

96

97

97

24 97 25 97 25 97 25

FG256

–

–

–

–

157 38 178 38 177 43 177 44

FG484

–

–

–

–

–

– 194 38 235 60 300 74

Notes:

1. When considering migrating your design to a lower- or higher-density device, refer to the ProASIC3 Flash

Family FPGAs handbook to ensure complying with design and board migration requirements.

2. Each used differential I/O pair reduces the number of single-ended I/Os available by two.

3. For A3P250 and A3P400 devices, the maximum number of LVPECL pairs in east and west banks cannot

exceed 15. Refer to the ProASIC3 Flash Family FPGAs t handbook for position assignments of the 15 LVPECL

pairs.

4. FG256 and FG484 are footprint-compatible packages.

5. "G" indicates RoHS-compliant packages. Refer to "ProASIC3 Ordering Information" on page 3 for the

location of the "G" in the part number.

6. The M1A3P250 device does not support FG256 or QN132 packages.

Table 1-2 • ProASIC3 FPGAs Package Sizes Dimensions

Package

QN68 QN132 VQ100

Length √ó Width

(mm \ mm)

8√ó8

8 √ó 8 14 √ó 14

Nominal Area

(mm2)

64

64

196

Pitch (mm)

0.4

0.5

0.5

Height (mm)

0.90

0.75

1.00

TQ144

20 √ó 20

400

0.5

1.40

PQ208

28 √ó 28

784

0.5

3.40

FG144

13 √ó 13

169

1.0

1.45

FG256

17 √ó 17

289

1.0

1.60

FG484

23 √ó 23

529

1.0

2.23

1-2

Product Brief