LH28F016SU View Datasheet(PDF) - Sharp Electronics

Part Name

Description

Manufacturer

LH28F016SU Datasheet PDF : 37 Pages

| |||

16M (1M √ó 16, 2M √ó 8) Flash Memory

LH28F016SU

PIN DESCRIPTION (Continued)

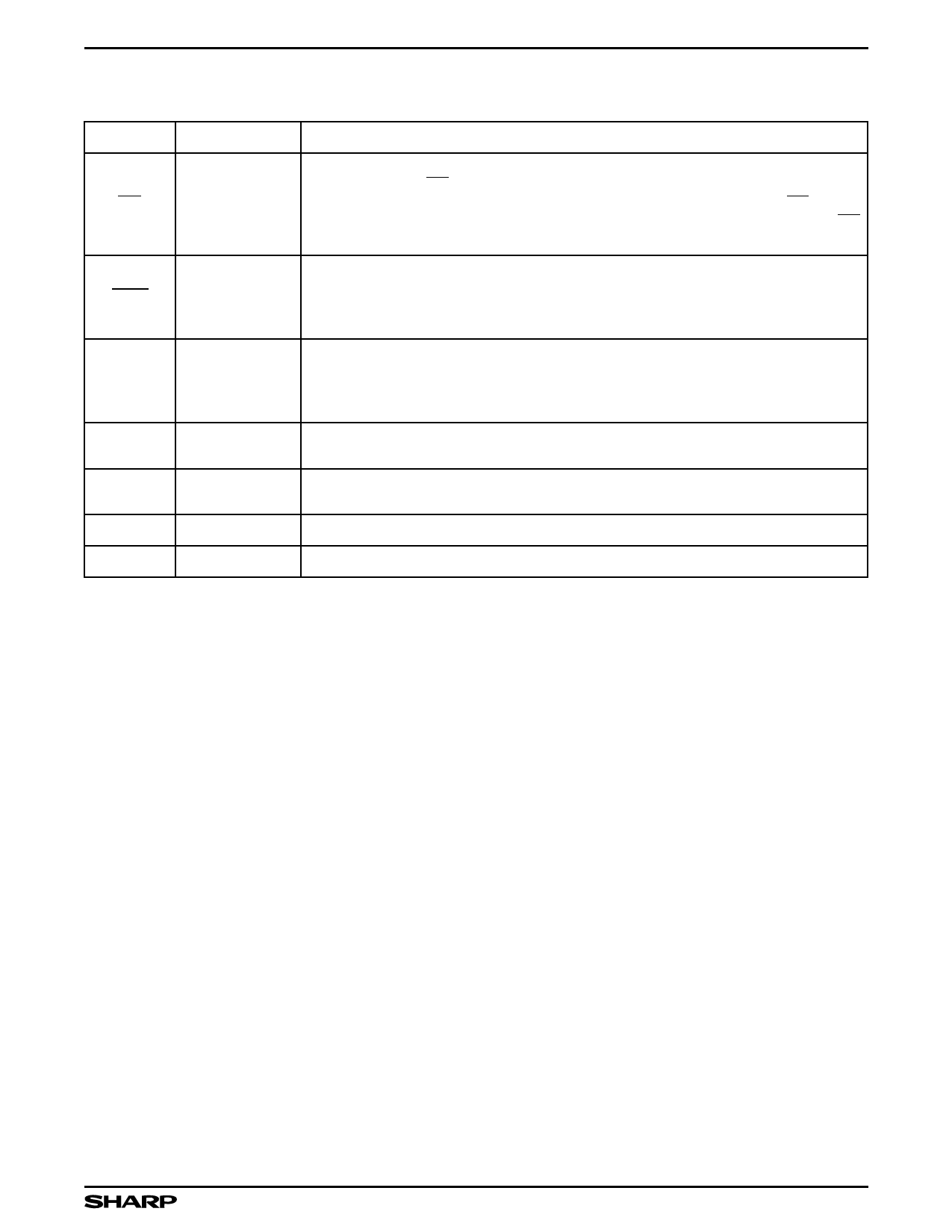

SYMBOL

TYPE

WP

INPUT

BYTE INPUT

3/5 »

INPUT

VPP

VCC

GND

NC

SUPPLY

SUPPLY

SUPPLY

NAME AND FUNCTION

WRITE PROTECT: Erase blocks can be locked by writing a non-volatile lock-bit for

each block. When WP is low, those locked blocks as reflected by the Block-Lock Status

bits (BSR.6), are protected from inadvertent Data Writes or Erases. When WP is high,

all blocks can be Written or Erased regardless of the state of the lock-bits. The WP

input buffer is disabled when RP» transitions low (deep power-down mode).

BYTE ENABLE: BYTE low places device x8 mode. All data is then input or output

on DQ0 - DQ7, and DQ8 - DQ15 float. Address A0 selects between the high and low

byte. BYTE high places the device in x16 mode, and turns off the A0 input buffer.

Address A1, then becomes the lowest order address.

3.3/5.0 VOLT SELECT: 3/5 » high configures internal circuits for 3.3 V operation. 3/5»

low configures internal circuits for 5.0 V operation.

NOTES: Reading the array with 3/5» high in a 5.0 V system could damage the

device. There is a significant delay from 3/5» switching to valid data.

ERASE/WRITE POWER SUPPLY: For erasing memory array blocks or writing

words/bytes/pages into the flash array.

DEVICE POWER SUPPLY (3.3 V ±0.3 V, 5.0 V ±0.5 V) (2.7 V ~ 3.6 V at Read

Operation): Do not leave any power pins floating.

GROUND FOR ALL INTERNAL CIRCUITRY: Do not leave any ground pins floating.

NO CONNECT: No internal connection to die, lead may be driven or left floating.

A Command User Interface (CUI) serves as the sys-

tem interface between the microprocessor or

microcontroller and the internal memory operation.

Internal Algorithm Automation allows Byte/Word

Writes and Block Erase operations to be executed

using a Two-Write command sequence to the CUI in

the same way as the LH28F008SA 8M Flash memory.

A Superset of commands have been added to the

basic LH28F008SA command-set to achieve higher

write performance and provide additional capabilities.

These new commands and features include:

• Page Buffer Writes to Flash

• Command Queuing Capability

• Automatic Data Writes During Erase

• Software Locking of Memory Blocks

• Two-Byte Successive Writes in 8-bit Systems

• Erase All Unlocked Blocks

Writing of memory data is performed in either byte or

word increments typically within 8 µs, a 25% improve-

ment over the LH28F008SA. A Block Erase operation

erases one of the 32 blocks in typically 0.7 seconds,

independent of the other blocks, which is about 55%

improvement over the LH28F008SA.

The LH28F016SU incorporates two Page Buffers of

256 Bytes (128 Words) each to allow page data writes.

This feature can improve a system write performance

over previous flash memory devices.

All operations are started by a sequence of Write

commands to the device. Three Status Registers

(described in detail later) and a RY »/BY » output pin

provide information on the progress of the requested

operation.

While the LH28F008SA requires an operation to com-

plete before the next operation can be requested, the

LH28F016SU allows queuing of the next operation while

the memory executes the current operation. This elimi-

nates system overhead when writing several bytes in a

row to the array or erasing several blocks at the same

time. The LH2F016SUR-10 can also perform write op-

erations to one block of memory while performing erase

of another block.

The LH28F016SU provides user-selectable block

locking to protect code or data such as Device Drivers,

PCMCIA card information, ROM-Executable O/S or

Application Code. Each block has an associated non-

volatile lock-bit which determines the lock status of the

block. In addition, the LH28F016SU has a master Write

Protect pin (WP ») which prevents any modifications to

memory blocks whose lock-bits are set.

5