NT5CB128M8DN View Datasheet(PDF) - Nanya Technology

Part Name

Description

Manufacturer

NT5CB128M8DN Datasheet PDF : 138 Pages

| |||

NT5CB128M8DN/NT5CB64M16DP

NT5CC128M8DN/NT5CC64M16DP

1Gb DDR3 D-die SDRAM

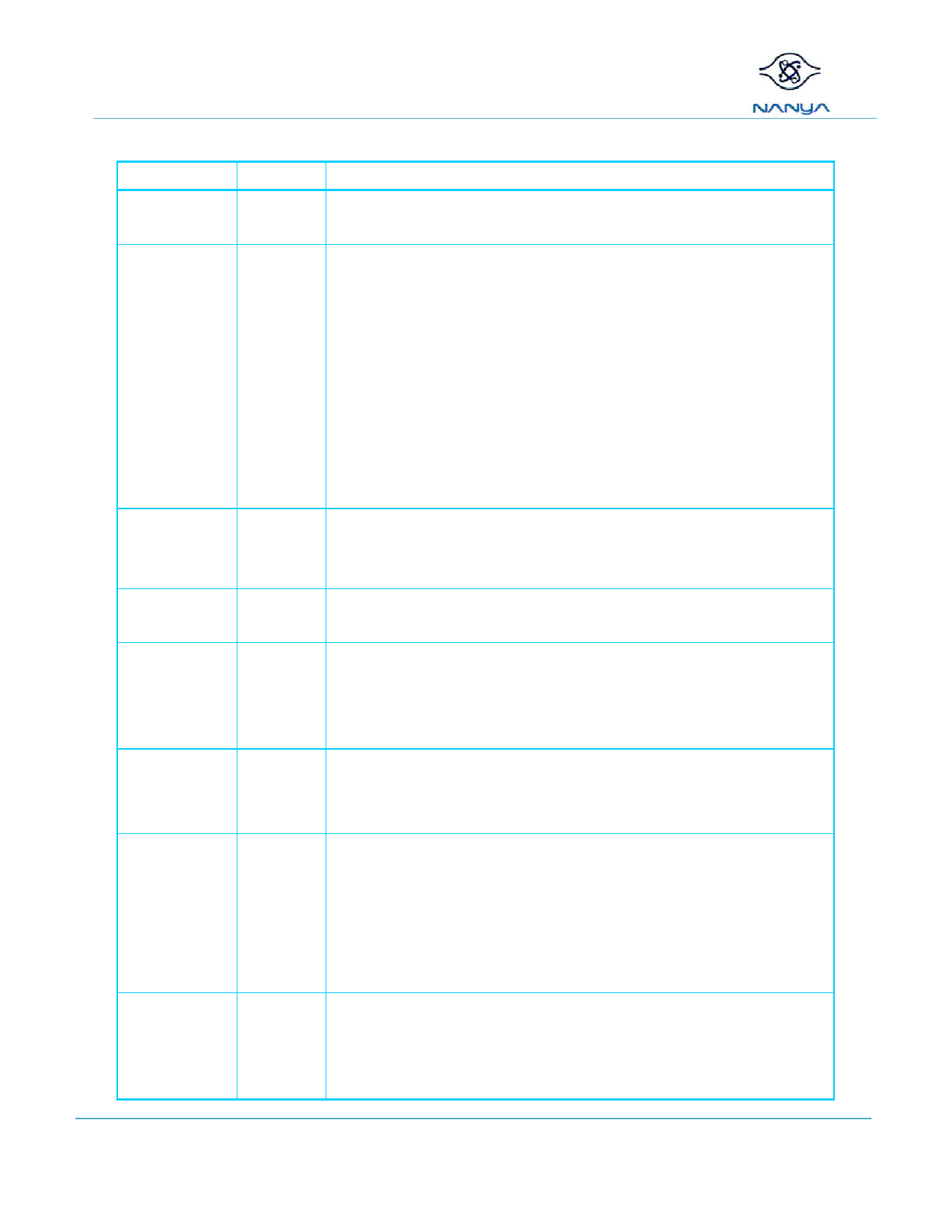

Table 2: Input / Output Functional Description

Symbol

Type

Function

CK,

CKE, (CKE0),

(CKE1)

, ( ), ( ),

( ), ( )

,,

Input

Input

Input

Input

Clock: CK and are differential clock inputs. All address and control input signals are

sampled on the crossing of the positive edge of CK and negative edge of .

Clock Enable: CKE high activates, and CKE low deactivates, internal clock signals

and device input buffers and output drivers. Taking CKE low provides Precharge

Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row

Active in any bank). CKE is synchronous for power down entry and exit and for

Self-Refresh entry. CKE is asynchronous for Self-Refresh exit. After VREF has

become stable during the power on and initialization sequence, it must be maintained

for proper operation of the CKE receiver. For proper self-refresh entry and exit, VREF

must maintain to this input. CKE must be maintained high throughout read and write

accesses. Input buffers, excluding CK, , ODT and CKE are disabled during Power

Down. Input buffers, excluding CKE, are disabled during Self-Refresh.

Chip Select: All commands are masked when is registered high. provides for

external rank selection on systems with multiple memory ranks. is considered part

of the command code.

Command Inputs: , and (along with ) define the command being

entered.

DM, (DMU, DML)

Input

Input Data Mask: DM is an input mask signal for write data. Input data is masked when

DM is sampled HIGH coincident with that input data during a Write access. DM is

sampled on both edges of DQS. For x8 device, the function of DM or TDQS /

is

enabled by Mode Register A11 setting in MR1

BA0 - BA2

Input

Bank Address Inputs: BA0, BA1, and BA2 define to which bank an Active, Read,

Write or Precharge command is being applied. Bank address also determines which

mode register is to be accessed during a MRS cycle.

A10 / AP

A0 – A13

Input

Input

Auto-Precharge: A10 is sampled during Read/Write commands to determine whether

Autoprecharge should be performed to the accessed bank after the Read/Write

operation. (HIGH: Autoprecharge; LOW: no Autoprecharge). A10 is sampled during a

Precharge command to determine whether the Precharge applies to one bank (A10

LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is

selected by bank addresses.

Address Inputs: Provide the row address for Activate commands and the column

address for Read/Write commands to select one location out of the memory array in

the respective bank. (A10/AP and A12/ have additional function as below.) The

address inputs also provide the op-code during Mode Register Set commands.

REV 1.2

May. 2011

CONSUMER DRAM

© NANYA TECHNOLOGY CORP.

All rights reserved

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.