TX9956C View Datasheet(PDF) - Toshiba

Part Name

Description

Manufacturer

TX9956C Datasheet PDF : 23 Pages

| |||

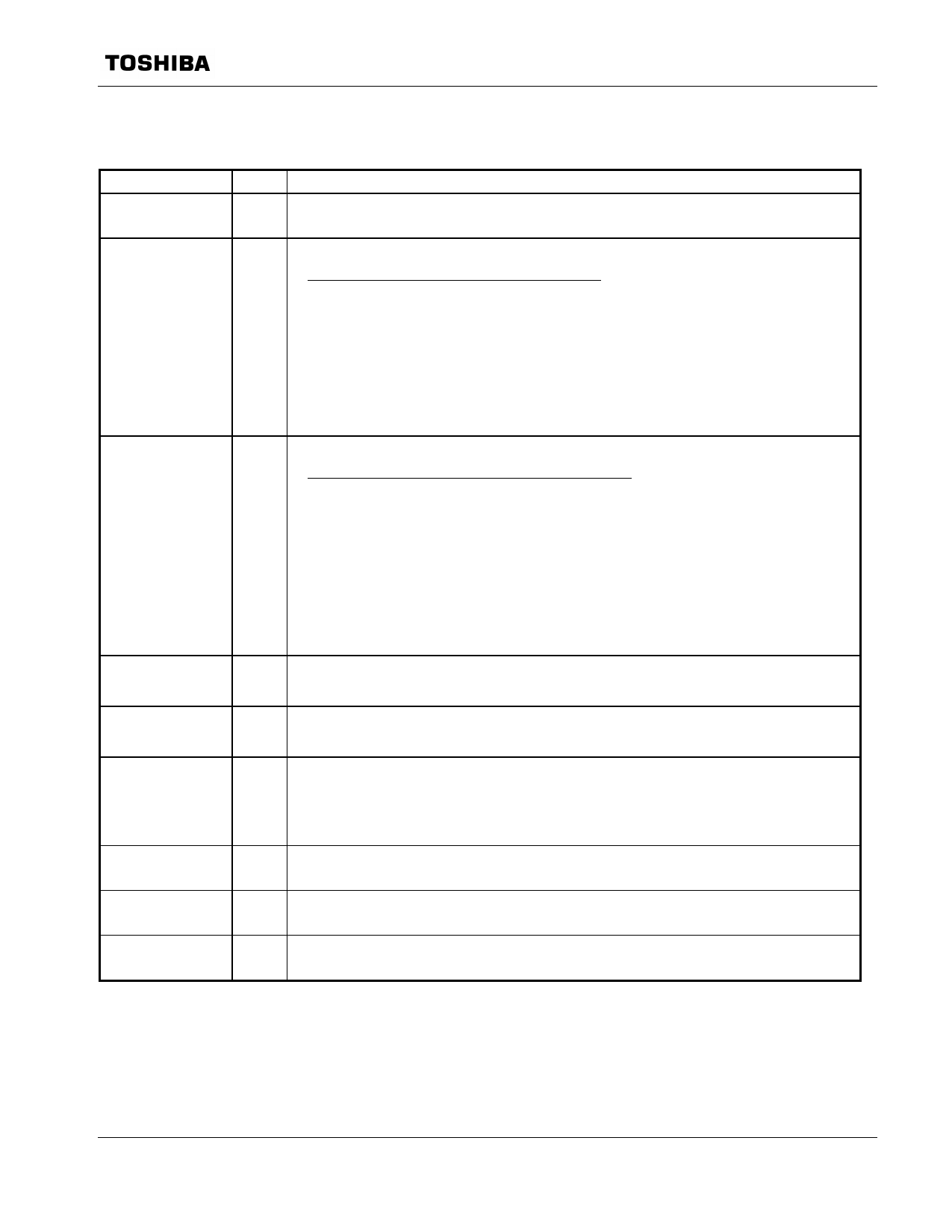

Preliminary

TX9956CXBG

CLOCK / CONTROL INTERFACE

PIN NAME

MasterClock

CoreDiv(3:0)

SysDiv(2:0)

Sleep

RP

Endian

L2Bypass

BypassPLL

BypassCoreCG

I/O

FUNCTION

Master clock

I

Master clock input that establishes the processor operating frequency.

Set the operational frequency of TX99H4 Core vs L2 Cache

CoreDiv( 3:0 )

CPU Core : L2 Cache

0000

Reserved

0001

2:1

I

0010

3:1

0011

4:1

0100, 0101, 0110, 0111,

1000, 1001, 1010, 1011,

1100, 1101, 1110, 1111 Reserved

Set the operational frequency of MBG II bus vs SysAD Bus

SysDiv( 2:0 )

MGB II bus : SysAD bus I/F

000

Reserved

001

Reserved

010

2:1

I

011

3:1

100

4:1

101

Reserved

110

Reserved

111

Reserved

Sleep mode

O

RP mode

O

Endianess input

Indicates the initial setting of the endian during a reset.

I

0 Little Endian

1 Big Endian

L2 Cache Bypass Mode

I

Test Mode

I

I

Test Mode

TX9956CXBG 2004-4-25 9