ADF7021BCPZ_06 View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

ADF7021BCPZ_06 Datasheet PDF : 44 Pages

| |||

Preliminary Technical Data

ADF7021

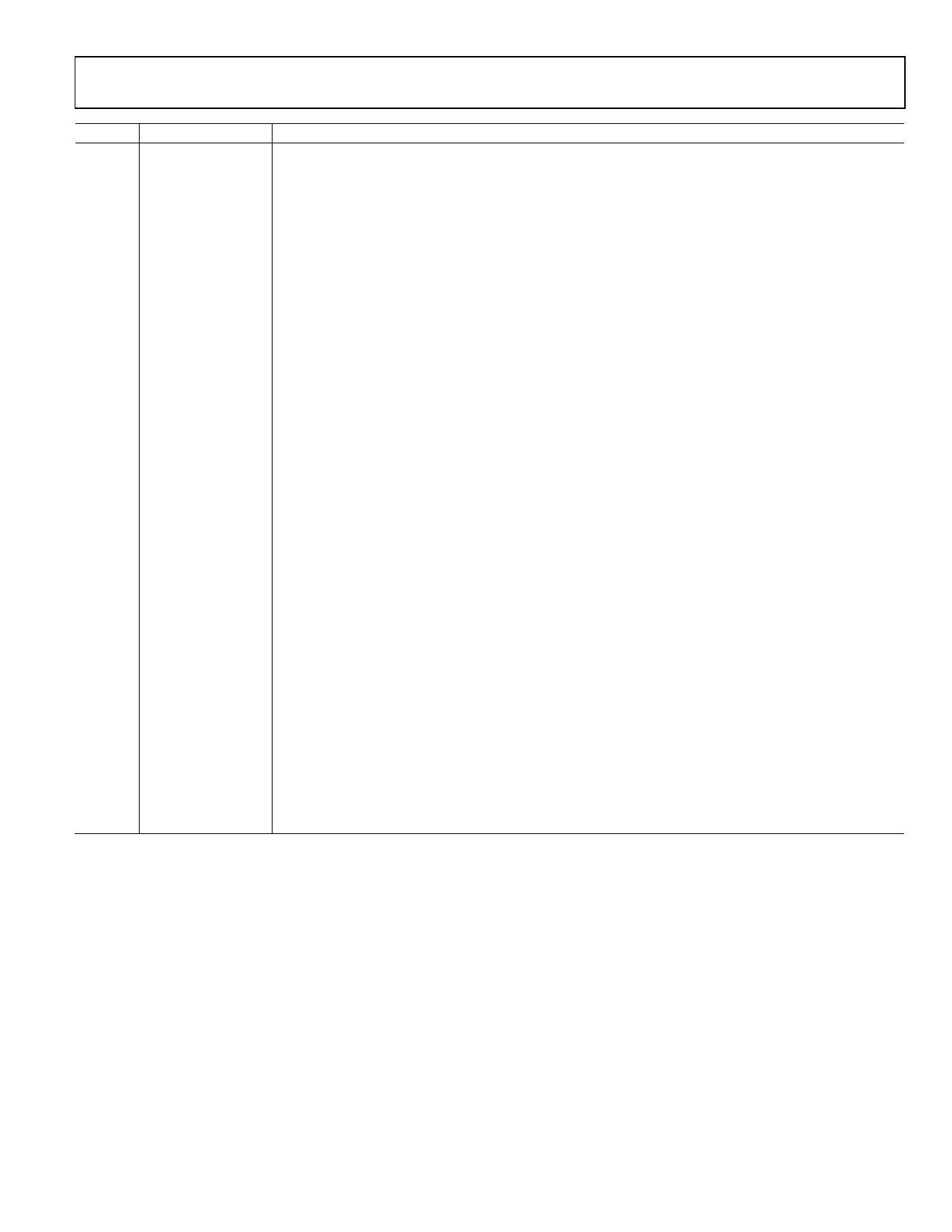

Pin No. Mnemonic

28

SCLK

29

GND2

30

ADCIN

31

CREG2

32

VDD2

33

SWD

34

DATA I/O | RxDATA

35

DATA CLK | TxDATA

36

CLKOUT

37

MUXOUT

38

39

40

41

42

43

44, 46

OSC2

OSC1

VDD3

CREG3

CPOUT

VDD

L2, L1

45, 47

48

GND, GND1

CVCO

Function

Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched

into the 24-bit shift register on the CLK rising edge. This pin is a digital CMOS input.

Ground for Digital Section.

Analog-to-Digital Converter Input. The internal 7-bit ADC can be accessed through this pin. Full scale is 0 V

to 1.9 V. Readback is made using the SREAD pin.

Regulator Voltage for Digital Block. A 100 nF capacitor should be placed between this pin and ground for

regulator stability and noise rejection.

Voltage Supply for Digital Block. A decoupling capacitor of 10 nF should be placed as close as possible to

this pin.

Sync Word Detect. The ADF7021 asserts this pin when it has found a match for the sync word sequence

(See the Register 11—Sync Word Detect Register section). This provides an interrupt for an external

microcontroller indicating valid data is being received.

Transmit Data Input/Received Data Output. This is a digital pin and normal CMOS levels apply.

In UART mode, this pin provides an output for the received data in receive mode. In transmit mode, this

pin is high impedance (see the Register 0—N Register section).

Outputs the data clock in both receive and transmit modes. This is a digital pin and normal CMOS levels

apply. The positive clock edge is matched to the center of the received data. In transmit mode, this pin

outputs an accurate clock to latch the data from the microcontroller into the transmit section at the exact

required data rate. In UART mode, this pin is used to input the transmit data in transmit mode. In receive

mode, this pin is high impedance (see the Register 0—N Register section).

A Divided-Down Version of the Crystal Reference with Output Driver. The digital clock output can be used to

drive several other CMOS inputs such as a microcontroller clock. The output has a 50:50 mark-space ratio.

Provides the Lock_Detect Signal. This signal is used to determine if the PLL is locked to the correct

frequency. Other signals include Regulator_Ready, which is an indicator of the status of the serial interface

regulator (see the Register 0—N Register section).

The reference crystal should be connected between this pin and OSC1. A TCXO reference can be used by

driving this pin with CMOS levels and disabling the crystal oscillator.

The reference crystal should be connected between this pin and OSC2.

Voltage Supply for the Charge Pump and PLL Dividers. This pin should be decoupled to ground with a

10 nF capacitor.

Regulator Voltage for Charge Pump and PLL Dividers. A 100 nF capacitor should be placed between this

pin and ground for regulator stability and noise rejection.

Charge Pump Output. This output generates current pulses that are integrated in the loop filter. The

integrated current changes the control voltage on the input to the VCO.

Voltage Supply for VCO Tank Circuit. This pin should be decoupled to ground with a 10 nF capacitor.

External VCO Inductor Pins. If using an external VCO inductor, a chip inductor should be connected across

these pins to set the VCO operating frequency. If using the internal VCO inductor, these pins can be left

floating. See the Voltage Controlled Oscillator (VCO) section for more information.

Grounds for VCO Block.

A 22 nF capacitor should be placed between this pin and CREG1 to reduce VCO noise.

Rev. PrI | Page 11 of 44