MPC8541PXALF View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

MPC8541PXALF

MPC8541PXALF Datasheet PDF : 88 Pages

| |||

DDR SDRAM

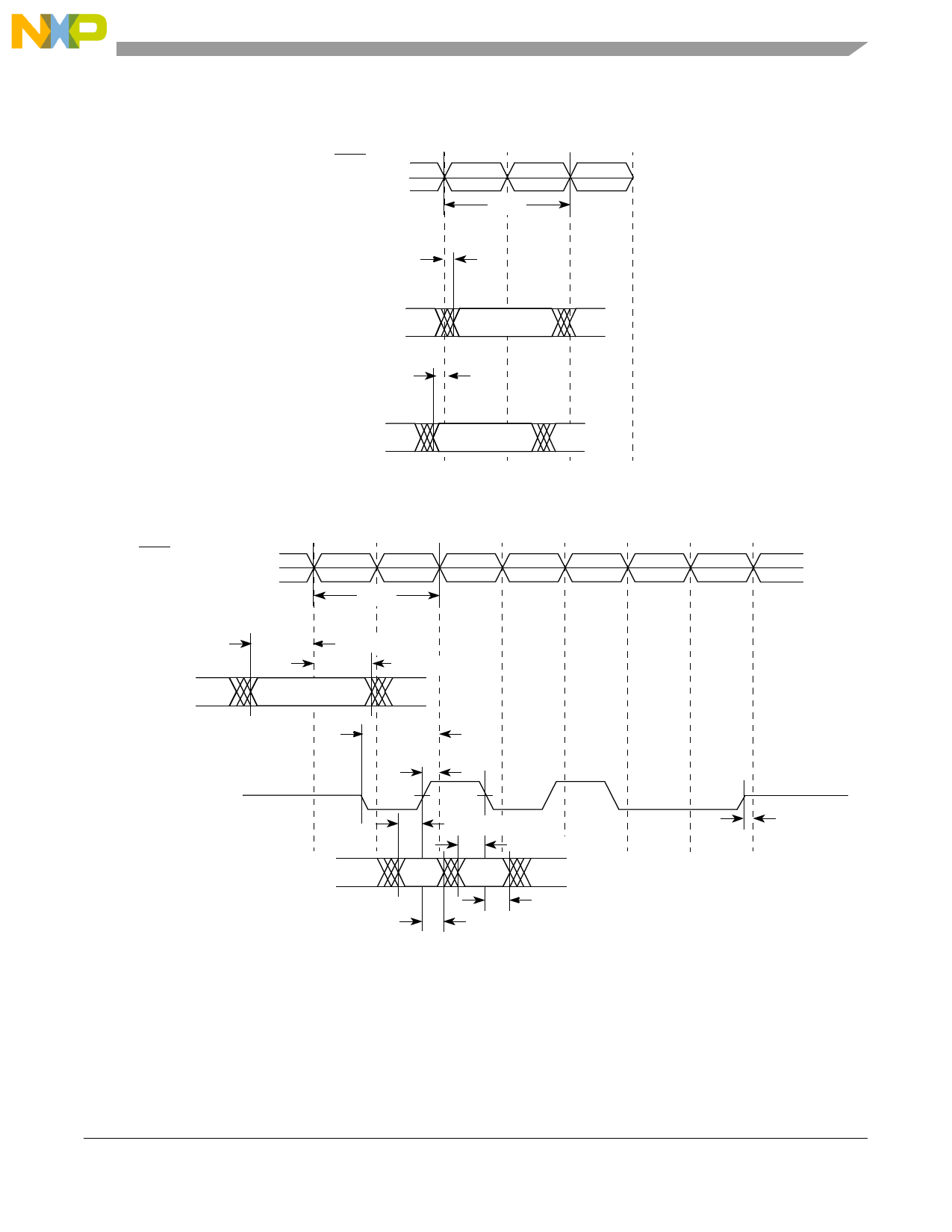

Figure 4 shows the DDR SDRAM output timing for address skew with respect to any MCK.

MCK[n]

MCK[n]

tMCK

tAOSKEWmax)

ADDR/CMD

CMD

tAOSKEW(min)

NOOP

ADDR/CMD

CMD

NOOP

Figure 4. Timing Diagram for tAOSKEW Measurement

Figure 5 shows the DDR SDRAM output timing diagram for the source synchronous mode.

MCK[n]

MCK[n]

tMCK

ADDR/CMD

tDDKHAS ,tDDKHCS

tDDKHAX ,tDDKHCX

Write A0

NOOP

tDDKHMP

tDDKHMH

MDQS[n]

tDDKHDS

tDDKLDS

MDQ[x]

D0

D1

tDDKHDX

tDDKLDX

Figure 5. DDR SDRAM Output Timing Diagram for Source Synchronous Mode

tDDKLME

MPC8541E PowerQUICC™ III Integrated Communications Processor Hardware Specification, Rev. 4.2

Freescale Semiconductor

19