S25FL256SDSBFIQ01 View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

Manufacturer

S25FL256SDSBFIQ01

S25FL256SDSBFIQ01 Datasheet PDF : 144 Pages

| |||

S25FL128S, S25FL256S

Hardware Interface

Serial Peripheral Interface with Multiple Input / Output (SPI-MIO)

Many memory devices connect to their host system with separate parallel control, address, and data signals that require a large

number of signal connections and larger package size. The large number of connections increase power consumption due to so

many signals switching and the larger package increases cost.

The S25FL128S and S25FL256S devices reduce the number of signals for connection to the host system by serially transferring all

control, address, and data information over 4 to 6 signals. This reduces the cost of the memory package, reduces signal switching

power, and either reduces the host connection count or frees host connectors for use in providing other features.

The S25FL128S and S25FL256S devices use the industry standard single bit Serial Peripheral Interface (SPI) and also supports

optional extension commands for two bit (Dual) and four bit (Quad) wide serial transfers. This multiple width interface is called SPI

Multi-I/O or SPI-MIO.

2. Signal Descriptions

2.1 Input/Output Summary

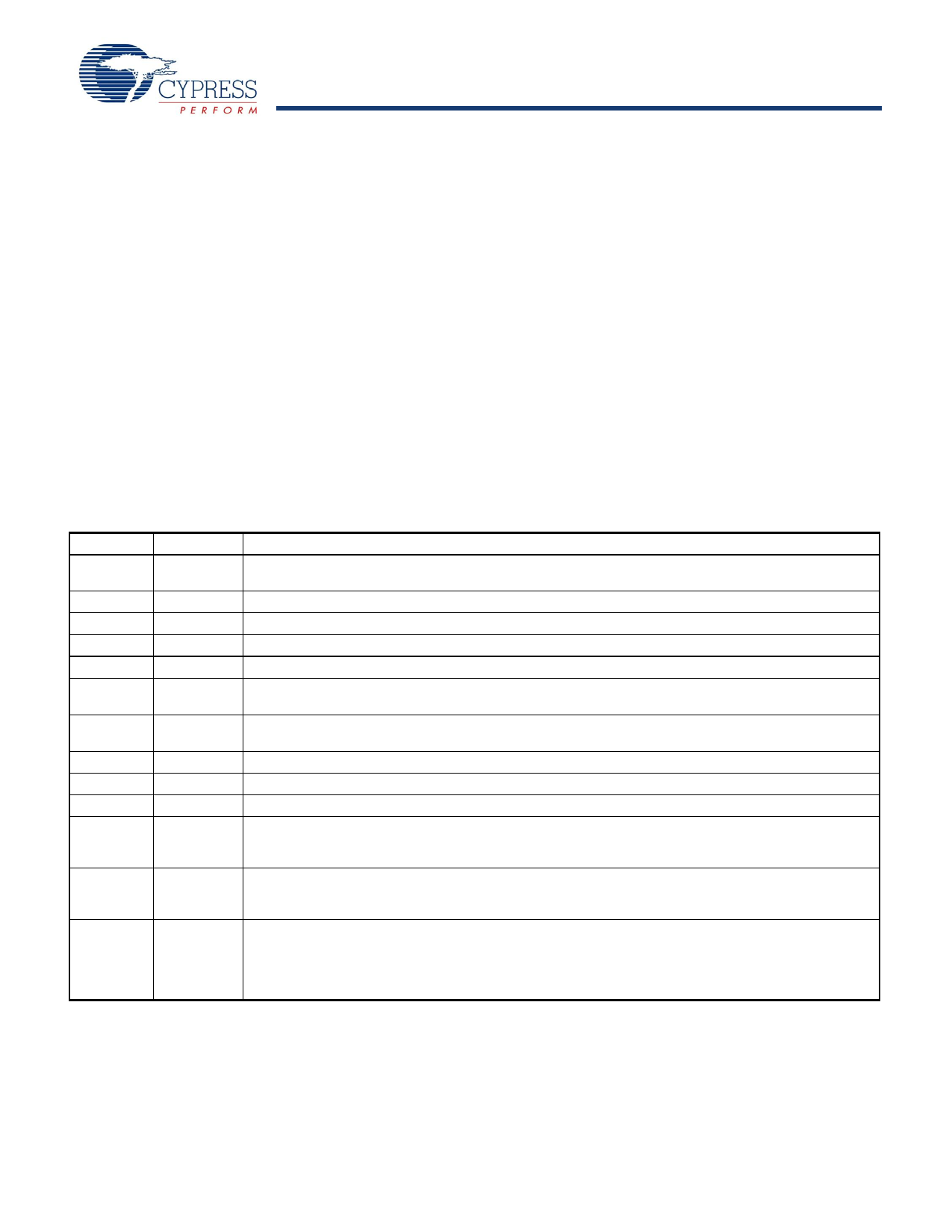

Table 2.1 Signal List

Signal Name

RESET#

SCK

CS#

SI / IO0

SO / IO1

WP# / IO2

HOLD# / IO3

VCC

VIO

VSS

NC

RFU

DNU

Type

Input

Input

Input

I/O

I/O

I/O

I/O

Supply

Supply

Supply

Unused

Reserved

Reserved

Description

Hardware Reset: Low = device resets and returns to standby state, ready to receive a command. The signal has

an internal pull-up resistor and may be left unconnected in the host system if not used.

Serial Clock

Chip Select

Serial Input for single bit data commands or IO0 for Dual or Quad commands.

Serial Output for single bit data commands. IO1 for Dual or Quad commands.

Write Protect when not in Quad mode. IO2 in Quad mode. The signal has an internal pull-up resistor and may be

left unconnected in the host system if not used for Quad commands.

Hold (pause) serial transfer in single bit or Dual data commands. IO3 in Quad-I/O mode. The signal has an internal

pull-up resistor and may be left unconnected in the host system if not used for Quad commands.

Core Power Supply.

Versatile I/O Power Supply.

Ground.

Not Connected. No device internal signal is connected to the package connector nor is there any future plan to

use the connector for a signal. The connection may safely be used for routing space for a signal on a Printed

Circuit Board (PCB). However, any signal connected to an NC must not have voltage levels higher than VIO.

Reserved for Future Use. No device internal signal is currently connected to the package connector but there is

potential future use of the connector for a signal. It is recommended to not use RFU connectors for PCB routing

channels so that the PCB may take advantage of future enhanced features in compatible footprint devices.

Do Not Use. A device internal signal may be connected to the package connector. The connection may be used by

Cypress for test or other purposes and is not intended for connection to any host system signal. Any DNU signal

related function will be inactive when the signal is at VIL. The signal has an internal pull-down resistor and may be

left unconnected in the host system or may be tied to VSS. Do not use these connections for PCB signal routing

channels. Do not connect any host system signal to this connection.

Document Number: 001-98283 Rev. *I

Page 9 of 144