LH28F008SC-L120 View Datasheet(PDF) - Sharp Electronics

Part Name

Description

Manufacturer

LH28F008SC-L120 Datasheet PDF : 55 Pages

| |||

sharp

LHF08CH1

7

2 PRINCIPLES OF OPERATION

The LH28F008SCT-L85 SmartVoltage Flash memory

includes an on-chip WSM to manage block erase,

byte write, and lock-bit configuration functions. It

allows for: 100% TTL-level control inputs, fixed power

supplies during block erasure, byte write, and lock-bit

configuration, and minimal processor overhead with

RAM-Like interface timings.

After initial device power-up or return from deep

power-down mode (see Bus Operations), the device

defaults to read array mode. Manipulation of external

memory control pins allow array read, standby, and

output disable operations.

Status register and identifier codes can be accessed

through the CUI independent of the VPP voltage. High

voltage on VPP enables successful block erasure,

byte writing, and lock-bit configuration. All functions

associated with altering memory contents‚àíblock

erase, byte write, Lock-bit configuration, status, and

identifier codes‚àíare accessed via the CUI and

verified through the status register.

Commands are written using standard

microprocessor write timings. The CUI contents serve

as input to the WSM, which controls the block erase,

byte write, and lock-bit configuration. The internal

algorithms are regulated by the WSM, including pulse

repetition, internal verification, and margining of data.

Addresses and data are internally latch during write

cycles. Writing the appropriate command outputs

array data, accesses the identifier codes, or outputs

status register data.

Interface software that initiates and polls progress of

block erase, byte write, and lock-bit configuration can

be stored in any block. This code is copied to and

executed from system RAM during flash memory

updates. After successful completion, reads are

again possible via the Read Array command. Block

erase suspend allows system software to suspend a

block erase to read or write data from any other

block. Byte write suspend allows system software to

suspend a byte write to read data from any other

flash memory array location.

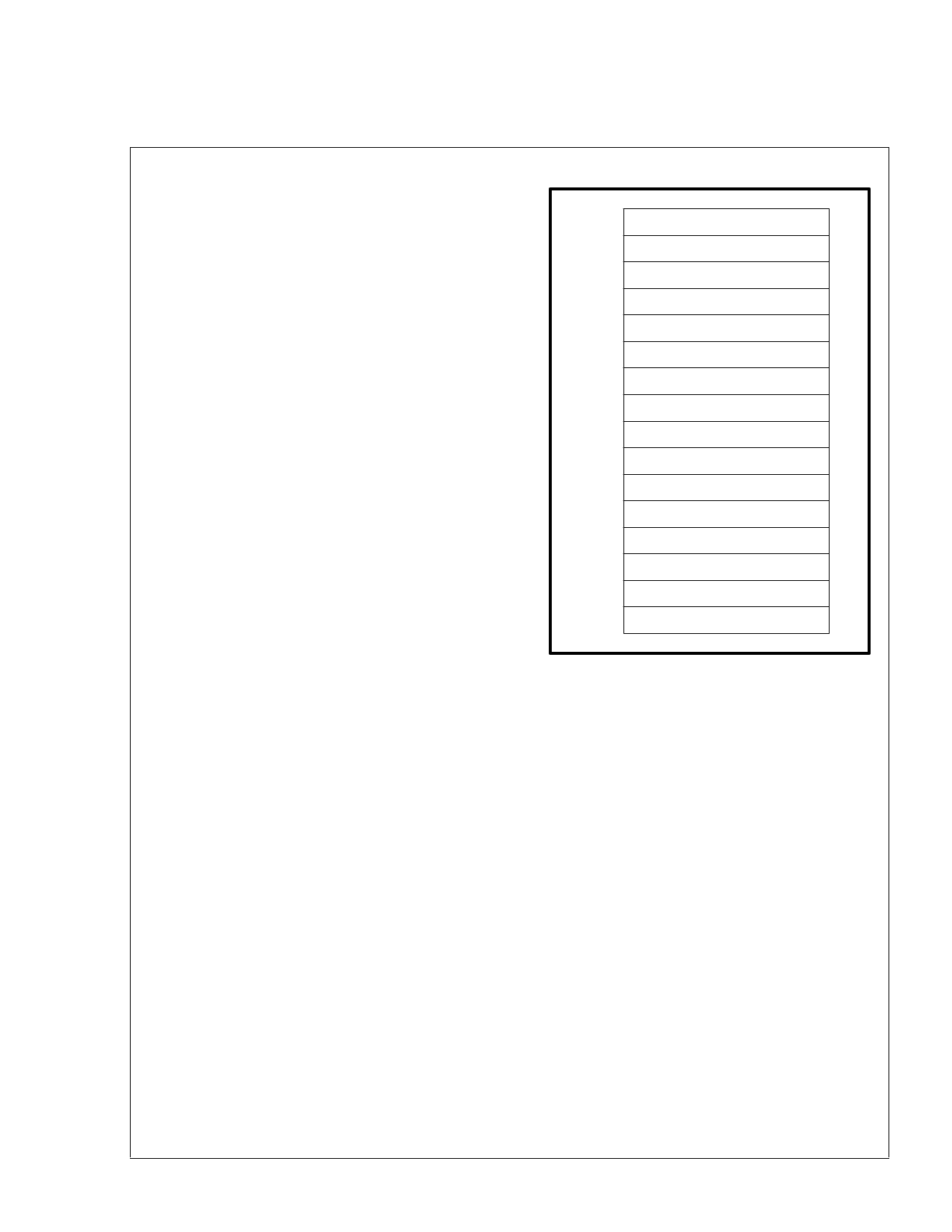

FFFFF

F0000

EFFFF

E0000

DFFFF

D0000

CFFFF

C0000

BFFFF

B0000

AFFFF

A0000

9FFFF

90000

8FFFF

80000

7FFFF

70000

6FFFF

60000

5FFFF

50000

4FFFF

40000

3FFFF

30000

2FFFF

20000

1FFFF

10000

0FFFF

00000

64K-byte Block 15

64K-byte Block 14

64K-byte Block 13

64K-byte Block 12

64K-byte Block 11

64K-byte Block 10

64K-byte Block

9

64K-byte Block

8

64K-byte Block

7

64K-byte Block

6

64K-byte Block

5

64K-byte Block

4

64K-byte Block

3

64K-byte Block

2

64K-byte Block

1

64K-byte Block

0

Figure 3. Memory Map

2.1 Data Protection

Depending on the application, the system designer

may choose to make the VPP power supply

switchable (available only when memory block

erases, byte writes, or lock-bit configurations are

required) or hardwired to VPPH1/2/3. The device

accommodates either design practice and

encourages optimization of the processor-memory

interface.

When VPP≤VPPLK, memory contents cannot be

altered. The CUI, with two-step block erase, byte

write, or lock-bit configuration command sequences,

provides protection from unwanted operations even

when high voltage is applied to VPP. All write

functions are disabled when VCC is below the write

lockout voltage VLKO or when RP# is at VIL. The

device’s block locking capability provides additional

protection from inadvertent code or data alteration by

gating erase and byte write operations.

Rev. 1.3