7C1325-100 View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

Manufacturer

7C1325-100 Datasheet PDF : 13 Pages

| |||

ADVANCED INFORMATION

CY7C1325

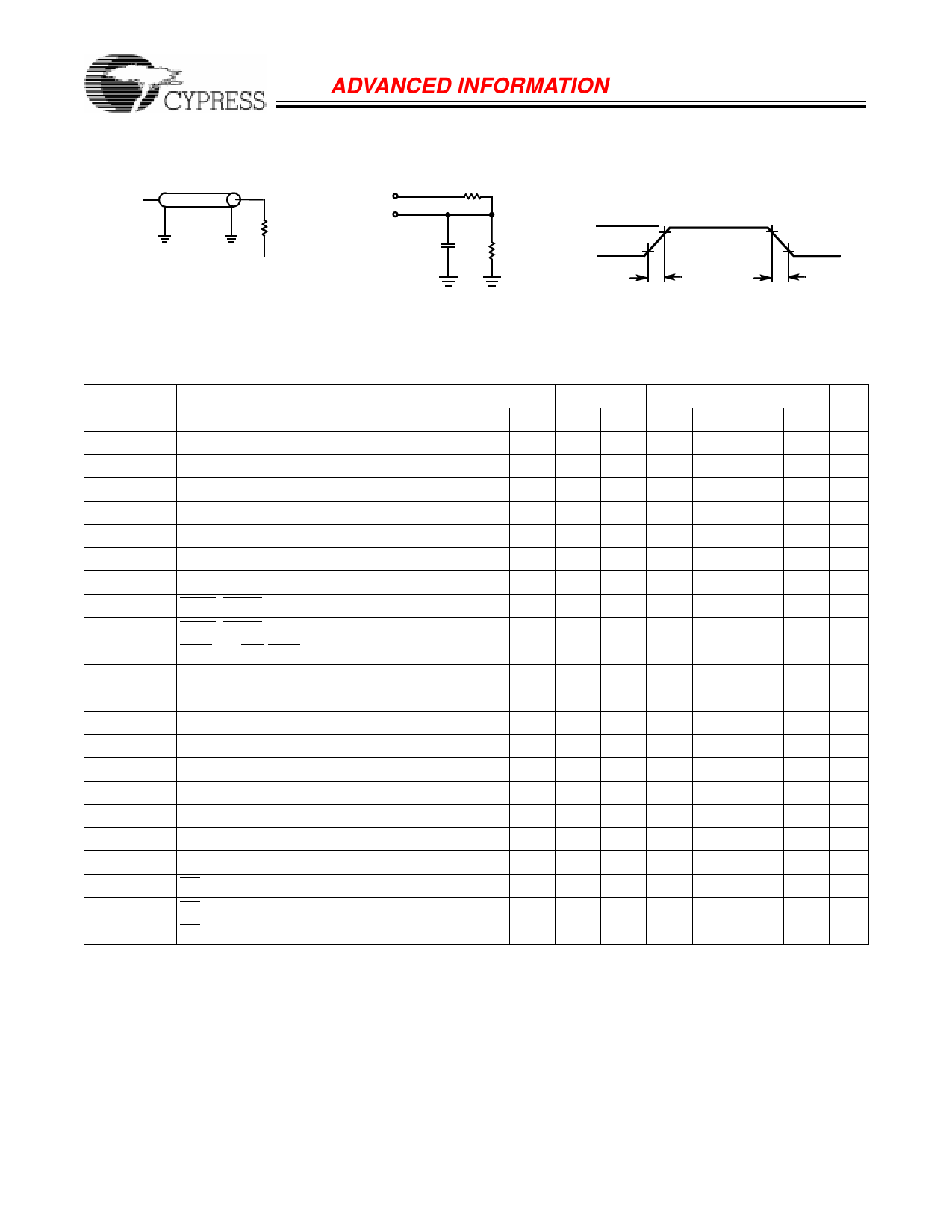

AC Test Loads and Waveforms

OUTPUT

Z0 =50 Ω

RL =50 Ω

VL =1.5V

(a)

2.5V

OUTPUT

5 pF

INCLUDING

JIGAND

SCOPE

R1

2.5V

R2

10%

GND

≤ 2.5ns

(b)[9]

1325–3

ALL INPUT PULSES

90%

90%

10%

≤ 2.5ns

1325–4

Switching Characteristics Over the Operating Range[10]

-117

-100

-90

-50

Parameter

Description

Min. Max. Min. Max. Min. Max. Min. Max. Unit

tCYC

Clock Cycle Time

8.5

10

11

20

ns

tCH

Clock HIGH

3.0

4.0

4.5

4.5

ns

tCL

Clock LOW

3.0

4.0

4.5

4.5

ns

tAS

Address Set-Up Before CLK Rise

2.0

2.0

2.0

2.0

ns

tAH

Address Hold After CLK Rise

0.5

0.5

0.5

0.5

ns

tCDV

Data Output Valid After CLK Rise

7.5

8.0

8.5

11.0 ns

tDOH

Data Output Hold After CLK Rise

2.0

2.0

2.0

2.0

ns

tADS

ADSP, ADSC Set-Up Before CLK Rise

2.0

2.0

2.0

2.0

ns

tADH

ADSP, ADSC Hold After CLK Rise

0.5

0.5

0.5

0.5

ns

tWES

BWS[1:0], GW,BWE Set-Up Before CLK Rise 2.0

2.0

2.0

2.0

ns

tWEH

BWS[1:0], GW,BWE Hold After CLK Rise

0.5

0.5

0.5

0.5

ns

tADVS

ADV Set-Up Before CLK Rise

2.0

2.0

2.0

2.0

ns

tADVH

ADV Hold After CLK Rise

0.5

0.5

0.5

0.5

ns

tDS

Data Input Set-Up Before CLK Rise

2.0

2.0

2.0

2.0

ns

tDH

Data Input Hold After CLK Rise

0.5

0.5

0.5

0.5

ns

tCES

Chip Enable Set-Up

2.0

2.0

2.0

2.0

ns

tCEH

tCHZ

tCLZ

tEOHZ

tEOLZ

Chip Enable Hold After CLK Rise

Clock to High-Z[11,12]

Clock to Low-Z[11,12]

OE HIGH to Output High-Z[11,13]

OE LOW to Output Low-Z[11,13]

0.5

0.5

0.5

0.5

ns

3.5

3.5

3.5

3.5 ns

0

0

0

0

ns

3.5

3.5

3.5

3.5 ns

0

0

0

0

ns

tEOV

OE LOW to Output Valid

3.5

3.5

3.5

3.5 ns

Notes:

9. R1=1667Ω and R2=1538Ω for IOH/IOL=–4/8mA, R1=521Ω and R2=481Ω for IOH/IOL=–2/2mA.

10. Unless otherwise noted, test conditions assume signal transition time of 2.5ns or less, timing reference levels of 1.25V, input pulse levels of 0 to 2.5V, and output

loading of the specified IOL/IOH and load capacitance. Shown in (a) and (b) of AC test loads.

11. tCHZ, tCLZ, tEOHZ, and tEOLZ are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured ± 200 mV from steady-state voltage.

12. At any given voltage and temperature, tCHZ (max) is less than tCLZ (min).

13. This parameter is sampled and not 100% tested.

9