AN17831A View Datasheet(PDF) - Unspecified

Part Name

Description

Manufacturer

AN17831A Datasheet PDF : 9 Pages

| |||

Prepared

Checked

Approved

Product Specifications

AN17831A

Ref No.

F-1

Total Page

9

Page No.

6

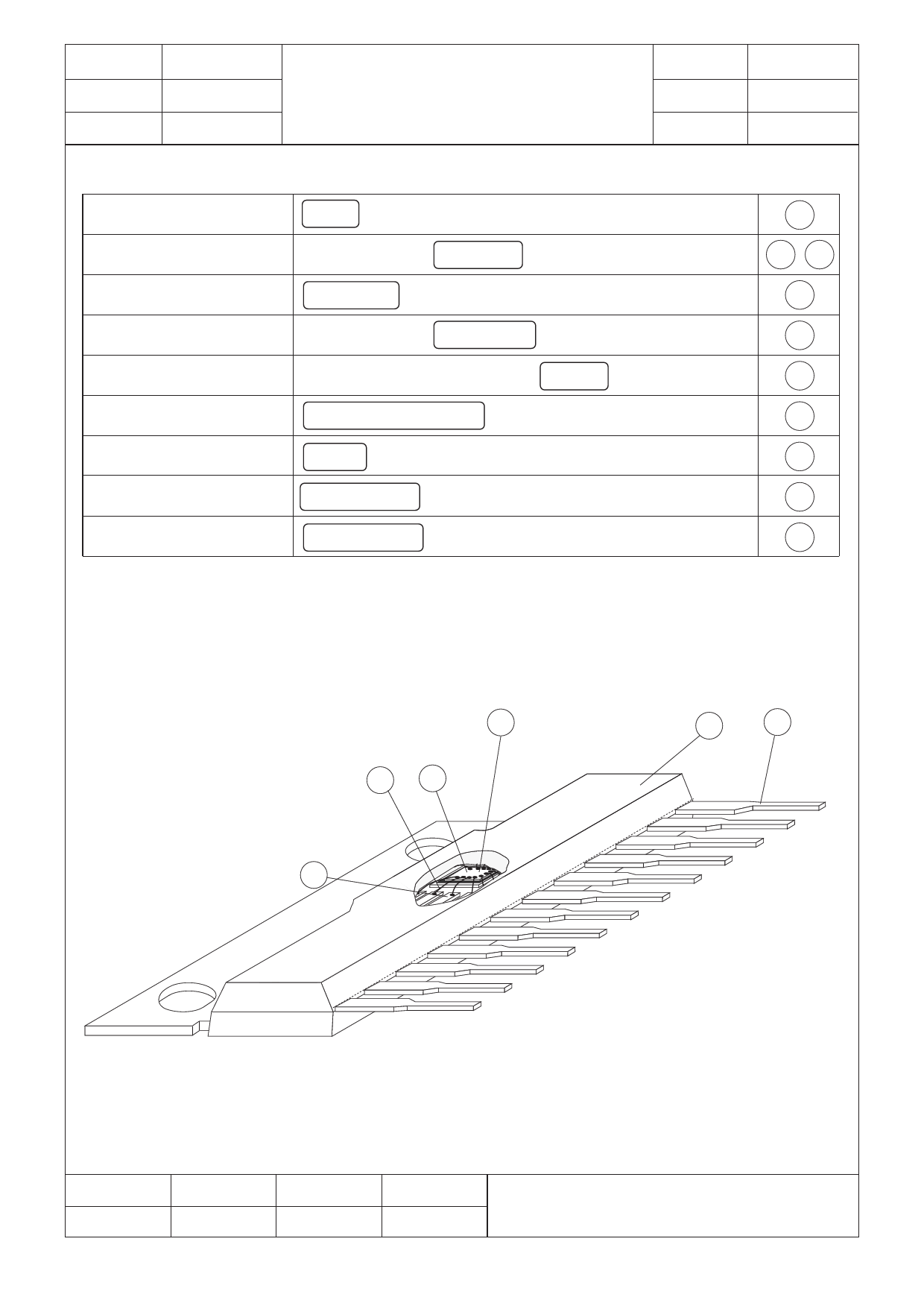

(Structure Description)

Chip surface passivation SiN,

PSG,

Others (

Lead frame material

Fe group,

Cu group,

Others (

Inner lead surface process Ag plating, Au plating,

Others (

Outer lead surface process Solder plating, Solder dip,

Others (

Chip mounting method Ag paste,

Au-Si alloy, Solder, Others (

Wire bonding method Thermalsonic bonding,

Others (

Mold material

Epoxy,

Others (

Molding method

Transfer mold, Multiplunger mold, Others (

Fin material

Cu Group

Others (

)1

) 2, 6

)2

)6

)3

)4

)4

)5

)5

Package FP-12S

1

43

2

5

6

Eff. Date Eff. Date

18-FEB-2002

FMSC-PSDA-002-01 Rev.1

Eff. Date Eff. Date

Semiconductor Company, Matsushita Electric Industrial Co., Ltd.