PA7572 View Datasheet(PDF) - International Cmos Technology

Part Name

Description

Manufacturer

PA7572 Datasheet PDF : 10 Pages

| |||

Commercial/Industrial

PA7572 PEEL Array™

Programmable Electrically Erasable Logic Array

Versatile Logic Array Architecture

- 24 I/Os, 14 inputs, 60 registers/latches

- Up to 72 logic cell output functions

- PLA structure with true product-term sharing

- Logic functions and registers can be I/O-buried

High-Speed Commercial and Industrial Versions

- As fast as 13ns/20ns (tpdi/tpdx), 66.6MHz (fMAX)

- Industrial grade available for 4.5 to 5.5V VCC and -40

to +85 °C temperatures

Ideal for Combinatorial, Synchronous and

Asynchronous Logic Applications

- Integration of multiple PLDs and random logic

- Buried counters, complex state-machines

- Comparators, decoders, other wide-gate functions

CMOS Electrically Erasable Technology

- Reprogrammable in 40-pin DIP,

44-pin PLCC and TQFP packages

Flexible Logic Cell

- Up to 3 output functions per logic cell

- D,T and JK registers with special features

- Independent or global clocks, resets, presets,

clock polarity and output enables

- Sum-of-products logic for output enables

Development and Programmer Support

- ICT PLACE Development Software

- Fitters for ABEL, CUPL and other software

- Programming support by popular third-party

programmers

General Description

The PA7572 is a member of the Programmable Electrically

Erasable Logic (PEEL™) Array family based on ICT’s

CMOS EEPROM technology. PEEL™ Arrays free

designers from the limitations of ordinary PLDs by

providing the architectural flexibility and speed needed for

today’s programmable logic designs. The PA7572 offers a

versatile logic array architecture with 24 I/O pins, 14 input

pins and 60 registers/latches (24 buried logic cells, 12 input

registers/latches, 24 buried I/O registers/latches). Its logic

array implements 100 sum-of-products logic functions

divided into two groups each serving 12 logic cells. Each

group shares half (60) of the 120 product-terms available.

The PA7572’s logic and I/O cells (LCCs, IOCs) are

extremely flexible with up to three output functions per cell

(a total of 72 for all 24 logic cells). Cells are configurable as

D, T, and JK registers with independent or global clocks,

resets, presets, clock polarity, and other features, making

the PA7572 suitable for a variety of combinatorial,

synchronous and asynchronous logic applications. The

PA7572 supports speeds as fast as 13ns/20ns (tpdi/tpdx)

and 66.6MHz (fMAX) at moderate power consumption

140mA (100mA typical). Packaging includes 40-pin DIP

and 44-pin PLCC (see Figure 1). ICT and popular third-

party development tool manufacturers provide

development and programming support for the PA7572.

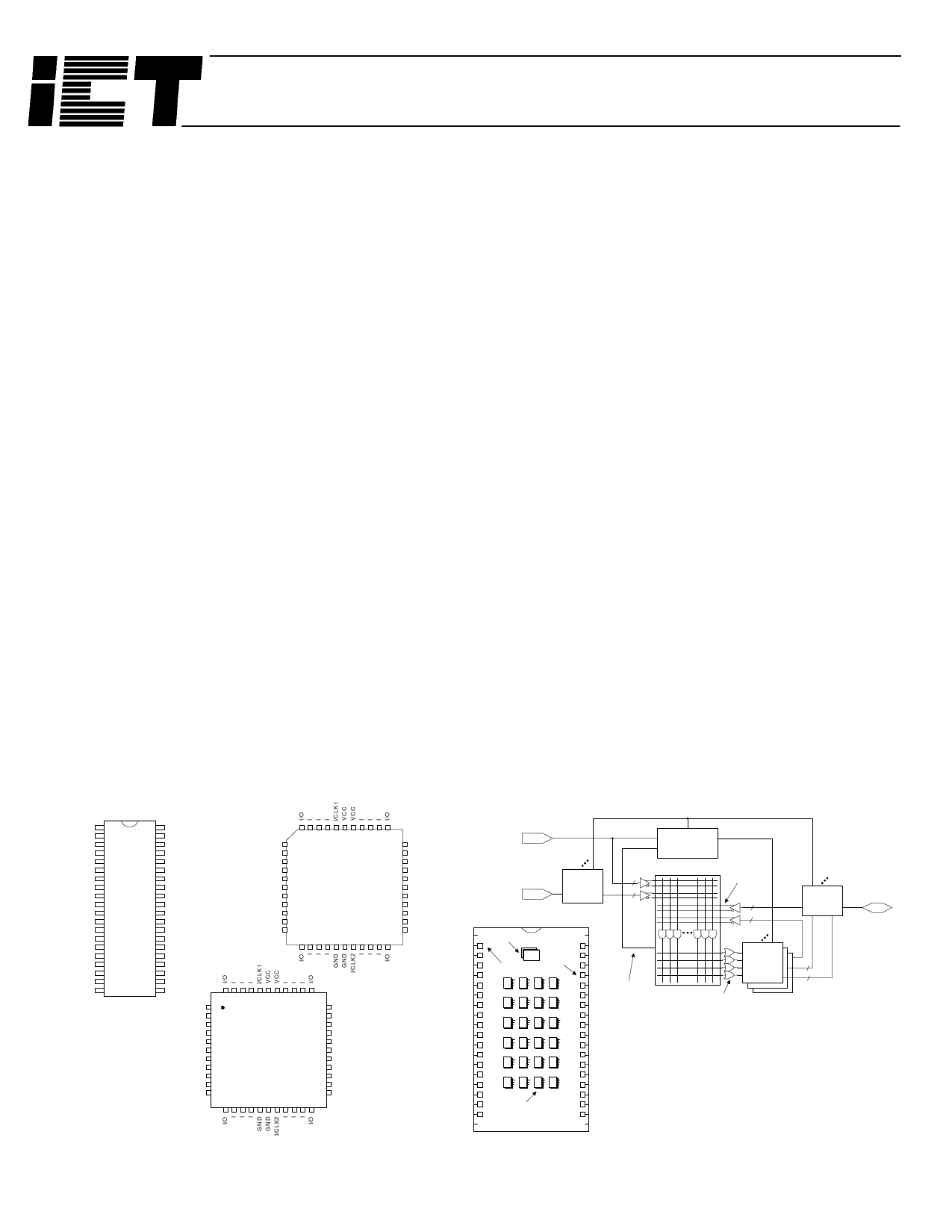

Figure 1. Pin Configuration

Figure 2. Block Diagram

DIP (600 m il)

I/C LK1

1

40

I

2

39

I

3

38

I

4

37

I/O

5

36

I/O

6

35

I/O

7

34

I/O

8

33

I/O

9

32

I/O

10

31

I/O

11

30

I/O

12

29

I/O

13

28

I/O

14

27

I/O

15

26

I/O

16

25

I

17

24

I

18

23

I

19

22

GND

20

21

VCC

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I/C LK2

TQFP

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

PLCC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

6 5 4 3 2 1 44 43 42 41 40

7

39

8

38

9

37

10

36

11

35

12

34

13

33

14

32

15

31

16

30

17

29

18 19 20 21 22 23 24 25 26 27 28

44 43 42 41 403938 37 3635 34

1

33

2

32

3

31

4

30

5

29

6

28

7

27

8

26

9

25

10

24

11

23

12 13 14 151617 18 19 20 21 22

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

08-15 -0 01A

I/C L K

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

GND

2 Input/

G lobal Clock Pins

In p u t

2

12 Input Pins C ells

(IN C )

12

G lobal

C e lls

124 (62X2)

Array Inputs

true and

com plem ent

24

I/O

C e lls

(IO C )

24 I/O Pins

Global C ells

Input C ells

I/O Cells

Logic C ontrol Cells

PA7572

VCC

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I/C L K 2

Logic

Array

24

Buried

logic

Logic

A

B

C o n tro l

24

C

C e lls

D

(LCC)

Logic

func tions

to I/O cells

4 sum term s

5 product term s

for G lobal Cells

96 sum term s

(four per LCC)

24

24 Logic Control Cells

up to 3 output functions per cell

(72 total output functions

possible)

08-15-002A

1

04-02-050A