FX365C View Datasheet(PDF) - CML Microsystems Plc

Part Name

Description

Manufacturer

FX365C Datasheet PDF : 9 Pages

| |||

Specification ......

Characteristics

See Note

Min.

Typ.

Max.

Unit

Serial/Parallel Inputs

Parallel Set-Up Time (tSP)

Load/Latch Pulse Width (tL)

Serial Clock Pulse Width (tC)

Serial Set-Up Time (tSS)

Serial Enable Time (t1)

Serial Load/Latch Set-Up Time (t2)

Serial Clock Frequency

400

-

400

-

400

-

400

-

400

-

400

-

-

1.0

-

ns

-

ns

-

ns

-

ns

-

ns

-

ns

-

MHz

Notes

1.

2.

3.

4.

5.

6.

7.

8.

Refers to Rx/Tx, PTL, Decode Comparator Input, D0, D1, D2, D3, D4, D5 inputs.

All logic outputs.

Composite Signal test condition.

Any programme tone and RL = 600Ω. CL = 15pF. Includes response to a phase-reversal instruction.

1kHz reference = 0dB.

fO > 100Hz, (for 100Hz >fO >67Hz: t = (100/fO Hz) x 250ms).

Measured in a 30kHz bandwidth.

For an input level of 180mVrms at 1.0kHz, in a 30kHz measurement bandwidth.

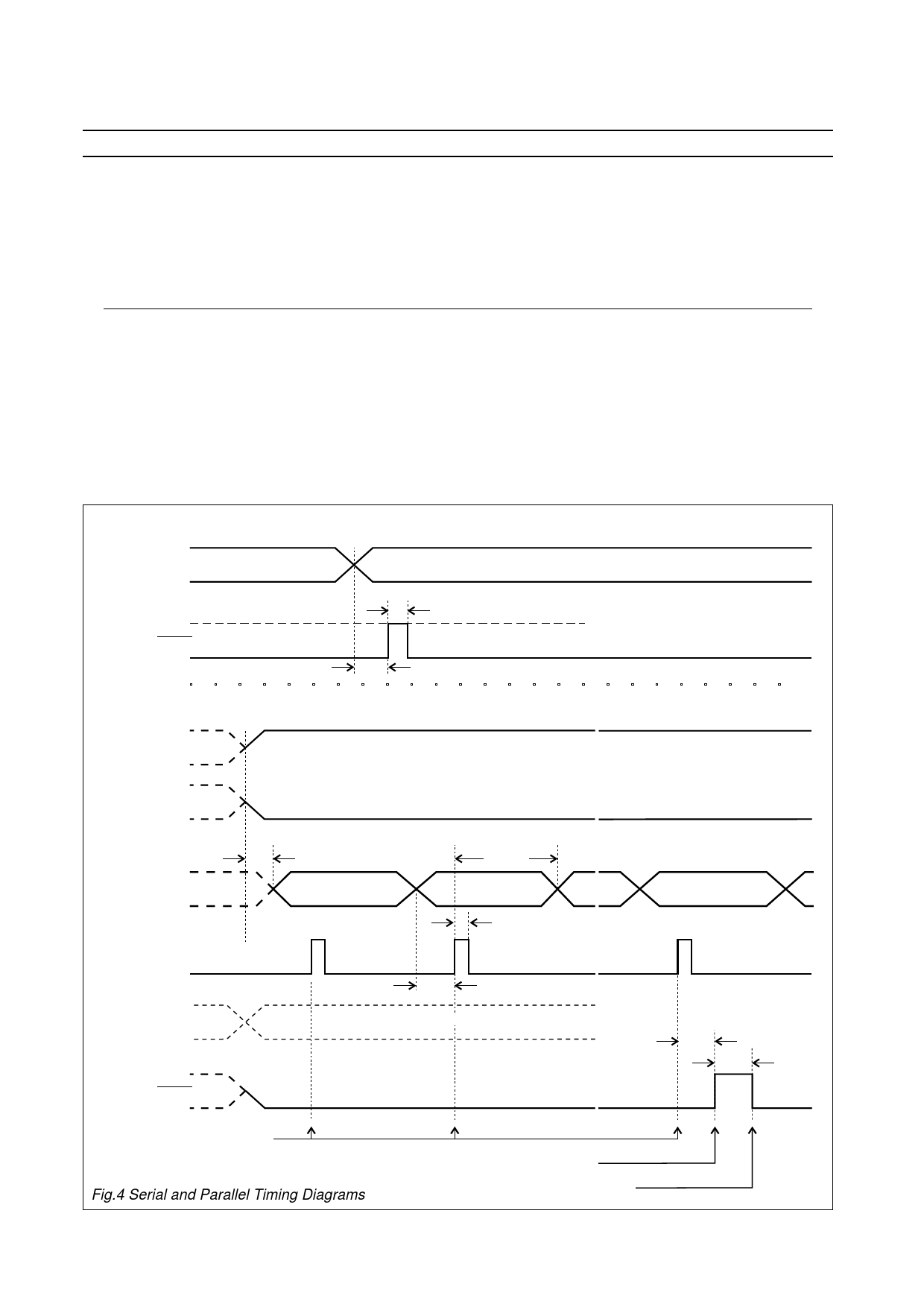

(a) Parallel Mode Timing

D0 to D5, Rx/Tx and PTL

LOAD/LATCH

tL

tSP

For wired, non-µP applications,

Load/Latch should be connected to VDD.

(b) Serial Mode Timing

D5

SERIAL

ENABLE

FUNCTION

D4

SERIAL

DATA

D3

SERIAL

CLOCK

D2

D1 and D0

LOAD/LATCH

Data load sequence: D5, D4, D3, D2, D1, D0, Rx/Tx and PTL/Phase Reverse

t1

tW

DATA D5

DATA D4

D 3 Rx/Tx

(Rx) PTL or

(Tx) Phase Reverse

tC

tSS

NOT USED 1.0MΩ INTERNAL PULLUP

t2

tL

LOAD DATA

Fig.4 Serial and Parallel Timing Diagrams

LATCH DATA

DATA LATCHED

7