ISPLSI1016E-100LT44 View Datasheet(PDF) - Lattice Semiconductor

Part Name

Description

Manufacturer

ISPLSI1016E-100LT44 Datasheet PDF : 13 Pages

| |||

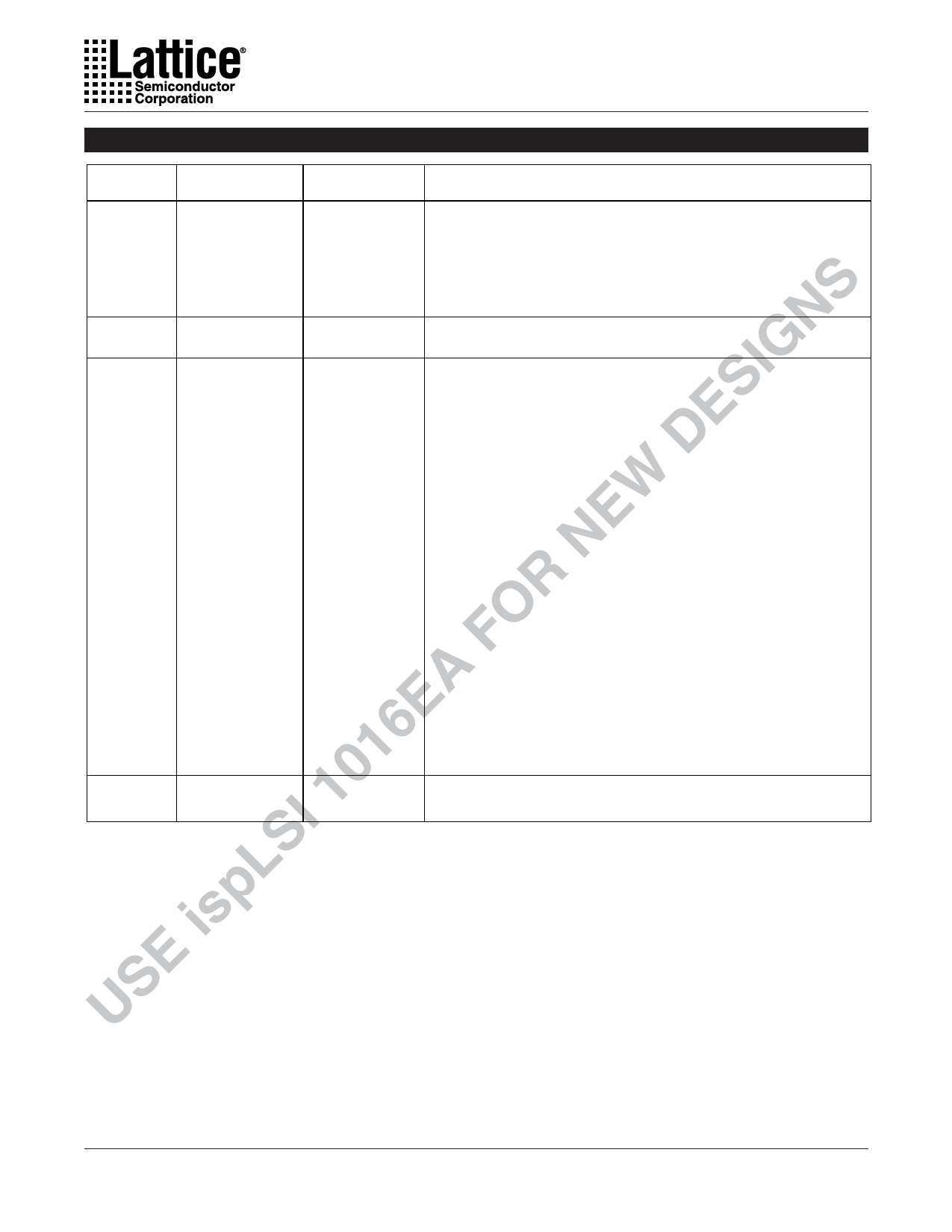

Specifications ispLSI 1016E

Pin Description

NAME

PLCC

PIN NUMBERS

TQFP

PIN NUMBERS

DESCRIPTION

I/O 0 - I/O 3

15, 16, 17, 18,

9, 10, 11, 12, Input/Output Pins - These are the general purpose I/O pins used by the logic

I/O 4 - I/O 7

19, 20, 21, 22, 13, 14, 15, 16, array.

I/O 8 - I/O 11 25, 26, 27, 28, 19, 20, 21, 22,

I/O 12 - I/O 15 29, 30, 31, 32, 23, 24, 25, 26,

I/O 16 - I/O 19

I/O 20 - I/O 23

I/O 24 - I/O 27

I/O 28 - I/O 31

GOE 0/IN 32

37, 38, 39, 40,

41, 42, 43, 44,

3, 4, 5, 6,

7, 8, 9, 10

2

ispEN

13

SDI/IN 01

14

31, 32, 33, 34,

35, 36, 37, 38,

41, 42, 43, 44,

1, 2, 3, 4

40

7

8

NS This is a dual function pin. It can be used either as Global Output Enable for

all I/O cells or it can be used as a dedicated input pin.

IG Input - Dedicated in-system programming enable input pin. This pin is

brought low to enable the programming mode. The MODE, SDI, SDO and

S SCLK controls become active.

Input - This pin performs two functions. When ispEN is logic low, it functions

E as an input pin to load programming data into the device. It is a dedicated

D input pin when ispEN is logic high.SDI/IN0 also is used as one of the two

control pins for the isp state machine.

MODE/IN 21

36

SDO/IN 11

24

30

18

Input - This pin performs two functions. When ispEN is logic low, it functions

as a pin to control the operation of the isp state machine. It is a dedicated

W input pin when ispEN is logic high.

Output/Input - This pin performs two functions. When ispEN is logic low, it

E functions as an output pin to read serial shift register data. It is a dedicated

N input pin when ispEN is logic high.

SCLK/Y21

33

Y0

11

27

5

Input - This pin performs two functions. When ispEN is logic low, it

functions as a clock pin for the Serial Shift Register. It is a dedicated clock

R input when ispEN is logic high. This clock input is brought into the Clock

Distribution Network, and can optionally be routed to any GLB and/or I/O

O cell on the device.

F Dedicated Clock input. This clock input is connected to one of the clock

6EA Y1/RESET

35

inputs of all the GLBs on the device.

29

This pin performs two functions:

- Dedicated clock input. This clock input is brought into the Clock

Distribution Network, and can optionally be routed to any GLB and/or

I/O cell on the device.

- Active Low (0) Reset pin which resets all of the GLB and I/O registers

in the device.

01 GND

1 VCC

1, 23

12, 34

17, 39

6, 28

Ground (GND)

Vcc

I 1. Pins have dual function capability.

ispLS 2. Pins have dual function capability which is software selectable.

Table 2-0002C-16-isp

USE

10