ADSP-21160M(Rev0) View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

ADSP-21160M Datasheet PDF : 52 Pages

| |||

ADSP-21160M

,QWHUQDO

0HPRU\

6SDFH

,23 5HJ¶V

/RQJ :RUG

1RUPDO :RUG

[

[

[

[

6KRUW :RUG

,QWHUQDO

0HPRU\

6SDFH

,'

[

,QWHUQDO

0HPRU\

6SDFH

,'

[

,QWHUQDO

0HPRU\

6SDFH

,'

0XOWLSURFHVVRU

0HPRU\

6SDFH

,QWHUQDO

0HPRU\

6SDFH

,'

,QWHUQDO

0HPRU\

6SDFH

,'

,QWHUQDO

0HPRU\

6SDFH

,'

[

[

[

[

%URDGFDVW

:ULWH WR

$OO '63V

,'

[

[) ))))

%DQN

[

06

%DQN

06

%DQN

06

%DQN

06

([WHUQDO

0HPRU\

6SDFH

1RQEDQNHG

[)))) ))))

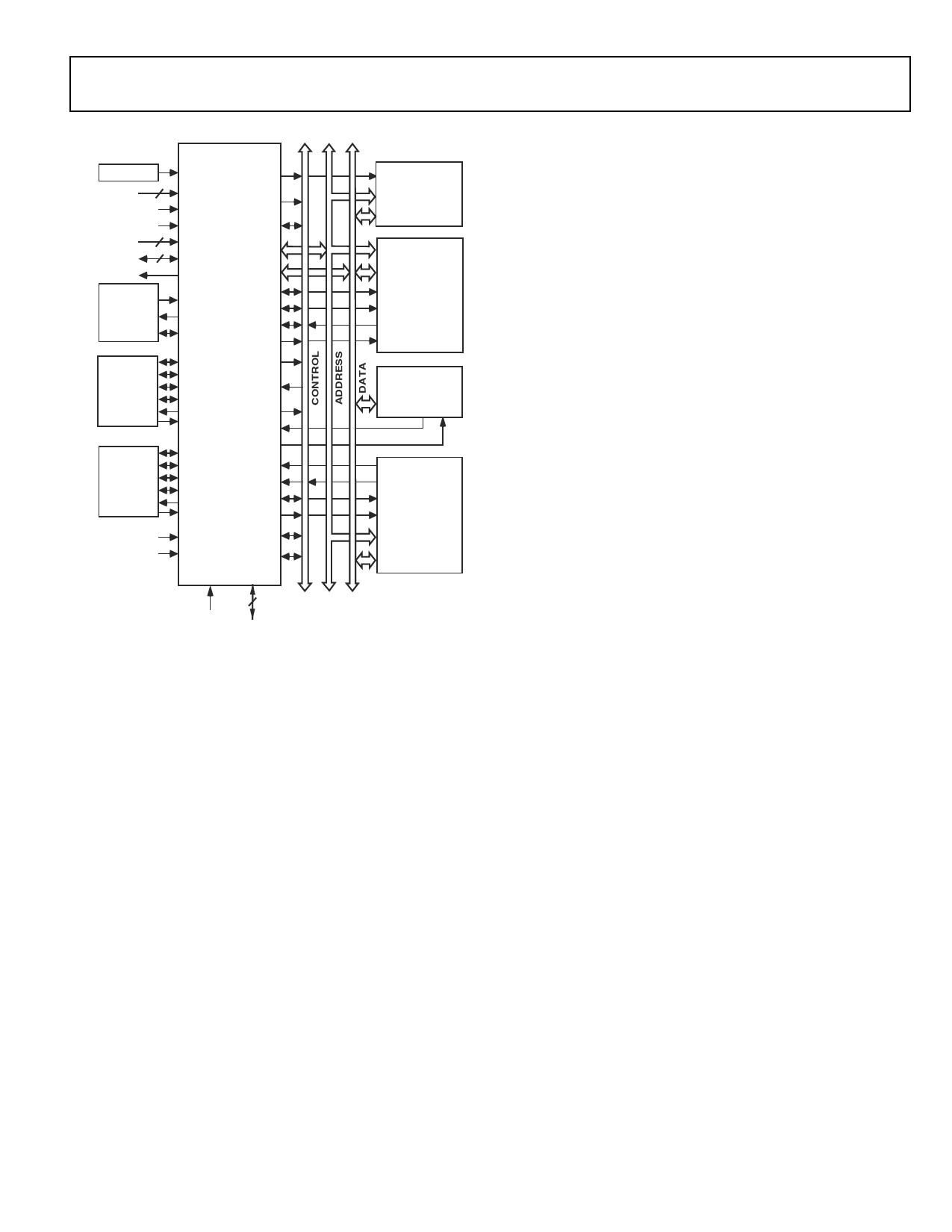

Figure 2. ADSP-21160M Memory Map

host processor, other ADSP-21160Ms, memory or I/O

transfers). Programs can be downloaded to the

ADSP-21160M using DMA transfers. Asynchronous

off-chip peripherals can control two DMA channels using

DMA Request/Grant lines (DMAR1–2, DMAG1–2).

Other DMA features include interrupt generation upon

completion of DMA transfers, two-dimensional DMA, and

DMA chaining for automatic linked DMA transfers.

Multiprocessing

The ADSP-21160M offers powerful features tailored to

multiprocessing DSP systems as shown in Figure 4. The

external port and link ports provide integrated glueless mul-

tiprocessing support.

The external port supports a unified address space (see

Figure 2) that allows direct interprocessor accesses of each

ADSP-21160M’s internal memory. Distributed bus arbitra-

tion logic is included on-chip for simple, glueless connection

of systems containing up to six ADSP-21160Ms and a host

processor. Master processor changeover incurs only one

cycle of overhead. Bus arbitration is selectable as either fixed

%<7(

'$7$±

5'+:5+

5'/:5/

%,7 /21* :25' 6,0' '0$ ,23 5(*,67(5 75$16)(56

%<7(

%,7 75$16)(5 )25 %,7 ,16758&7,21 )(7&+

%,7 75$16)(5 )25 %,7 (;7(1'(' 35(&,6,21

%,7 1250$/ :25' (9(1 $''5(66

%,7 1250$/ :25' 2'' $''5(66

5(675,&7(' '0$ +267 (3520 '$7$ $/,*10(176

%,7 3$&.('

%,7 3$&.('

(3520

Figure 3. ADSP-21160M External Data Alignment Options

or rotating priority. Bus lock allows indivisible read-mod-

ify-write sequences for semaphores. A vector interrupt is

provided for interprocessor commands. Maximum

throughput for interprocessor data transfer is 320M bytes/s

over the external port. Broadcast writes allow simultaneous

transmission of data to all ADSP-21160Ms and can be used

to implement reflective semaphores.

Six link ports provide for a second method of multiprocess-

ing communications. Each link port can support

communications to another ADSP-21160M. Using the

links, a large multiprocessor system can be constructed in a

2D or 3D fashion. Systems can use the link ports and cluster

multiprocessing concurrently or independently.

Link Ports

The ADSP-21160M features six 8-bit link ports that

provide additional I/O capabilities. With the capability of

running at 80 MHz rates, each link port can support 80M

bytes/s. Link port I/O is especially useful for point-to-point

interprocessor communication in multiprocessing systems.

The link ports can operate independently and simulta-

neously. Link port data is packed into 48- or 32-bit words,

and can be directly read by the core processor or

DMA-transferred to on-chip memory. Each link port has its

own double-buffered input and output registers.

Clock/acknowledge handshaking controls link port trans-

fers. Transfers are programmable as either transmit

or receive. For data throughput information, see link port

timing details in Table 18 on page 34.

Serial Ports

The ADSP-21160M features two synchronous serial ports

that provide an inexpensive interface to a wide variety of

digital and mixed-signal peripheral devices. The serial ports

can operate up to half the clock rate of the core, providing

each with a maximum data rate of 40M bit/s. Independent

REV. 0

–5–