ADSP-21160M(Rev0) View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

ADSP-21160M Datasheet PDF : 52 Pages

| |||

ADSP-21160M

9'',17

⍀

␮)

␮)

$9''

$*1'

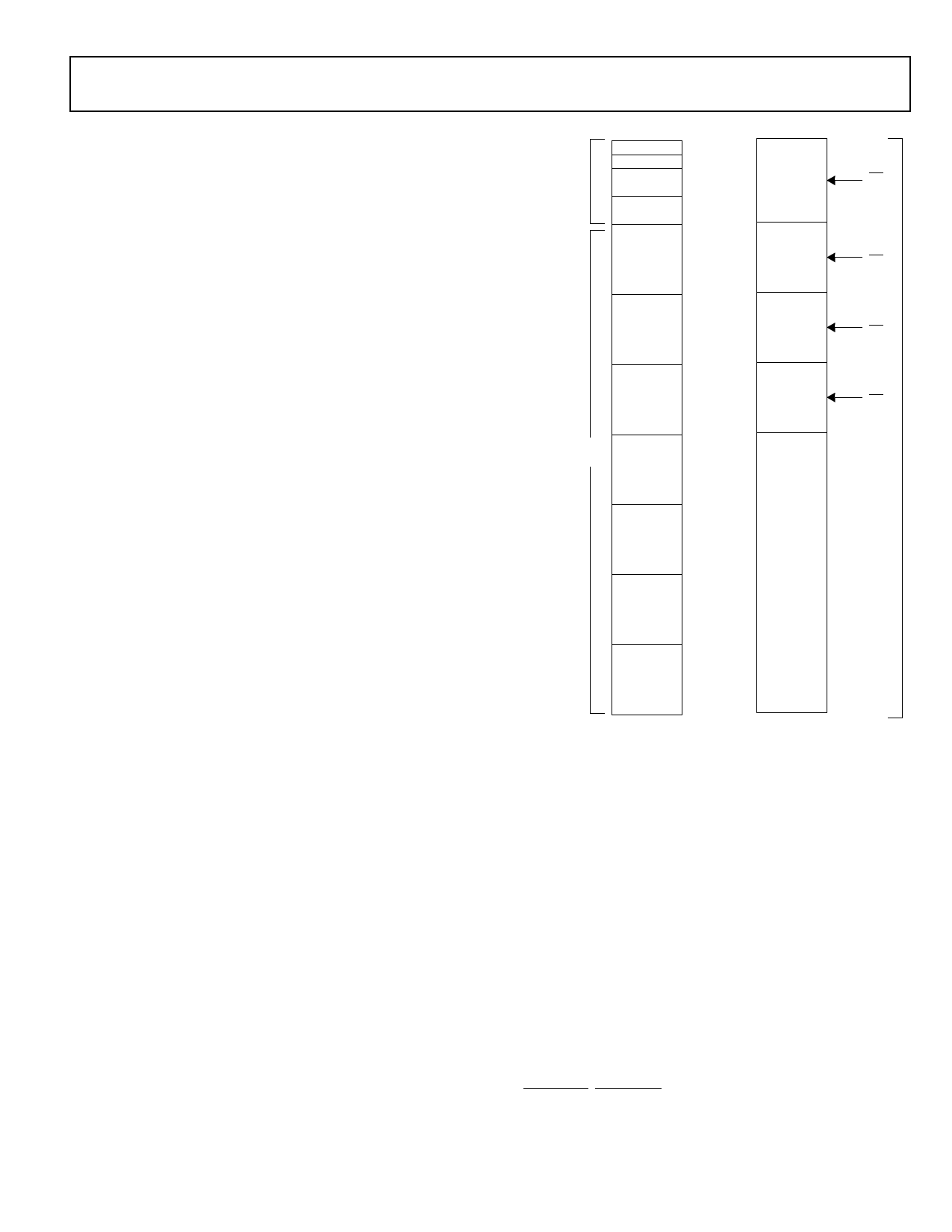

Figure 5. Analog Power (AVDD) Filter Circuit

Development Tools

The ADSP-21160M is supported with a complete set of

software and hardware development tools, including Analog

Devices’ emulators and VisualDSP++1 development envi-

ronment. The same emulator hardware that supports other

ADSP-2116x DSPs, also fully emulates the

ADSP-21160M.

The VisualDSP++ project management environment lets

programmers develop and debug an application. This envi-

ronment includes an easy-to-use assembler that is based on

an algebraic syntax; an archiver (librarian/library builder),

a linker, a loader, a cycle-accurate instruction-level simula-

tor, a C/C++ compiler, and a C/C++ run-time library that

includes DSP and mathematical functions. Two key points

for these tools are:

• Compiled ADSP-2116x C/C++ code efficiency—the

compiler has been developed for efficient translation of

C/C++ code to ADSP-2116x assembly. The DSP has

architectural features that improve the efficiency of

compiled C/C++ code.

• ADSP-2106x family code compatibility—The assembler

has legacy features to ease the conversion of existing

ADSP-2106x applications to the ADSP-2116x.

Debugging both C/C++ and assembly programs with the

VisualDSP++ debugger, programmers can:

• View mixed C/C++ and assembly code (interleaved

source and object information)

• Insert break points

• Set conditional breakpoints on registers, memory, and

stacks

• Trace instruction execution

• Perform linear or statistical profiling of program

execution

• Fill, dump, and graphically plot the contents of memory

• Source level debugging

• Create custom debugger windows

The VisualDSP++ IDE lets programmers define and

manage DSP software development. Its dialog boxes and

property pages let programmers configure and manage all

of the ADSP-2116x development tools, including the syntax

highlighting in the VisualDSP++ editor. This capability

permits:

• Control how the development tools process inputs and

generate outputs.

• Maintain a one-to-one correspondence with the tool’s

command line switches.

Analog Devices’ DSP emulators use the IEEE 1149.1 JTAG

test access port of the ADSP-21160M processor to monitor

and control the target board processor during emulation.

The emulator provides full-speed emulation, allowing

inspection and modification of memory, registers, and

processor stacks. Nonintrusive in-circuit emulation is

assured by the use of the processor’s JTAG interface—the

emulator does not affect target system loading or timing.

In addition to the software and hardware development tools

available from Analog Devices, third parties provide a wide

range of tools supporting the ADSP-2116x processor

family. Hardware tools include ADSP-2116x PC plug-in

cards. Third Party software tools include DSP libraries,

real-time operating systems, and block diagram

design tools.

Designing an Emulator-Compatible DSP Board

(Target)

The White Mountain DSP (Product Line of Analog

Devices, Inc.) family of emulators are tools that every DSP

developer needs to test and debug hardware and software

systems. Analog Devices has supplied an IEEE 1149.1

JTAG Test Access Port (TAP) on each JTAG DSP. The

emulator uses the TAP to access the internal features of the

DSP, allowing the developer to load code, set breakpoints,

observe variables, observe memory, and examine registers.

The DSP must be halted to send data and commands, but

once an operation has been completed by the emulator, the

DSP system is set running at full speed with no impact on

system timing.

To use these emulators, the target’s design must include the

interface between an Analog Devices’ JTAG DSP and the

emulation header on a custom DSP target board.

Target Board Header

The emulator interface to an Analog Devices’ JTAG DSP

is a 14-pin header, as shown in Figure 6. The customer must

supply this header on the target board in order to commu-

nicate with the emulator. The interface consists of a

standard dual row 0.025" square post header, set on

0.1" ÿã 0.1" spacing, with a minimum post length of 0.235".

Pin 3 is the key position used to prevent the pod from being

inserted backwards. This pin must be clipped on the

target board.

1VisualDSP++ is a registered trademark of Analog Devices, Inc.

REV. 0

–7–