ADSP-21160NCBZ-100(RevD) View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

ADSP-21160NCBZ-100 Datasheet PDF : 58 Pages

| |||

MEMORY AND I/O INTERFACE FEATURES

Augmenting the ADSP-2116x family core, the ADSP-21160x

adds the following architectural features.

Dual-Ported On-Chip Memory

The ADSP-21160x contains four megabits of on-chip SRAM,

organized as two blocks of 2M bits each, which can be config-

ured for different combinations of code and data storage

(Figure 4). Each memory block is dual-ported for single-cycle,

independent accesses by the core processor and I/O processor.

The dual-ported memory in combination with three separate

on-chip buses allows two data transfers from the core and one

from I/O processor, in a single cycle. The ADSP-21160x mem-

ory can be configured as a maximum of 128K words of

32-bit data, 256K words of 16-bit data, 85K words of 48-bit

instructions (or 40-bit data), or combinations of different word

sizes up to four megabits. All of the memory can be accessed as

16-, 32-, 48-, or 64-bit words. A 16-bit floating-point storage

format is supported that effectively doubles the amount of data

that may be stored on-chip. Conversion between the 32-bit

floating-point and 16-bit floating-point formats is done in a sin-

gle instruction. While each memory block can store

combinations of code and data, accesses are most efficient when

one block stores data, using the DM bus for transfers, and the

other block stores instructions and data, using the PM bus for

transfers. Using the DM bus and PM bus in this way, with one

dedicated to each memory block, assures single-cycle execution

with two data transfers. In this case, the instruction must be

available in the cache.

Off-Chip Memory and Peripherals Interface

The ADSP-21160x DSP’s external port provides the processor’s

interface to off-chip memory and peripherals. The 4G word off-

chip address space is included in the processor’s unified address

space. The separate on-chip buses—for PM addresses, PM data,

DM addresses, DM data, I/O addresses, and I/O data—are mul-

tiplexed at the external port to create an external system bus

with a single 32-bit address bus and a single 64-bit data bus. The

lower 32 bits of the external data bus connect to even addresses,

and the upper 32 bits of the 64 connect to odd addresses. Every

access to external memory is based on an address that fetches a

32-bit word, and with the 64-bit bus, two address locations can

be accessed at once. When fetching an instruction from external

memory, two 32-bit data locations are being accessed (16 bits

are unused). Figure 5 shows the alignment of various accesses to

external memory.

The external port supports asynchronous, synchronous, and

synchronous burst accesses. ZBT synchronous burst SRAM can

be interfaced gluelessly. Addressing of external memory devices

is facilitated by on-chip decoding of high-order address lines to

generate memory bank select signals. Separate control lines are

also generated for simplified addressing of page-mode DRAM.

The ADSP-21160x provides programmable memory wait states

and external memory acknowledge controls to allow interfacing

to DRAM and peripherals with variable access, hold, and disable

time requirements.

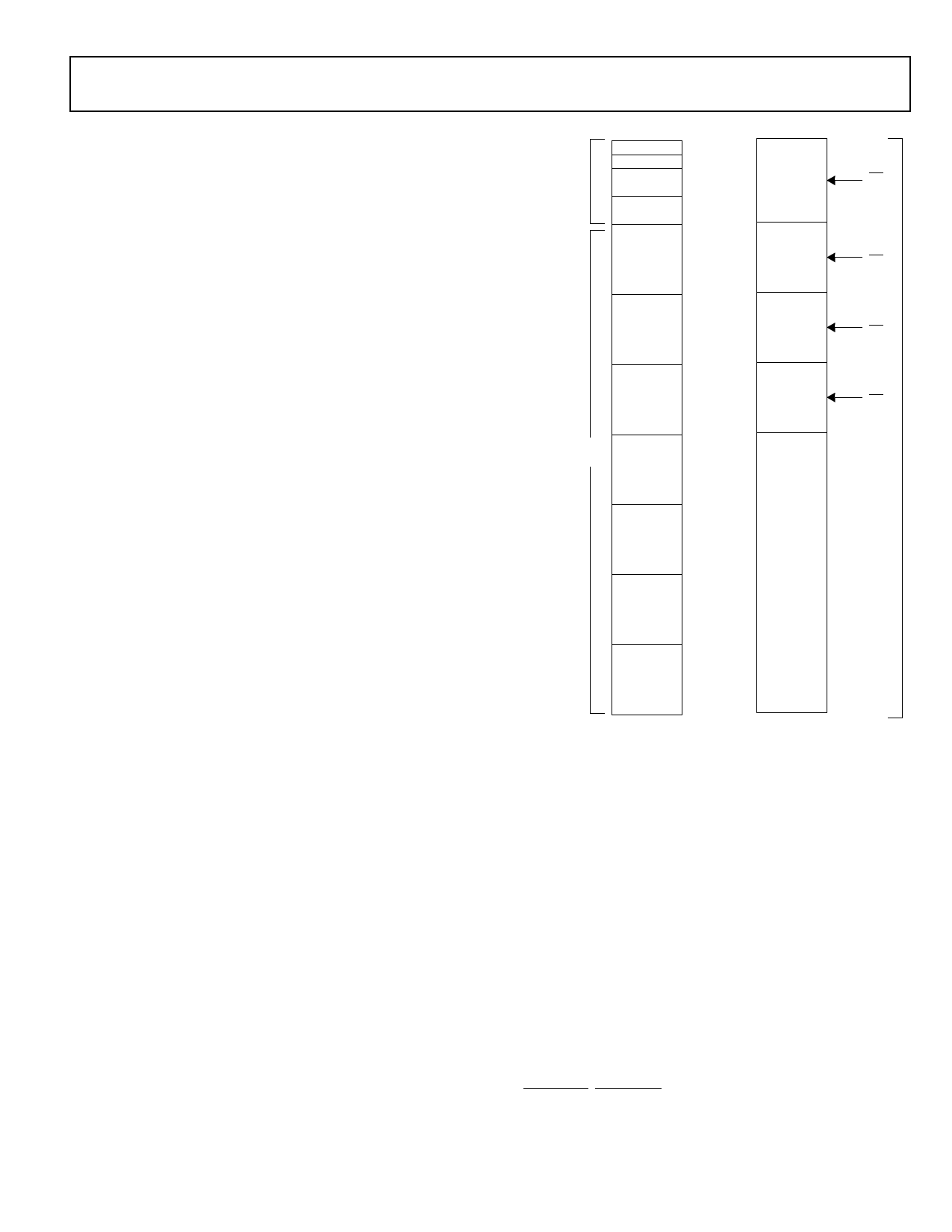

ADSP-21160M/ADSP-21160N

Internal

Memory

Space

IOP Reg’s

Long Word

Normal Word

0x00 0000

0x02 0000

0x04 0000

0x08 0000

Short Word

Internal

Memory

Space

(ID = 001)

Internal

Memory

Space

(ID = 010)

0x10 0000

0x20 0000

Internal

Memory

Space

(ID = 011)

Multiprocessor

Memory

Space

Internal

Memory

Space

(ID = 100)

Internal

Memory

Space

(ID = 101)

Internal

Memory

Space

(ID = 110)

0x30 0000

0x40 0000

0x50 0000

0x60 0000

Broadcast

Write to

All DSPs

(ID = 111)

0x70 0000

0x7F FFFF

Bank 0

0x80 0000

MS0

Bank 1

MS1

Bank 2

MS2

Bank 3

MS3

External

Memory

Space

Nonbanked

0xFFFF FFFF

Figure 4. Memory Map

DMA Controller

The ADSP-21160x DSP’s on-chip DMA controller allows zero-

overhead data transfers without processor intervention. The

DMA controller operates independently and invisibly to the

processor core, allowing DMA operations to occur while the

core is simultaneously executing its program instructions. DMA

transfers can occur between the processor’s internal memory

and external memory, external peripherals, or a host processor.

DMA transfers can also occur between the product’s DSP’s

internal memory and its serial ports or link ports. External bus

packing to 16-, 32-, 48-, or 64-bit words is performed during

DMA transfers. Fourteen channels of DMA are available on the

ADSP-21160x—six via the link ports, four via the serial ports,

and four via the processor’s external port (for either host pro-

cessor, other ADSP-21160x processors, memory or I/O

transfers). Programs can be downloaded to the processor using

DMA transfers. Asynchronous off-chip peripherals can control

two DMA channels using DMA Request/Grant lines

(DMAR1–2, DMAG1–2). Other DMA features include

Rev. D | Page 7 of 58 | September 2015