IDT79R4650100MS(1996) View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650100MS Datasheet PDF : 22 Pages

| |||

IDT79R4650

COMMERCIAL TEMPERATURE RANGE

I0

1I

2I

1R

2R

1A

2A

1D

2D

1W 2W

I1

1I

2I

1R

2R

1A

2A

1D

2D

1W 2W

I2

1I

2I

1R

2R

1A

2A

1D

2D

1W

•••

I3

1I

2I

1R

2R

1A

2A

1D

•••

I4

1I

2I

1R

2R

1A

•••

1I-1R

2I

2A-2D

1D

1D-2D

2R

2R

2R

2R

1A

1A-2A

1A

2A

1A

2W

one cycle

Instruction cache access

Instruction virtual to physical address translation

Data cache access and load align

Data virtual to physical address translation

Virtual to physical address translation

Register file read

Bypass calculation

Instruction decode

Branch address calculation

Issue or slip decision

Integer add, logical, shift

Data virtual address calculation

Store align

Branch decision

Register file write

Figure 2: R4650 Pipeline

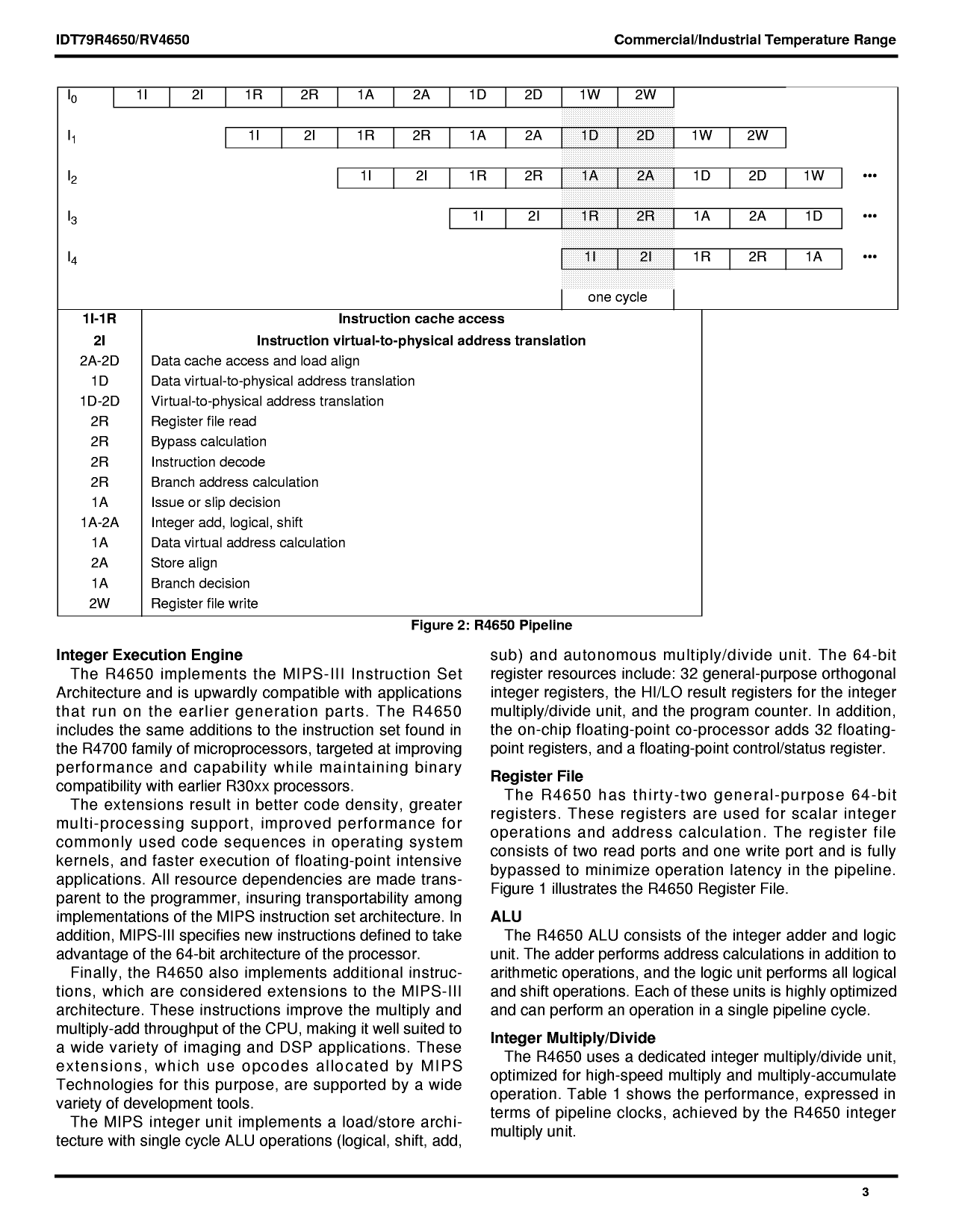

performance of the processor. Figure 2 shows the R4650

pipeline.

Integer Execution Engine

The R4650 implements the MIPS-III Instruction Set

Architecture, and thus is fully upward compatible with appli-

cations running on the earlier generation parts. The R4650

includes the same additions to the instruction set found in

the R4600 family of microprocessors, targeted at improving

performance and capability while maintaining binary

compatibility with earlier R30xx processors. The extensions

result in better code density, greater multi-processing

support, improved performance for commonly used code

sequences in operating system kernels, and faster

execution of floating-point intensive applications. All

resource dependencies are made transparent to the

programmer, insuring transportability among implementa-

tions of the MIPS instruction set architecture. In addition,

MIPS-III specifies new instructions defined to take

advantage of the 64-bit architecture of the processor.

Finally, the R4650 also implements additional instruc-

tions, which are considered extensions to the MIPS-III

architecture. These instructions improve the multiply and

multiply-add throughput of the CPU, making it well suited to

a wide variety of imaging and DSP applications. These

extensions, which use opcodes allocated by MIPS

Technologies for this purpose, are supported by a wide

variety of development tools.

The MIPS integer unit implements a load/store archi-

tecture with single cycle ALU operations (logical, shift, add,

sub) and autonomous multiply/divide unit. The 64-bit

register resources include: 32 general-purpose orthogonal

integer registers, the HI/LO result registers for the integer

multiply/divide unit, and the program counter. In addition,

the on-chip floating-point co-processor adds 32 floating-

point registers, and a floating-point control/status register.

Register File

The R4650 has thirty-two general-purpose 64-bit

registers. These registers are used for scalar integer

operations and address calculation. The register file

consists of two read ports and one write port, and is fully

bypassed to minimize operation latency in the pipeline.

Figure 1 illustrates the R4650 Register File.

ALU

The R4650 ALU consists of the integer adder and logic

unit. The adder performs address calculations in addition to

arithmetic operations, and the logic unit performs all logical

and shift operations. Each of these units is highly optimized

and can perform an operation in a single pipeline cycle.

5.8

3