IDT79R4650(1996) View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650 Datasheet PDF : 22 Pages

| |||

IDT79R4650

COMMERCIAL TEMPERATURE RANGE

of cached performance are achieved, while deterministic

real-time response is preserved.

Data Cache

For fast, single cycle data access, the R4650 includes an

8KB on-chip data cache that is two-way set associative

with a fixed 32-byte (eight words) line size. Table 4 lists the

R4650 cache attributes.

Characteristics

Size

Organization

Line size

Index

Tag

Write policy

Line transfer order

Miss restart after

transfer of

Parity

Cache locking

Instruction

8KB

2-way set associa-

tive

32B

vAddr 11..0

pAddr31..12

n.a.

read sub-block

order

write sequential

entire line

per-word

set A

Data

8KB

2-way set associa-

tive

32B

vAddr11..0

pAddr31..12

writeback /writethru

read sub-block

order

write sequential

first word

per-byte

set A

Table 4: R4650 Cache Attributes

The data cache is protected with byte parity and its tag is

protected with a single parity bit. It is virtually indexed and

physically tagged to allow simultaneous address translation

and data cache access

The normal write policy is writeback, which means that a

store to a cache line does not immediately cause memory

to be updated. This increases system performance by

reducing bus traffic and eliminating the bottleneck of

waiting for each store operation to finish before issuing a

subsequent memory operation. Software can however

select write-through for certain address ranges, using the

CAlg register in CP0. Cache protocols supported for the

data cache are:

• Uncached. Addresses in a memory area indicated as

uncached will not be read from the cache. Stores to such

addresses will be written directly to main memory, with-

out changing cache contents.

• Writeback. Loads and instruction fetches will first search

the cache, reading main memory only if the desired data

is not cache resident. On data store operations, the

cache is first searched to see if the target address is

cache resident. If it is resident, the cache contents will be

updated, and the cache line marked for later writeback. If

the cache lookup misses, the target line is first brought

into the cache before the cache is updated.

• Write-through with write allocate. Loads and instruc-

tion fetches will first search the cache, reading main

memory only if the desired data is not cache resident. On

data store operations, the cache is first searched to see if

the target address is cache resident. If it is resident, the

cache contents will be updated and main memory will

also be written; the state of the “writeback” bit of the

cache line will be unchanged. If the cache lookup misses,

the target line is first brought into the cache before the

cache is updated.

• Write-through without write-allocate. Loads and

instruction fetches will first search the cache, reading

main memory only if the desired data is not cache resi-

dent. On data store operations, the cache is first

searched to see if the target address is cache resident. If

it is resident, the cache contents will be updated, and the

cache line marked for later writeback. If the cache lookup

misses, then only main memory is written.

Associated with the Data Cache is the store buffer. When

the R4650 executes a Store instruction, this single-entry

buffer gets written with the store data while the tag

comparison is performed. If the tag matches, then the data

is written into the Data Cache in the next cycle that the

Data Cache is not accessed (the next non-load cycle). The

store buffer allows the R4650 to execute a store every

processor cycle and to perform back-to-back stores without

penalty.

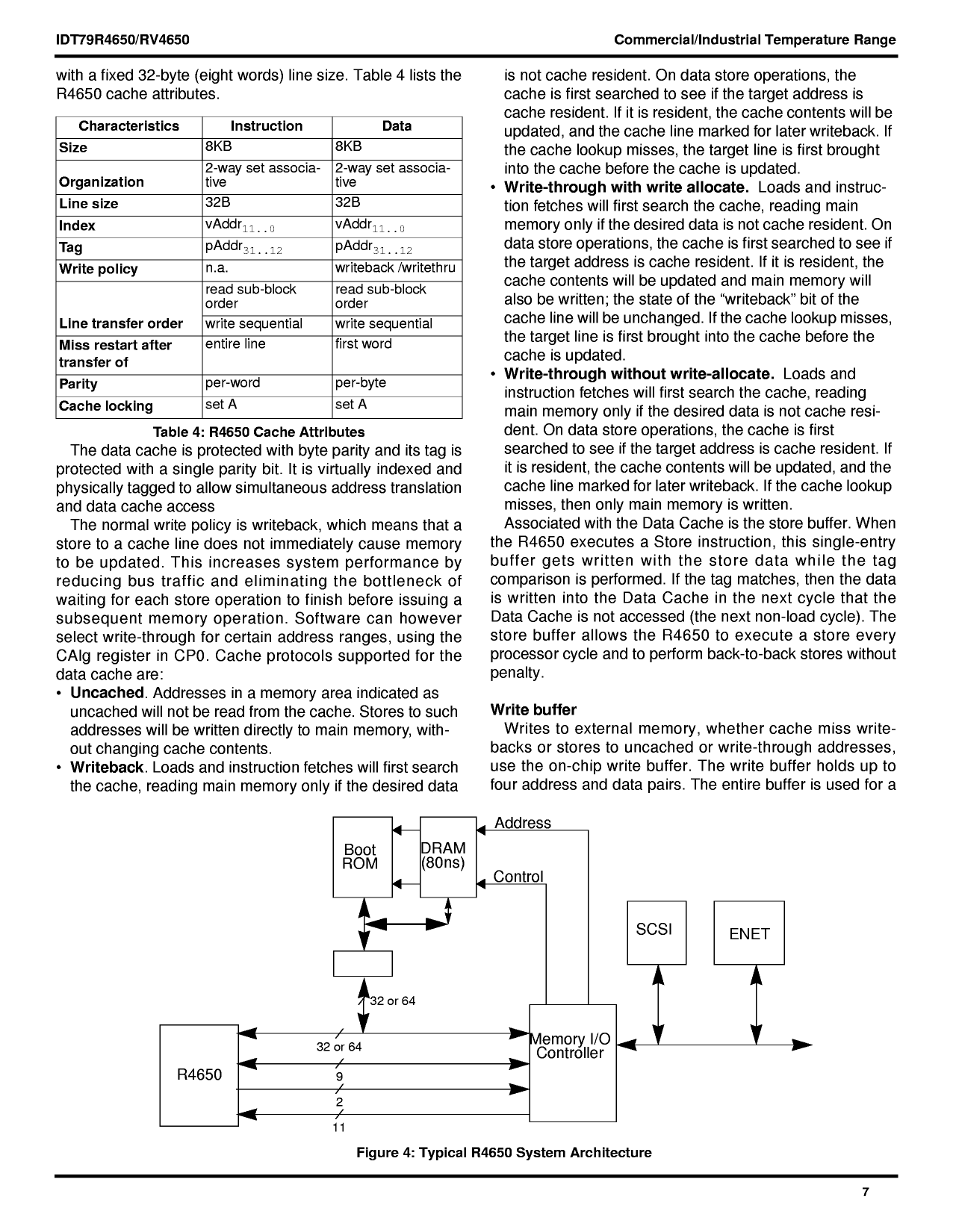

Boot

ROM

DRAM

(80ns)

Address

Control

SCSI

ENET

32 or 64

R4650

32 or 64

Memory I/O

Controller

9

2

11

Figure 4: Typical R4650 System Architecture

5.8

7