IDT79R4650-100DP(2000) View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650-100DP

(Rev.:2000)

(Rev.:2000)

IDT79R4650-100DP Datasheet PDF : 25 Pages

| |||

IDT79RC4650™

,QWHJHU#([HFXWLRQ#(QJLQH

The RC4650 implements the MIPS-III Instruction Set Architecture

and is upwardly compatible with applications that run on the earlier

generation parts. The RC4650 includes the same additions to the

instruction set found in the RC4700 family of microprocessors, targeted

at improving performance and capability while maintaining binary

compatibility with earlier RC3000 processors.

The extensions result in better code density, greater multi-processing

support, improved performance for commonly used code sequences in

operating system kernels, and faster execution of floating-point intensive

applications. All resource dependencies are made transparent to the

programmer, insuring transportability among implementations of the

MIPS instruction set architecture. In addition, MIPS-III specifies new

instructions defined to take advantage of the 64-bit architecture of the

processor.

Finally, the RC4650 also implements additional instructions, which

are considered extensions to the MIPS-III architecture. These instruc-

tions improve the multiply and multiply-add throughput of the CPU,

making it well suited to a wide variety of imaging and DSP applications.

These extensions, which use opcodes allocated by MIPS Technologies

for this purpose, are supported by a wide variety of development tools.

The MIPS integer unit implements a load/store architecture with

single cycle ALU operations (logical, shift, add, sub) and autonomous

multiply/divide unit. The 64-bit register resources include: 32 general-

purpose orthogonal integer registers, the HI/LO result registers for the

integer multiply/divide unit, and the program counter. In addition, the on-

chip floating-point co-processor adds 32 floating-point registers, and a

floating-point control/status register.

5HJLVWHU#)LOH

The RC4650 has thirty-two general-purpose 64-bit registers. These

registers are used for scalar integer operations and address calculation.

The register file consists of two read ports and one write port and is fully

bypassed to minimize operation latency in the pipeline. Figure 1 illus-

trates the RC4650 Register File.

$/8

The RC4650 ALU consists of the integer adder and logic unit. The

adder performs address calculations in addition to arithmetic operations,

and the logic unit performs all logical and shift operations. Each of these

units is highly optimized and can perform an operation in a single pipe-

line cycle.

,QWHJHU#0XOWLSO\2'LYLGH

The RC4650 uses a dedicated integer multiply/divide unit, optimized

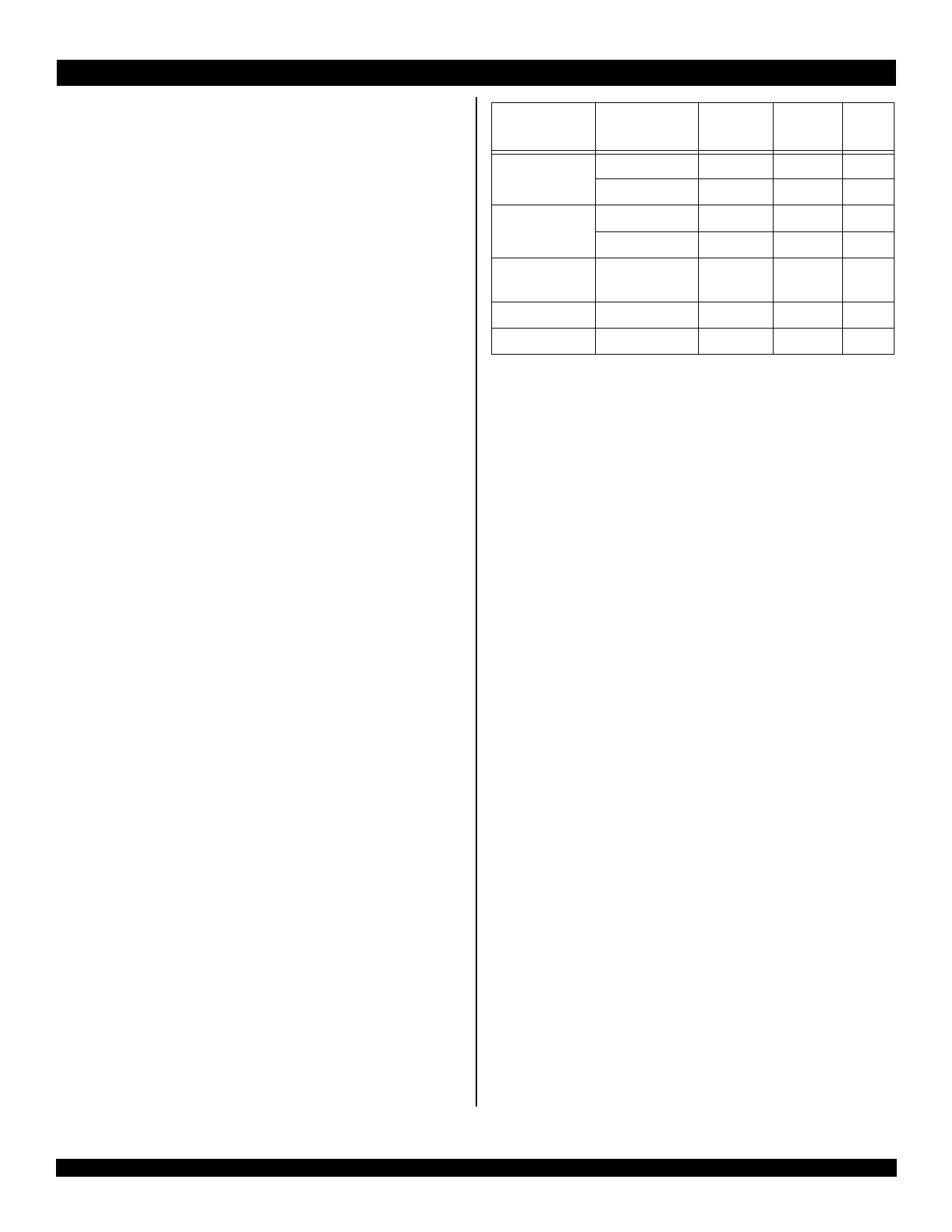

for high-speed multiply and multiply-accumulate operation. Table 1

shows the performance, expressed in terms of pipeline clocks, achieved

by the RC4650 integer multiply unit.

2SFRGH

2SHUDQG#

6L]H

/DWHQF\ 5HSHDW 6WDOO

MULT/U, MAD/U 16 bit

32 bit

3

2

0

4

3

0

MUL

16 bit

3

2

1

32 bit

4

3

2

DMULT,

any

DMULTU

6

5

0

DIV, DIVU

any

36

36

0

DDIV, DDIVU any

68

68

0

Table 1 RC4650 Integer Multiply Operation

The MIPS-III architecture defines that the results of a multiply or

divide operation are placed in the HI and LO registers. The values can

then be transferred to the general purpose register file using the MFHI/

MFLO instructions.

The RC4650 adds a new multiply instruction, “MUL”, which can

specify that the multiply results bypass the “Lo” register and are placed

immediately in the primary register file. By avoiding the explicit “Move-

from-Lo” instruction required when using “Lo”, throughput of multiply-

intensive operations is increased.

An additional enhancement offered by the RC4650 is an atomic

“multiply-add” operation, MAD, used to perform multiply-accumulate

operations. This instruction multiplies two numbers and adds the product

to the current contents of the HI and LO registers. This operation is used

in numerous DSP algorithms, and allows the RC4650 to cost reduce

systems requiring a mix of DSP and control functions.

Finally, aggressive implementation techniques feature low latency for

these operations along with pipelining to allow new operations to be

issued before a previous one has fully completed. Table 1 also shows

the repeat rate (peak issue rate), latency, and number of processor stalls

required for the various operations. The RC4650 performs automatic

operand size detection to determine the size of the operand, and imple-

ments hardware interlocks to prevent overrun, allowing this high-perfor-

mance to be achieved with simple programming.

)ORDWLQJ03RLQW#&R03URFHVVRU

The RC4650 incorporates an entire single-precision floating-point co-

processor on chip, including a floating-point register file and execution

units. The floating-point co-processor forms a “seamless” interface with

the integer unit, decoding and executing instructions in parallel with the

integer unit.

The RC4650’s floating-point unit directly implements single-precision

floating-point operations. This enables the RC4650 to perform functions

such as graphics rendering, without requiring extensive die are or power

consumption.

The RC4650 does not directly implement the double-precision opera-

tions found in the RC64475. However, to maintain software compatibility,

3 of 25

March 28, 2000