IDT79R4650-100DP(2000) View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650-100DP

(Rev.:2000)

(Rev.:2000)

IDT79R4650-100DP Datasheet PDF : 25 Pages

| |||

IDT79RC4650™

6\VWHP#,QWHUIDFH

The RC4650 supports a 64-bit system interface that is bus compat-

ible with the RC4700 system interface. In addition, the RC4650 supports

a 32-bit system interface mode, allowing the CPU to interface directly

with a lower cost memory system.

The RC64475 supports a 64-bit system interface that is bus compat-

ible with the RC4650 system interface.

The interface consists of a 64-bit Address/Data bus with 8 check bits

and a 9-bit command bus protected with parity. In addition, there are 8

handshake signals and 6 interrupt inputs. The interface has a simple

timing specification and is capable of transferring data between the

processor and memory at a peak rate of 1000MB/sec.

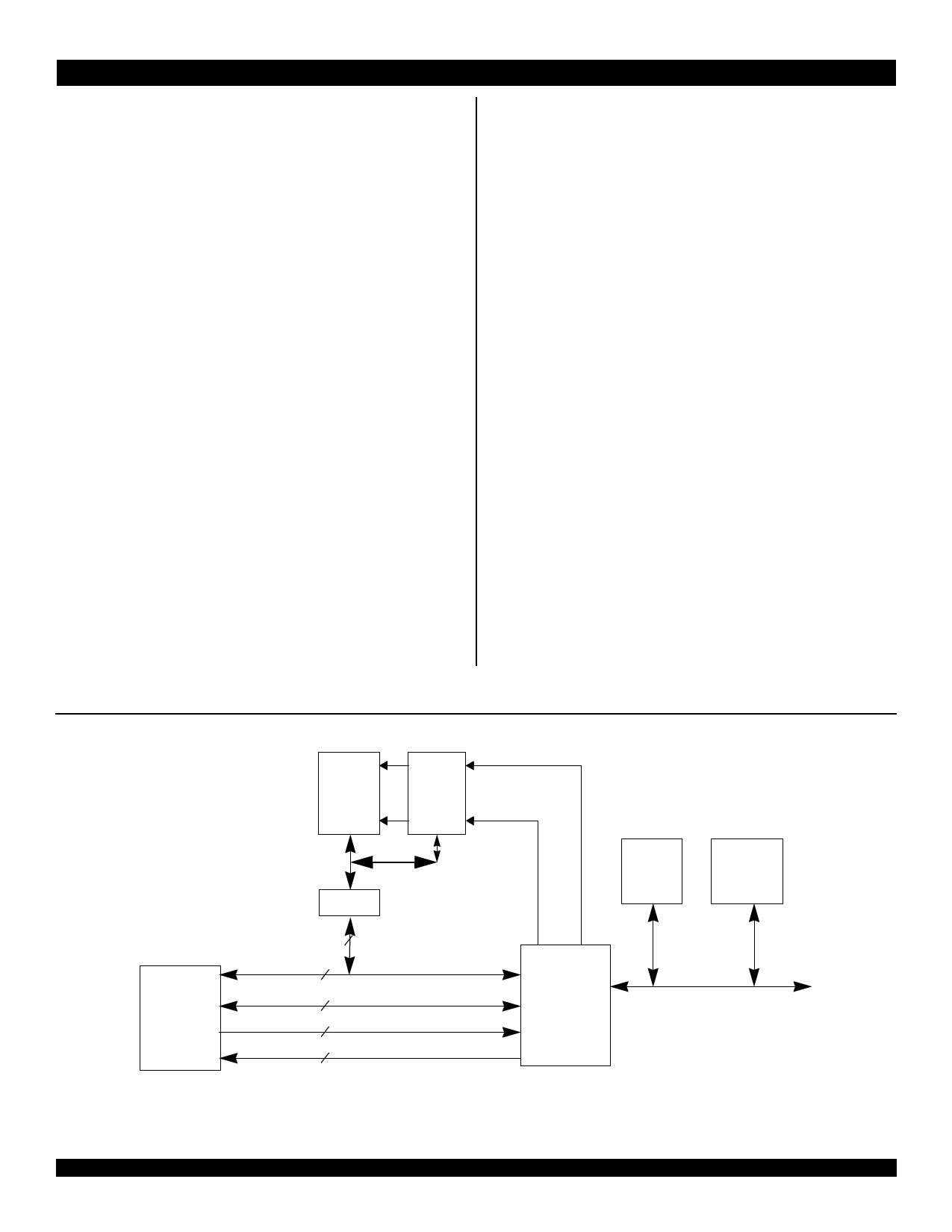

Figure 3 shows a typical system using the RC4650. In this example

two banks of DRAMs are used to supply and accept data with a

DDxxDD data pattern.

The RC4650 clocking interface allows the CPU to be easily mated

with external reference clocks. The CPU input clock is the bus reference

clock, and can be between 50 and 125MHz (somewhat dependent on

maximum pipeline speed for the CPU).

An on-chip phase-locked-loop generates the pipeline clock from the

system interface clock by multiplying it up an amount selected at system

reset. Supported multipliers are values 2 through 8 inclusive, allowing

systems to implement pipeline clocks at significantly higher frequency

than the system interface clock.

6\VWHP#$GGUHVV2'DWD#%XV

The 64-bit System Address Data (SysAD) bus is used to transfer

addresses and data between the RC4650 and the rest of the system. It

is protected with an 8-bit parity check bus, SysADC. When initialized for

32-bit operation, SysAD can be viewed as a 32-bit multiplexed bus, with

4 parity check bits.

The system interface is configurable to allow easier interfacing to

memory and I/O systems of varying frequencies. The bus frequency and

reference timing of the RC4650 are taken from the input clock. The rate

at which the CPU transmits data to the system interface is program-

mable via boot time mode control bits. The rate at which the processor

receives data is fully controlled by the external device. Therefore, either

a low cost interface requiring no read or write buffering or a faster, high

performance interface can be designed to communicate with the

RC4650. Again, the system designer has the flexibility to make these

price/performance trade-offs.

6\VWHP#&RPPDQG#%XV

The RC4650 interface has a 9-bit System Command (SysCmd) bus.

The command bus indicates whether the SysAD bus carries an address

or data. If the SysAD carries an address, then the SysCmd bus also indi-

cates what type of transaction is to take place (for example, a read or

write). If the SysAD carries data, then the SysCmd bus also gives infor-

mation about the data (for example, this is the last data word trans-

mitted, or the cache state of this data line is clean exclusive). The

SysCmd bus is bidirectional to support both processor requests and

external requests to the RC4650. Processor requests are initiated by the

RC4650 and responded to by an external device. External requests are

issued by an external device and require the RC4650 to respond.

RC4650

Address

Boot

DRAM

ROM

(80ns)

Control

SCSI

32 or 64

32 or 64

9

Memory I/O

Controller

2

11

Figure 3 Typical RC4650 System Architecture

7 of 25

ENET

March 28, 2000