IDT79R4650-100DP(2000) View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650-100DP

(Rev.:2000)

(Rev.:2000)

IDT79R4650-100DP Datasheet PDF : 25 Pages

| |||

IDT79RC4650™

The RC4650 supports single datum (one to eight byte) and 8-word

block transfers on the SysAD bus. In the case of a single-datum transfer,

the low-order 3 address bits gives the byte address of the transfer, and

the SysCmd bus indicates the number of bytes being transferred. The

choice of 32- or 64-bit wide system interface dictates whether a cache

line block transaction requires 4 double word data cycles or 8 single

word cycles, and whether a single datum transfer larger than 4 bytes

needs to be broken into two smaller transfers.

+DQGVKDNH#6LJQDOV

There are six handshake signals on the system interface. Two of

these signals, RdRdy* and WrRdy*, are used by an external device to

indicate to the RC4650 whether it can accept a new read or write trans-

action. The RC4650 samples these signals before deasserting the

address on read and write requests.

ExtRqst* and Release* are used to transfer control of the SysAD and

SysCmd buses between the processor and an external device. When an

external device needs to control the interface, it asserts ExtRqst*. The

RC4650 responds by asserting Release* to release the system interface

to slave state.

ValidOut* and ValidIn* are used by the RC4650 and the external

device respectively to indicate that there is a valid command or data on

the SysAD and SysCmd buses. The RC4650 asserts ValidOut* when it

is driving these buses with a valid command or data, and the external

device drives ValidIn* when it has control of the buses and is driving a

valid command or data.

1RQ02YHUODSSLQJ#6\VWHP#,QWHUIDFH

The RC4650 requires a non-overlapping system interface, compat-

ible with the RC4700. This means that only one processor request may

be outstanding at a time and that the request must be serviced by an

external device before the RC4650 issues another request. The RC4650

can issue read and write requests to an external device, and an external

device can issue read and write requests to the RC4650.

The RC4650 asserts ValidOut* and simultaneously drives the

address and read command on the SysAD and SysCmd buses. If the

system interface has RdRdy* or Read transactions asserted, then the

processor tristates its drivers and releases the system interface to slave

state by asserting Release*. The external device can then begin sending

the data to the RC4650.

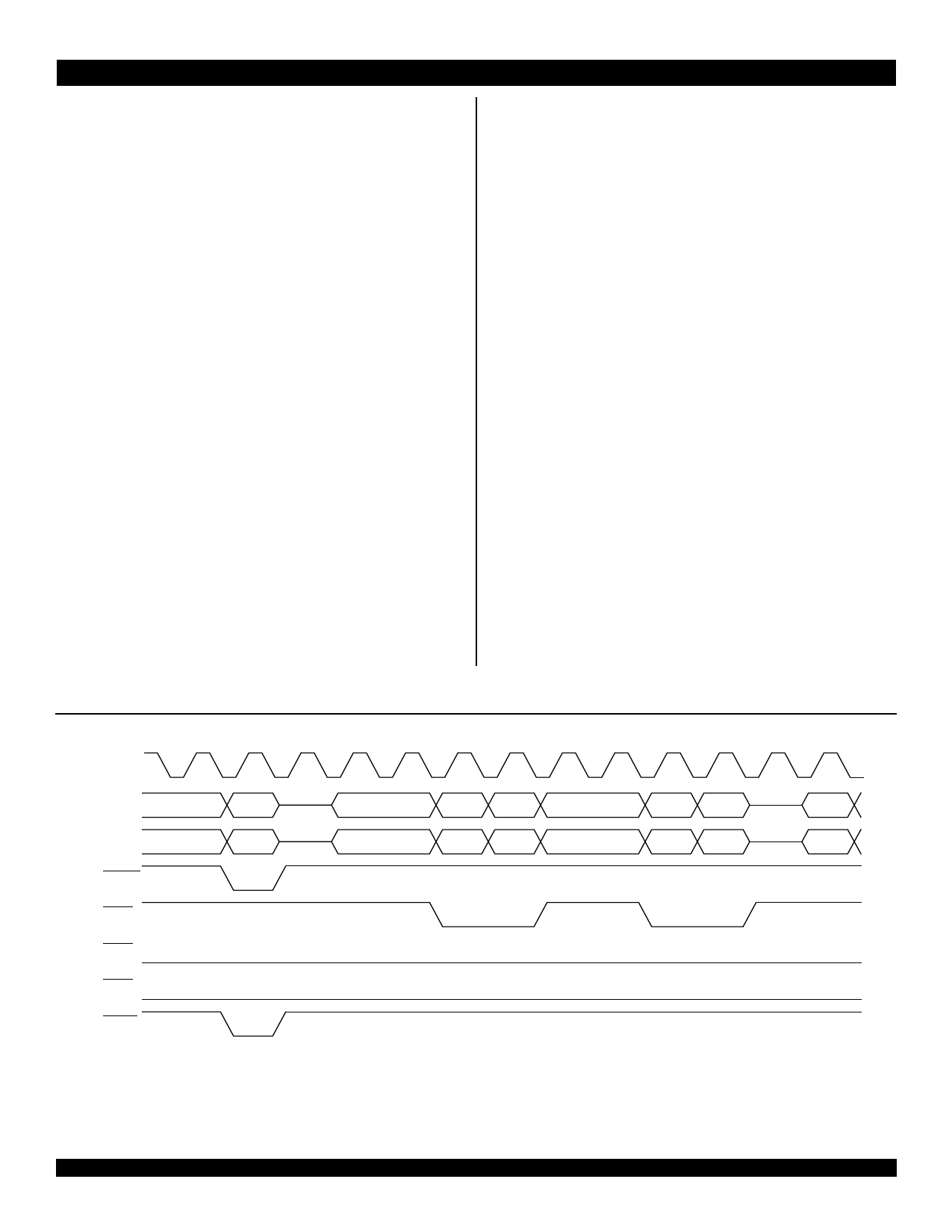

Figure 4 shows a processor block read request and the external

agent read response. The read latency is 4 cycles (ValidOut* to

ValidIn*), and the response data pattern is DDxxDD. Figure 5 shows a

processor block write.

:ULWH#5HLVVXH#DQG#3LSHOLQH#:ULWH

The RC4700 and the RC4650 implement additional write protocols

designed to improve performance. This implementation doubles the

effective write bandwidth. The write re-issue has a high repeat rate of 2

cycles per write. A write issues if WrRdy is asserted 2 cycles earlier and

is still asserted at the issue cycle. If it is not still asserted, the last write

re-issues again. Pipelined writes have the same 2-cycle per write repeat

rate, but can issue one more write after WrRdy de-asserts. They still

follow the issue rule as R4x00 mode for other writes.

([WHUQDO#5HTXHVWV

The RC4650 responds to requests issued by an external device. The

requests can take several forms. An external device may need to supply

data in response to an RC4650 read request or it may need to gain

control over the system interface bus to access other resources which

may be on that bus.

MasterClock

SysAD

SysCmd

ValidOut

ValidIn

RdRdy

WrRdy

Release

Addr

Read

Data0

Data1

CData CData

Data2 Data3

CData CEOD

Figure 4 RC4650 Block Read Request (64-bit interface option)

8 of 25

March 28, 2000