IDT79R4650-267DP View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650-267DP Datasheet PDF : 25 Pages

| |||

IDT79RC4650™

the RC4650 will signal a trap when a double-precision operation is initi-

ated, allowing the requested function to be emulated in software. Alter-

natively, the system architect could use a software library emulation of

double-precision functions, selected at compile time, to eliminate the

overhead associated with trap and emulation.

Floating-Point Units

The RC4650 floating-point execution units perform single precision

arithmetic, as specified in the IEEE Standard 754. The execution unit is

broken into a separate multiply unit and a combined add/convert/divide/

square root unit. Overlap of multiplies and add/subtract is supported.

The multiplier is partially pipelined, allowing a new multiply to begin

every 6 cycles.

As in the IDT79RC64475, the RC4650 maintains fully precise

floating-point exceptions while allowing both overlapped and pipelined

operations. Precise exceptions are extremely important in mission-crit-

ical environments, such as ADA, and highly desirable for debugging in

any environment.

The floating-point unit’s operation set includes floating-point add,

subtract, multiply, divide, square root, conversion between fixed-point

and floating-point format, conversion among floating-point formats, and

floating-point compare.These operations comply with IEEE Standard

754. Double precision operations are not directly supported; attempts to

execute double-precision floating point operations, or refer directly to

double-precision registers, result in the RC4650 signalling a “trap” to the

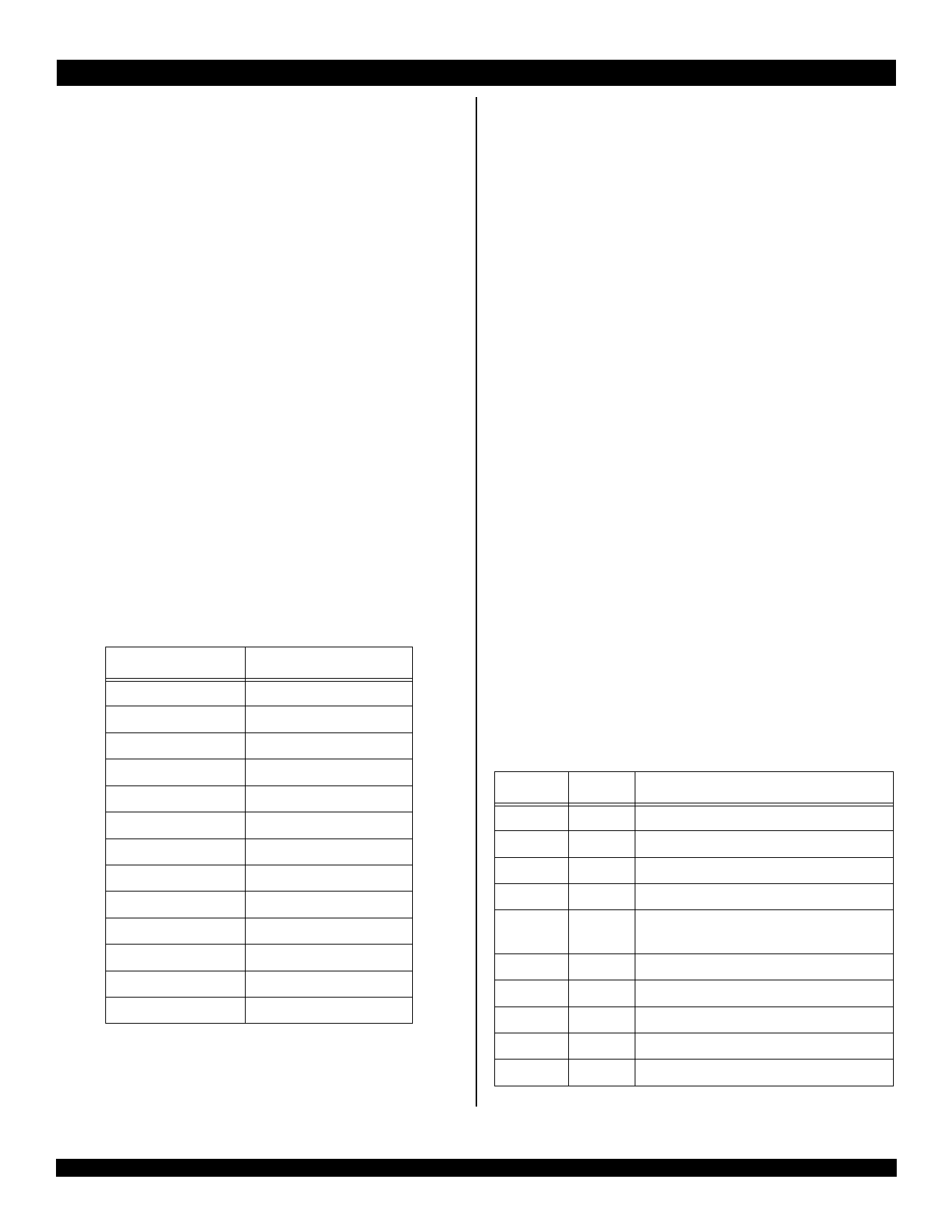

CPU, enabling emulation of the requested function. Table 2 gives the

latencies of some of the floating-point instructions in internal processor

cycles.

Operation

Instruction Latency

ADD

4

SUB

4

MUL

8

DIV

32

SQRT

31

CMP

3

FIX

4

FLOAT

6

ABS

1

MOV

1

NEG

1

LWC1

2

SWC1

1

Table 2 Floating-Point Operation

Floating-Point General Register File

The floating-point register file is made up of thirty-two 32-bit regis-

ters. These registers are used as source or target registers for the

single-precision operations. References to these registers as 64-bit

registers (as supported in the RC64475) will cause a trap to be

signalled.

The floating-point control register space contains two registers; one

for determining configuration and revision information for the copro-

cessor and one for control and status information. These are primarily

involved with diagnostic software, exception handling, state saving and

restoring, and control of rounding modes.

System Control Co-Processor (CP0)

The system control co-processor in the MIPS architecture is respon-

sible for the virtual to physical address translation and cache protocols,

the exception control system, and the diagnostics capability of the

processor. In the MIPS architecture, the system control co-processor

(and thus the kernel software) is implementation dependent.

In the RC4650, significant changes in CP0—relative to the

RC4700—have been implemented. These changes are designed to

simplify memory management, facilitate debug, and speed real-time

processing.

System Control Co-Processor Registers

The RC4650 incorporates all system control co-processor (CP0)

registers on-chip. These registers provide the path through which the

virtual memory system’s address translation is controlled, exceptions

are handled, and operating modes are controlled (kernel vs. user mode,

interrupts enabled or disabled, cache features). In addition, the RC4650

includes registers to implement a real-time cycle counting facility, which

aids in cache diagnostic testing, assists in data error detection, and

facilitates software debug. Alternatively, this timer can be used as the

operating system reference timer, and can signal a periodic interrupt.

Table 3 shows the CP0 registers of the RC4650.

Number Name

Function

0

IBase

Instruction address space base

1

IBound Instruction address space bound

2

DBase Data address space base

3

DBound Data address space bound

4-7, 10, 20- —

25, 29, 31

Not used

8

BadVAddr Virtual address on address exceptions

9

Count

Counts every other cycle

11

Compare Generate interrupt when Count = Compare

12

Status Miscellaneous control/status

13

Cause Exception/Interrupt information

Table 3 RC4650 CPO Registers (Page 1 of 2)

4 of 25

April 10, 2001