IDT79R4650-180DP View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT79R4650-180DP Datasheet PDF : 25 Pages

| |||

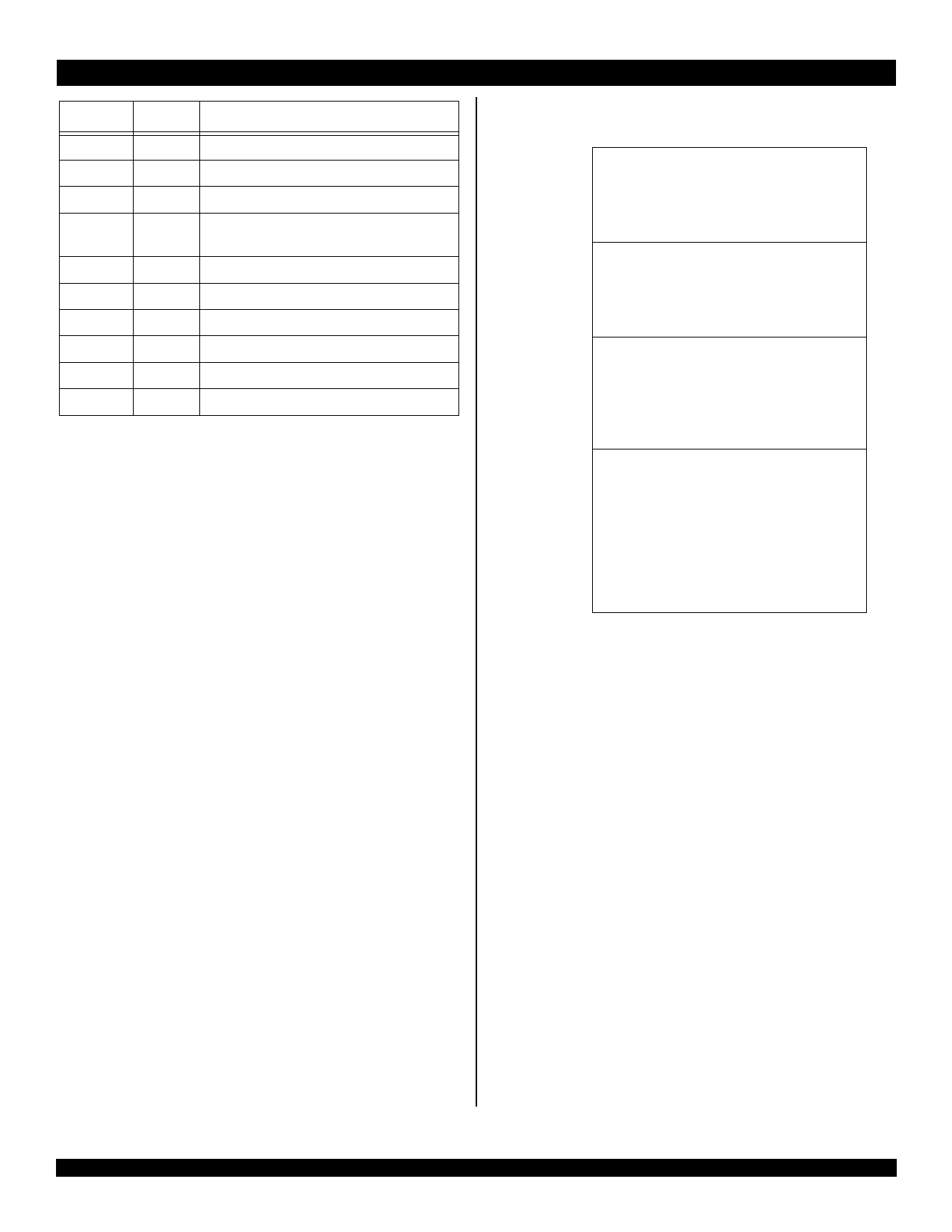

IDT79RC4650™

Number Name

Function

14

EPC

Exception PC

15

PRId

Processor ID

16

Config Cache and system attributes

17

CAlg

Cache attributes for the eight 512MB regions of

the virtual address space

18

IWatch Instruction breakpoint virtual address

19

DWatch Data breakpoint virtual address

26

ECC

Used in cache diagnostics

27

CacheErr Cache diagnostics

28

TagLo

Cache index

30

ErrorEPC CacheError exception PC

Table 3 RC4650 CPO Registers (Page 2 of 2)

Operation Modes

The RC4650 supports two modes of operation: user mode and

kernel mode. Kernel mode operation is typically used for exception

handling and operating system kernel functions, including CP0 manage-

ment and access to IO devices. In kernel mode, software has access to

the entire address space and all of the co-processor 0 registers, and can

select whether to enable co-processor 1 accesses. The processor

enters kernel mode at reset, and whenever an exception is recognized.

User mode is typically used for applications programs. User mode

accesses are limited to a subset of the virtual address space and can be

inhibited from accessing CP0 functions

Virtual-to-Physical Address Mapping

The 4GB virtual address space of the RC4650 is shown in Figure 2.

The 4 GB address space is divided into addresses accessible in either

kernel or user mode (kuseg), and addresses only accessible in kernel

mode (kseg2:0).

The RC4650 supports the use of multiple user tasks sharing

common virtual addresses, but mapped to separate physical addresses.

This facility is implemented via the “base-bounds” registers contained in

CP0.

When a user virtual address is asserted (load, store, or instruction

fetch), the RC4650 compares the virtual address with the contents of the

appropriate “bounds” register (instruction or data). If the virtual address

is “in bounds”, the value of the corresponding “base” register is added to

the virtual address to form the physical address for that reference. If the

address is not within bounds, an exception is signalled.

This facility enables multiple user processes in a single physical

memory without the use of a TLB. This type of operation is further

supported by a number of development tools for the RC4650, including

real-time operating systems and “position independent code.”

Kernel mode addresses do not use the base-bounds registers, but

rather undergo a fixed virtual-to-physical address translation.

0xFFFFFFFF

0xC0000000

0xBFFFFFFF

0xA0000000

0x9FFFFFFF

Kernel virtual address space

(kseg2)

Unmapped, 1.0 GB

Uncached kernel physical address space

(kseg1)

Unmapped, 0.5GB

Cached kernel physical address space

(kseg0)

Unmapped, 0.5GB

0x80000000

0x7FFFFFF

User virtual address space

(useg)

Mapped, 2.0GB

0x00000000

Figure 2 Kernel/User Mode Virtual Addressing (32-bit mode)

Debug Support

To facilitate software debug, the RC4650 adds a pair of “watch” regis-

ters to CP0. When enabled, these registers will cause the CPU to take

an exception when a “watched” address is appropriately accessed.

Interrupt Vector

The RC4650 also adds the capability to speed interrupt exception

decoding. Unlike the RC4700, which utilizes a single common exception

vector for all exception types (including interrupts), the RC4650 allows

kernel software to enable a separate interrupt exception vector. When

enabled, this vector location speeds interrupt processing by allowing

software to avoid decoding interrupts from general purpose exceptions.

Cache Memory

To keep the RC4650’s high-performance pipeline full and operating

efficiently, the RC4650 incorporates on-chip instruction and data caches

that can each be accessed in a single processor cycle. Each cache has

its own 64-bit data path and can be accessed in parallel. The cache

subsystem provides the integer and floating-point units with an aggre-

gate bandwidth of over 3200 MB per second at a pipeline clock

frequency of 267MHz. The cache subsystem is similar in construction to

that found in the RC4700, although some changes have been imple-

mented. Table 4 is an overview of the caches found on the RC4650.

5 of 25

April 10, 2001