Rev 1.0 02/26/18

#### N-Channel Enhancement Mode Field Effect Transistor in bare die form

### Features:

- High Density Cell Design for Low R<sub>DS(ON)</sub>

- Voltage Controlled Small Signal Switch

- Rugged and Reliable with Gold Back Metal

- High Reliability tested grades for Military + Space

## Ordering Information:

The following part suffixes apply:

- No suffix MIL-STD-750 /2072 Visual Inspection

- "H" MIL-STD-750 /2072 Visual Inspection+ MIL-PRF-38534 Class H LAT

- "K" MIL-STD-750 /2072 Visual Inspection+ MIL-PRF-38534 Class K LAT

LAT = Lot Acceptance Test.

For further information on LAT process flows see below.

www.siliconsupplies.com\quality\bare-die-lot-qualification

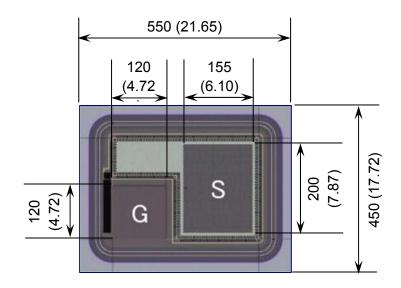

## Die Dimensions in µm (mils)

G = GATE S = SOURCE

**DIE BACK = DRAIN**

## **Supply Formats:**

- Default Die in Waffle Pack (400 per tray capacity)

- Sawn Wafer on Tape On request

- Unsawn Wafer On request

- With additional electrical selection On request

- Sawn as pairs or adjacent pair pick On request

- Assembled in metal or ceramic package On request

## **Mechanical Specification**

| Die Size<br>(Excluding Saw Street) | 550 x 450<br>22 x 18      | μm<br>mils |  |

|------------------------------------|---------------------------|------------|--|

| Gate Pad Size                      | 120 x 120<br>4.72 x 4.72  | μm<br>mils |  |

| Source Pad Size                    | 155 x 200<br>6.10 x 7.87  | μm<br>mils |  |

| Die Thickness                      | 140 (±20)<br>5.51 (±0.79) | μm<br>mils |  |

| Top Metal Composition              | Al-Si 4.6µm               |            |  |

| Back Metal Composition             | Au 0.9µm                  |            |  |

Rev 1.0 02/26/18

## Absolute Maximum Ratings<sup>1</sup> T<sub>J</sub> = 25°C unless otherwise stated

| PARAMETER                                                    | SYMBOL                           | VALUE      | UNIT  |  |

|--------------------------------------------------------------|----------------------------------|------------|-------|--|

| Drain-to-Source Voltage                                      | V <sub>DSS</sub>                 | 60         | V     |  |

| Drain-Gate Voltage (R <sub>GS</sub> ≤ 1MΩ)                   | $V_{DGR}$                        | 60         | V     |  |

| Gate-Source Voltage - Continuous                             |                                  | ±20        |       |  |

| Gate-Source Voltage – Non<br>Repetitive (tp < 50µs)          | $V_{GSS}$                        | ±40        | V     |  |

| Maximum Drain Current - Continuous                           | L-                               | 200        | mA    |  |

| Maximum Drain Current - Pulsed                               | I <sub>D</sub>                   | 500        |       |  |

| Maximum Power Dissipation<br>Derated above 25°C <sup>2</sup> | PD                               | 400        | mW    |  |

|                                                              |                                  | 3.2        | mW/°C |  |

| Junction & Storage Temperature                               | T <sub>J,</sub> T <sub>stg</sub> | -55 to 150 | °C    |  |

| THERMAL CHARACTERISTICS                                      |                                  |            |       |  |

| Thermal Resistance,<br>Junction to Ambient <sup>2</sup>      | R <sub>θJA</sub>                 | 312.5      | °C/W  |  |

<sup>1.</sup> Operation above the absolute maximum rating may cause device failure. Operation at the absolute maximum ratings, for extended periods, may reduce device reliability.

## Electrical Characteristics T<sub>J</sub> = 25°C unless otherwise stated

| PARAMETER                            | SYMBOL              | CONDITIONS                                                                                       | MIN | TYP  | MAX | UNIT |

|--------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|------|

| OFF CHARACTERISTICS <sup>3</sup>     |                     |                                                                                                  |     |      |     |      |

| Drain-Source Breakdown Voltage       | BV <sub>DSS</sub>   | $V_{GS} = 0V, I_D = 10\mu A$                                                                     | 60  | -    | -   | V    |

| Zero Gate Voltage Drain Current      | I <sub>DSS</sub>    | V <sub>DS</sub> = 48V, V <sub>GS</sub> = 0                                                       | -   | -    | 1   | μA   |

|                                      |                     | $V_{DS} = 48V, V_{GS} = 0, T_{J} = 125^{\circ}C$                                                 | -   | -    | 1   | mA   |

| Gate-Body Leakage, Forward           | I <sub>GSSF</sub>   | V <sub>GS</sub> = 15V, V <sub>DS</sub> = 0V                                                      | -   | -    | 10  | nA   |

| Gate-Body Leakage, Reverse           | I <sub>GSSR</sub>   | V <sub>GS</sub> = -15V, V <sub>DS</sub> = 0V                                                     | -   | -    | -10 | nA   |

| ON CHARACTERISTICS <sup>3</sup>      |                     |                                                                                                  |     |      |     |      |

| Gate Threshold Voltage               | V <sub>GS(th)</sub> | $V_{DS} = V_{GS}$ , $I_D = 1mA$                                                                  | 0.8 | 2.1  | 3   | V    |

| Static Drain-Source On-Resistance    | R <sub>DS(ON)</sub> | V <sub>GS</sub> = 10V, I <sub>D</sub> = 500mA                                                    | -   | 1.2  | 5   | Ω    |

|                                      |                     | $V_{GS}$ = 10V, $I_D$ = 500mA, $T_J$ = 125°C                                                     | -   | 1.9  | 9   |      |

|                                      |                     | $V_{GS} = 4.5V, I_D = 75mA$                                                                      | -   | 1.8  | 5.3 |      |

| Drain-Source On-Voltage              | V <sub>DS(ON)</sub> | V <sub>GS</sub> = 10V, I <sub>D</sub> = 500mA                                                    | -   | 0.6  | 2.5 | V    |

|                                      |                     | $V_{GS} = 4.5V, I_D = 75mA$                                                                      | -   | 0.14 | 0.4 | V    |

| On-State Drain Current               | I <sub>D(ON)</sub>  | V <sub>GS</sub> = 4.5V, V <sub>DS</sub> = 10V                                                    | 75  | 600  | -   | mA   |

| Forward Transconductance             | <b>9</b> FS         | V <sub>DS</sub> = 10V, I <sub>D</sub> = 200mA                                                    | 100 | 320  | -   | mS   |

| DYNAMIC CHARACTERISTICS <sup>4</sup> |                     |                                                                                                  |     |      |     |      |

| Input Capacitance                    | C <sub>iss</sub>    | V <sub>DS</sub> = 25V, V <sub>GS</sub> = 0V, f = 1MHz                                            | -   | 20   | 50  |      |

| Output Capacitance                   | Coss                |                                                                                                  | -   | 11   | 25  | pF   |

| Reverse Transfer Capacitance         | C <sub>rss</sub>    |                                                                                                  | -   | 4    | 5   |      |

| Turn-On Time                         | t <sub>on</sub>     | $V_{DD}$ = 15V, $R_{L}$ = 25 $\Omega$ , $I_{D}$ = 500mA, $V_{GS}$ = 10V, $R_{GEN}$ = 25 $\Omega$ | -   | -    | 10  | ns   |

| Turn-Off Time                        | t <sub>off</sub>    |                                                                                                  | -   | -    | 10  | 113  |

<sup>3.</sup> Pulse Test: Pulse width  $\leq$  300µs, Duty Cycle  $\leq$  2%. 4. Not production testing in die form, characterized by chip design & tested in package LAT.

<sup>2.</sup> Power dissipation & thermal characterisation in TO-92 package. Performance at die level dependent on assembly method and substrate choice.

# Rev 1.0 02/26/18

## **Typical Electrical Characteristics**

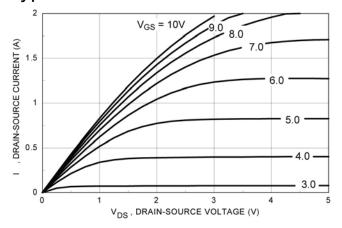

Fig 1 – On-Region Characteristics

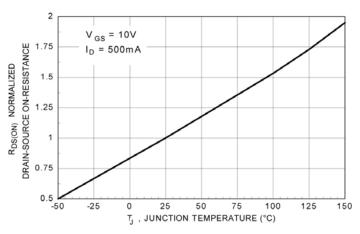

Fig 3 – On-Resistance Variation with Temperature

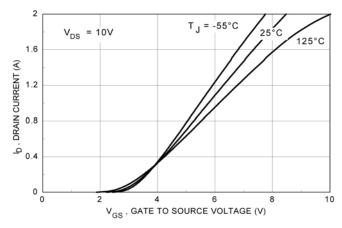

Fig 5 – Transfer Characteristics

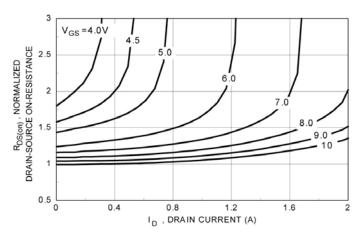

Fig 2 – On-Resistance Variation with Gate Voltage and Drain Current

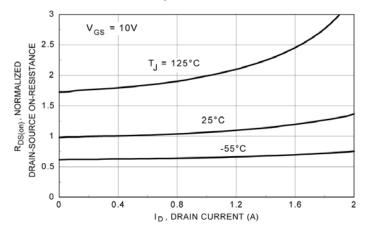

**Fig 4** – On-Resistance Variation with Drain Current and Temperature

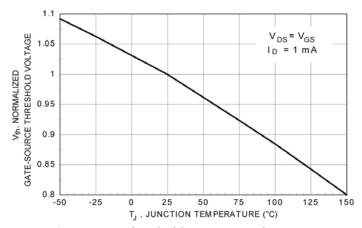

Fig 6 – Gate Threshold variation with Temperature

Rev 1.0 02/26/18

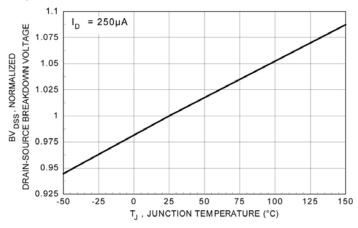

## Typical Electrical Characteristics continued

Fig 7 – Gate Threshold variation with Temperature

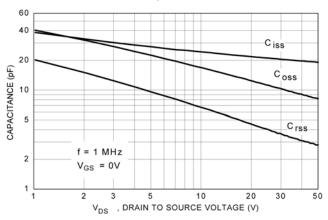

Fig 9 - Capacitance Characteristics

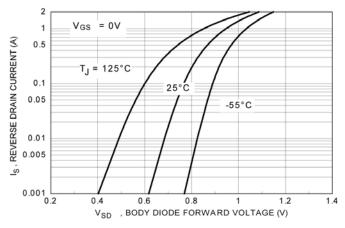

Fig 8 – Body Diode Forward Voltage variation with Temperature

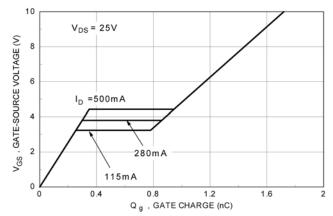

Fig 10 – Gate Charge Characteristics

DISCLAIMER: The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Silicon Supplies Ltd hereby disclaims any and all warranties and liabilities of any kind.

LIFE SUPPORT POLICY: Silicon Supplies Ltd components may be used in life support devices or systems only with the express written approval of Silicon Supplies Ltd, if a failure of such components can reasonably be expected to cause the failure of that life support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.