# MONOLITHIC MANCHESTER ENCODER (SERIES 3D7501)

PACKAGES

## FEATURES

- All-silicon, low-power CMOS technology

- TTL/CMOS compatible inputs and outputs

- Vapor phase, IR and wave solderable

- Auto-insertable (DIP pkg.)

- Low ground bounce noise

- Maximum data rate: 50 MBaud

| CLK                      |   | 1 | $\mathcal{T}$ | 8  |     | VDD |  |

|--------------------------|---|---|---------------|----|-----|-----|--|

| RESB                     |   | 2 |               | 7  |     | N/C |  |

| DAT                      |   | 3 |               | 6  |     | ТХВ |  |

| GND                      |   | 4 |               | 5  |     | ТΧ  |  |

| 3D7501                   | М | D | IP (          | .3 | 00) |     |  |

| 3D7501H Gull Wing (.300) |   |   |               |    |     |     |  |

| 3D7501Z SOIC (.150)      |   |   |               |    |     |     |  |

| CLK                                           |   | 1  | ${14}$  | þ   | VDD |  |

|-----------------------------------------------|---|----|---------|-----|-----|--|

| N/C                                           |   | 2  | 13      | þ   | N/C |  |

| N/C                                           |   | 3  | 12      | þ   | N/C |  |

| RESB                                          |   | 4  | 11      | þ   | N/C |  |

| DAT                                           |   | 5  | 10      | þ   | N/C |  |

| N/C                                           |   | 6  | 9       | þ   | ТХВ |  |

| GND                                           |   | 7  | 8       | þ   | ТΧ  |  |

| 3D7501 DIP (.300)<br>3D7501G Gull Wing (.300) |   |    |         |     |     |  |

| 3D7501                                        | D | SC | DIC (.1 | 150 | )   |  |

### FUNCTIONAL DESCRIPTION

The 3D7501 is a monolithic CMOS Manchester Encoder. The clock and data, present at the unit input, are combined into a single biphase-level signal. In this encoding mode, a logic one is represented by a high-to-low transition within the bit cell, while a logic zero is represented by a low-to-high transition. The unit operating baud rate (in Mbaud) is equal to the input clock frequency (in MHZ). All pins marked N/C must be left unconnected.

#### **PIN DESCRIPTIONS**

| DAT  | Data Input             |

|------|------------------------|

| CLK  | Clock Input            |

| RESB | Reset                  |

| ТΧ   | Signal Output          |

| ТХВ  | Inverted Signal Output |

| VCC  | +5 Volts               |

| GND  | Ground                 |

The all-CMOS 3D7501 integrated circuit has been designed as a reliable, economic alternative to hybrid TTL Manchester Encoder. It is TTL- and CMOS-compatible, capable of driving ten 74LS-type loads. It is offered in standard 8-pin and 14-pin auto-insertable DIPs and space saving surface mount 8-pin and 14-pin SOICs.

## **APPLICATION NOTES**

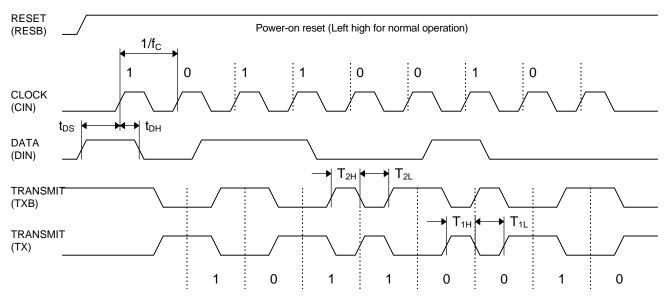

The 3D7501 Manchester Encoder samples the data input at the rising edge of the input clock. The sampled data is used in conjunction with the clock rising and falling edges to generate the by-phase level Manchester code.

#### **INPUT SIGNAL CHARACTERISTICS**

The 3D7501 Manchester Encoder inputs **are TTL compatible. The user should assure himself that** the 1.5 volt TTL threshold is used when referring to all timing, especially to the input clock duty cycle.

### **CLOCK DUTY CYCLE ERRORS**

The 3D7501 Manchester Encoder employs the timing of the clock rising and falling edges (duty cycle) to implement the required coding scheme. To reduce the difference between the output data high time and low time, it is essential that the deviation of the input clock duty cycle from 50/50 be minimized.

#### **OUTPUT SIGNAL CHARACTERISTICS**

The 3D7501 presents at its outputs the true and the complimented encoded data.

The High-to-Low time skew of the selected data output should be budgeted by the user, as it relates to his application, to satisfactorily estimate the distortion of the transmitted data stream.

Such estimate is very useful in determining the functionality and margins of the data link, if a 3D7502 Manchester Decoder is used to decode the received data.

#### POWER SUPPLY AND TEMPERATURE CONSIDERATIONS

CMOS integrated circuitry is strongly dependent on power supply and temperature. The monolithic 3D7501 Manchester encoder utilizes novel and innovative compensation circuitry to minimize timing variations induced by fluctuations in power supply and/or temperature.

Figure 1: Timing Diagram

## **DEVICE SPECIFICATIONS**

#### TABLE 1: ABSOLUTE MAXIMUM RATINGS

| PARAMETER           | SYMBOL            | MIN  | MAX                  | UNITS | NOTES  |

|---------------------|-------------------|------|----------------------|-------|--------|

| DC Supply Voltage   | V <sub>DD</sub>   | -0.3 | 7.0                  | V     |        |

| Input Pin Voltage   | V <sub>IN</sub>   | -0.3 | V <sub>DD</sub> +0.3 | V     |        |

| Input Pin Current   | I <sub>IN</sub>   | -10  | 10                   | mA    | 25C    |

| Storage Temperature | T <sub>STRG</sub> | -55  | 150                  | С     |        |

| Lead Temperature    | T <sub>LEAD</sub> |      | 300                  | С     | 10 sec |

#### TABLE 2: DC ELECTRICAL CHARACTERISTICS (0C to 70C, 4.75V to 5.25V)

| PARAMETER                 | SYMBOL                          | MIN  | MAX | UNITS | NOTES                   |

|---------------------------|---------------------------------|------|-----|-------|-------------------------|

| Static Supply Current*    | I <sub>DD</sub>                 |      | 40  | mA    |                         |

| High Level Input Voltage  | V <sub>IH</sub>                 | 2.0  |     | V     |                         |

| Low Level Input Voltage   | V <sub>IL</sub>                 |      | 0.8 | V     |                         |

| High Level Input Current  | I <sub>IH</sub>                 |      | 1.0 | μΑ    | $V_{IH} = V_{DD}$       |

| Low Level Input Current   | IIL                             |      | 1.0 | μΑ    | $V_{IL} = 0V$           |

| High Level Output Current | I <sub>OH</sub>                 | -4.0 |     | mA    | $V_{DD} = 4.75V$        |

|                           |                                 |      |     |       | $V_{OH} = 2.4 V$        |

| Low Level Output Current  | I <sub>OL</sub>                 | 4.0  |     | mA    | $V_{DD} = 4.75V$        |

|                           |                                 |      |     |       | $V_{OL} = 0.4V$         |

| Output Rise & Fall Time   | T <sub>R</sub> & T <sub>F</sub> |      | 2   | ns    | $C_{LD} = 5 \text{ pf}$ |

\*I<sub>DD</sub>(Dynamic) = 2 \* C<sub>LD</sub> \* V<sub>DD</sub> \* F

where:  $C_{LD}$  = Average capacitance load/pin (pf) F = Input frequency (GHz) Input Capacitance = 10 pf typical Output Load Capacitance ( $C_{LD}$ ) = 25 pf max

## TABLE 3: AC ELECTRICAL CHARACTERISTICS

(-40C to 85C, 4.75V to 5.25V)

| PARAMETER                   | SYMBOL                            | MIN  | TYP | MAX | UNITS | NOTES |

|-----------------------------|-----------------------------------|------|-----|-----|-------|-------|

| Input Baud Rate             | f <sub>BN</sub>                   |      |     | 50  | MBaud |       |

| Clock Frequency             | fc                                |      |     | 50  | MHz   |       |

| Data set-up to clock rising | t <sub>DS</sub>                   | 3.5  |     |     | ns    |       |

| Data hold from clock rising | t <sub>DH</sub>                   | 0    |     |     | ns    |       |

| TX High-Low time skew       | t <sub>1H</sub> - t <sub>1L</sub> | -3.5 |     | 3.5 | ns    | 1     |

| TXB High-Low time skew      | t <sub>2H</sub> - t <sub>2L</sub> | -2.0 |     | 2.0 | ns    | 1     |

| TX - TXB High/Low time skew | t <sub>1H</sub> - t <sub>2L</sub> | -3.0 |     | 3.0 | ns    | 1     |

Notes: 1: Assumes a 50% duty cycle clock input

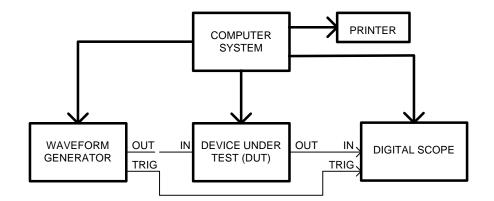

## SILICON DELAY LINE AUTOMATED TESTING

#### **TEST CONDITIONS**

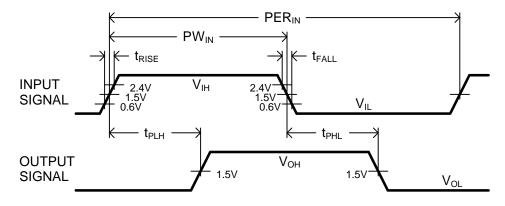

| INPUT:<br>Ambient Temperature:<br>Supply Voltage (Vcc):<br>Input Pulse: | $\begin{array}{l} 5.0V\pm0.1V\\ \text{High}=3.0V\pm0.1V \end{array}$                                                                          | OUTPUT:<br>R <sub>load</sub> :<br>C <sub>load</sub> :<br>Threshold: | $10K\Omega\pm10\%$ 5pf $\pm$ 10% 1.5V (Rising & Falling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Source Impedance:<br>Rise/Fall Time:<br>Pulse Width:<br>Period:         | Low = $0.0V \pm 0.1V$<br>$50\Omega$ Max.<br>3.0 ns Max. (measured<br>between 0.6V and 2.4V )<br>$PW_{IN} = 1/(2*BAUD)$<br>$PER_{IN} = 1/BAUD$ | O<br>Device<br>Under<br>Test                                        | $ \begin{array}{c c}  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & \\  & & & &$ |

**NOTE:** The above conditions are for test only and do not in any way restrict the operation of the device.

Figure 2: Test Setup

Figure 3: Timing Diagram