# **inter<sub>sil</sub>**

## **Radiation Hardened Quad Voltage Comparator**

## HS-139RH, HS-139EH

The Radiation Hardened HS-139RH, HS-139EH consists of four independent single or dual supply voltage comparators on a single monolithic substrate. The common mode input voltage range includes ground, even when operated from a single supply and the low supply current makes these comparators suitable for low power applications. These types were designed to directly interface with TTL and CMOS.

The HS-139RH, HS-139EH is fabricated on our dielectrically isolated Rad Hard Silicon Gate (RSG) process, which provides an immunity to Single Event Latch-up and the capability of highly reliable performance in any radiation environment.

Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed below must be used when ordering.

Detailed Electrical Specifications for the HS-139RH, HS-139EH are contained in <u>SMD 5962-98613</u>. A "hot-link" is provided on our homepage with instructions for downloading. www.intersil.com/spacedefense/newsafclasst.asp

## **Features**

- QML Qualified Per MIL-PRF-38535 Requirements

- Radiation Environment

- Latch-up Free Under any Conditions

- Total Dose (Max)...... 3 x 10<sup>5</sup> RAD(Si)

- Low Dose Rate Effects Immunity

- 100V Output Voltage Withstand Capability

- ESD Protection to >3000V

- Differential Input Voltage Range Equal to the Supply Voltage

- Input Offset Voltage (V<sub>IO</sub>) ..... 2mV (Max)

- Pb-Free (RoHS Compliant)

### Applications

- Pulse Generators

- Timing Circuitry

- Level Shifting

- Analog-to-Digital Conversion

| ORDERING NUMBER<br>(Note) | INTERNAL<br>MKT. NUMBER | PART<br>MARKING    | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PACKAGE<br>DRAWING NUMBER |

|---------------------------|-------------------------|--------------------|---------------------|-----------------------------|---------------------------|

| 5962F9861303VCC           | HS1-139EH-Q             | Q 5962F98 61303VCC | -55 to +125         | 14 Ld SBDIP                 | D14.3                     |

| 5962F9861301VCC           | HS1-139RH-Q             | Q 5962F98 61301VCC | -55 to +125         | 14 Ld SBDIP                 | D14.3                     |

| 5962F9861301QCC           | HS1-139RH-8             | Q 5962F98 61301QCC | -55 to +125         | 14 Ld SBDIP                 | D14.3                     |

| HS1-139RH/PROTO           | HS1-139RH/PROTO         | HS1-139RH/PROTO    | -55 to +125         | 14 Ld SBDIP                 | D14.3                     |

| 5962F9861301VXC           | HS9-139RH-Q             | Q 5962F98 61301VXC | -55 to +125         | 14 Ld FLATPACK              | K14.A                     |

| 5962F9861301QXC           | HS9-139RH-8             | Q 5962F98 61301QXC | -55 to +125         | 14 Ld FLATPACK              | K14.A                     |

| 5962F9861302VXC           | HS9-139EH-Q             | Q 5962F98 61302VXC | -55 to +125         | 14 Ld FLATPACK              | K14.A                     |

| HS9-139RH/PROTO           | HS9-139RH/PROTO         | HS9-139RH /PROTO   | -55 to +125         | 14 Ld FLATPACK              | K14.A                     |

NOTE: These Intersil Pb-free Hermetic packaged products employ 100% Au plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

## **Ordering Information**

1

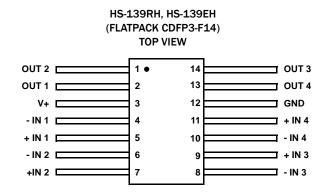

## **Pin Configurations**

## **Die Characteristics**

#### **DIE DIMENSIONS:**

3750µm x 2820µm (148 mils x 111 mils) 483µm  $\pm$ 25.4µm (19 mils  $\pm$ 1 mil)

#### **INTERFACE MATERIALS:**

#### **Glassivation:**

Type: Silox (SiO<sub>2</sub>) Thickness: 8.0kÅ ±1.0kÅ

#### **Top Metallization:**

Type: AlSiCu Thickness: 16.0kÅ ±2kÅ

#### Substrate:

Radiation Hardened Silicon Gate, Dielectric Isolation

#### **Backside Finish:**

Silicon

#### **ASSEMBLY RELATED INFORMATION:**

#### Substrate Potential:

Unbiased (DI)

#### **ADDITIONAL INFORMATION:**

#### Worst Case Current Density:

<2.0 x 10<sup>5</sup> A/cm<sup>2</sup>

#### **Transistor Count:**

49

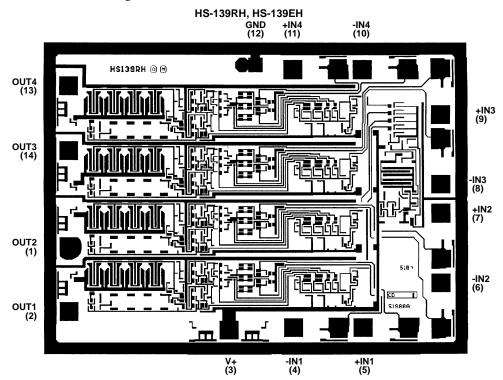

## **Metallization Mask Layout**

TABLE 1. HS-139RH, HS-139EH PAD COORDINATES

|            |          | RELATIVE TO PIN 1 |                  |  |

|------------|----------|-------------------|------------------|--|

| PIN NUMBER | PAD NAME | X<br>COORDINATES  | Y<br>COORDINATES |  |

| 1          | OUT 2    | 0                 | 0                |  |

| 2          | OUT 1    | 0                 | -535             |  |

| 3          | V+       | 1323              | -688             |  |

| 4          | -IN 1    | 1862              | -670             |  |

| 5          | +IN 1    | 2439              | -670             |  |

| 6          | -IN 2    | 3084              | -299             |  |

| 7          | +IN 2    | 3084              | 278              |  |

| 8          | -IN 3    | 3084              | 518              |  |

| 9          | +IN 3    | 3084              | 1095             |  |

| 10         | -IN 4    | 2439              | 1466             |  |

| 11         | +IN 4    | 1862              | 1466             |  |

| 12         | GND      | 1550              | 1503             |  |

| 13         | OUT 4    | 0                 | 1331             |  |

| 14         | OUT 3    | 0                 | 796              |  |

NOTE: Dimensions in microns

For additional products, see www.intersil.com/product\_tree

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com