Data Sheet June 1999 File Number 4739.1

# Radiation Hardened Dual, Non-Inverting Power MOSFET Drivers

The Radiation Hardened HS-4424RH and HS-4424BRH are non-inverting, dual, monolithic high-speed MOSFET drivers designed to convert TTL level signals into high current outputs at voltages up to 18V.

The inputs of these devices are TTL compatible and can be directly driven by our HS-1825ARH PWM device or by our ACS/ACTS and HCS/HCTS type logic devices. The fast rise times and high current outputs allow very quick control of high gate capacitance power MOSFETs, like our Rad Hard FS055, in high frequency applications.

The high current outputs minimize power losses in MOSFETs by rapidly charging and discharging the gate capacitance. The output stage incorporates a low voltage lock-out circuit that puts the outputs into a three-state mode when the supply voltage drops below 10V for the HS-4424RH and 7.5V for the HS-4424BRH.

Constructed with the Intersil dielectrically isolated Rad Hard Silicon Gate (RSG) BiCMOS process, these devices are immune to Single Event Latch-up and have been specifically designed to provide highly reliable performance in harsh radiation environments.

Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering.

Detailed Electrical Specifications for these devices are contained in SMD 5962-99560. A "hot-link" is provided on our homepage for downloading. www.intersil.com/spacedefense/space.asp

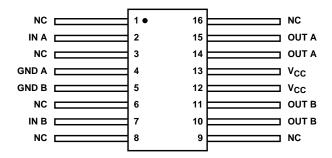

#### **Pinout**

HS-4424RH, HS-4424BRH (FLATPACK CDFP4-F16)

TOP VIEW

NOTE: Pins 4 and 5, 10 and 11, 12 and 13, 14 and 15 are double-bonded to their same electrical points on the die.

#### **Features**

- Electrically Screened to DESC SMD # 5962-99560

- QML Qualified per MIL-PRF-38535 Requirements

- Radiation Environment

- Total Dose (Max)......3 x 10<sup>5</sup> RAD(SI)

- Latch-Up Immune

- Low Dose Rate Immune

- I<sub>PEAK</sub> .....>2A (Min)

- Matched Rise and Fall Times (C<sub>1</sub> = 4300pF)...75ns (Max)

- · Low Voltage Lock-Out Feature

- Consistent Delay Times with V<sub>CC</sub> Changes

- · Low Power Consumption

- 40mW with Inputs High

- 20mW with Inputs Low

## **Applications**

- Switching Power Supplies

- DC/DC Converters

- Motor Controllers

## Ordering Information

| ORDERING NUMBER   | INTERNAL<br>MKT. NUMBER | TEMP. RANGE<br>(°C) |

|-------------------|-------------------------|---------------------|

| 5962F9956001VXC   | HS9-4424RH-Q            | -55 to 125          |

| 5962F9956001QXC   | HS9-4424RH-8            | -55 to 125          |

| HS9-4424RH/Proto  | HS9-4424RH/Proto        | -55 to 125          |

| 5962F9956002VXC   | HS9-4424BRH-Q           | -55 to 125          |

| 5962F9956002QXC   | HS9-4424BRH-8           | -55 to 125          |

| HS9-4424BRH/Proto | HS9-4424BRH/Proto       | -55 to 125          |

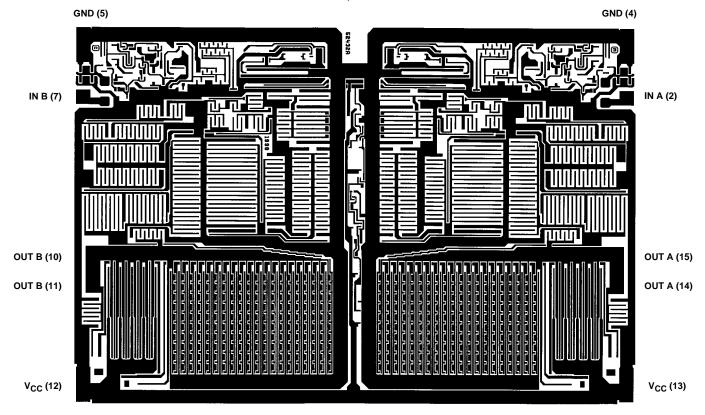

### Die Characteristics

**DIE DIMENSIONS:**

$4890\mu m$  x  $3370\mu m$  (193 mils x 133 mils) Thickness:  $483\mu m \pm 25.4\mu m$  (19 mils  $\pm$  1 mil)

**INTERFACE MATERIALS:**

Glassivation:

Type: PSG (Phosphorous Silicon Glass)

Thickness: 8.0kÅ ± 1.0kÅ

**Top Metallization:**

Type: AlSiCu

Thickness:  $16.0 \text{kÅ} \pm 2 \text{kÅ}$

Substrate:

Radiation Hardened Silicon Gate,

Dielectric Isolation

**Backside Finish:**

Silicon

**ASSEMBLY RELATED INFORMATION:**

**Substrate Potential:**

Unbiased (DI)

**ADDITIONAL INFORMATION:**

**Worst Case Current Density:**

$< 2.0 \times 10^{5} \text{ A/cm}^{2}$

**Transistor Count:**

125

## Metallization Mask Layout

HS-4424RH, HS-4424BRH

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com