74F378 Parallel D-Type Register with Enable

## FAIRCHILD

SEMICONDUCTOR

### 74F378 Parallel D-Type Register with Enable

#### **General Description**

The 74F378 is a 6-bit register with a buffered common Enable. This device is similar to the 74F174, but with common Enable rather than common Master Reset.

#### Features

- 6-bit high-speed parallel register

- Positive edge-triggered D-type inputs

- Fully buffered common clock and enable inputs

- Input clamp diodes limit high-speed termination effects

- Full TTL and CMOS compatible

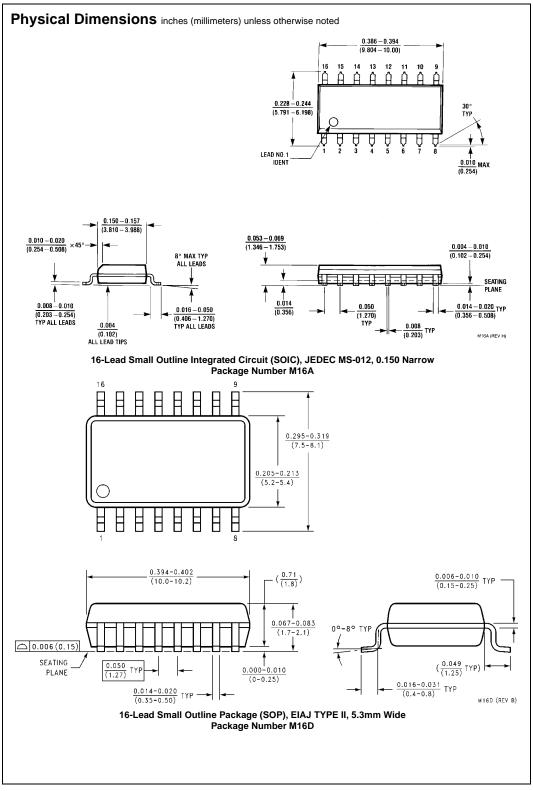

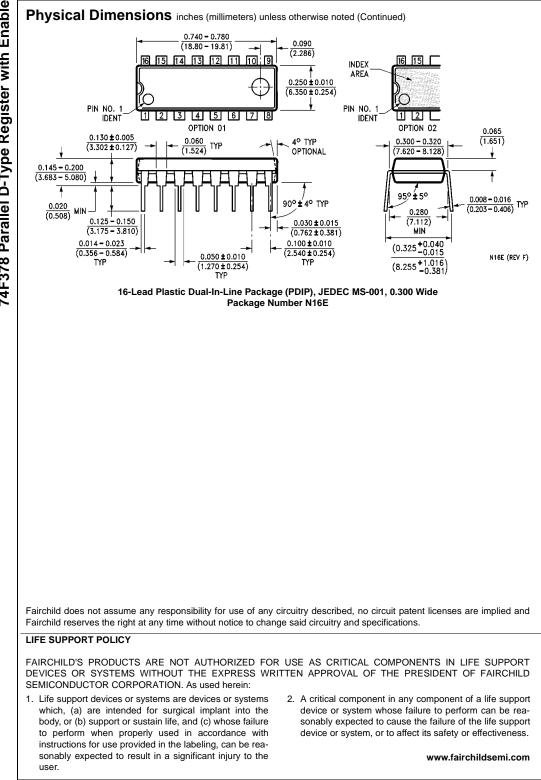

#### **Ordering Code:**

| M16A | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

|------|-----------------------------------------------------------------------------|

|      |                                                                             |

| M16D | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

| N16E | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

| [a   |                                                                             |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code

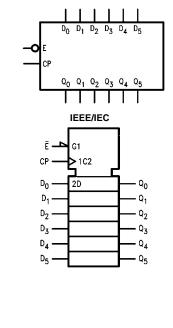

#### **Logic Symbols**

### **Connection Diagram**

|                  |   |            | -  |                  |

|------------------|---|------------|----|------------------|

| Ē-               | 1 | $\bigcirc$ | 16 | -v <sub>cc</sub> |

| Q0-              | 2 |            | 15 | — Q <sub>5</sub> |

| D <sub>0</sub> - | 3 |            | 14 | — D <sub>5</sub> |

| D <sub>1</sub> - | 4 |            | 13 | -D4              |

| Q <sub>1</sub> — | 5 |            | 12 | —Q4              |

| D <sub>2</sub> - | 6 |            | 11 | -D <sub>3</sub>  |

| Q2-              | 7 |            | 10 | -Q3              |

| GND -            | 8 |            | 9  | — CP             |

|                  |   |            |    |                  |

#### © 1999 Fairchild Semiconductor Corporation DS009526

74F378

#### **Unit Loading/Fan Out**

|                                |                                        | U.L.     | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |  |

|--------------------------------|----------------------------------------|----------|-----------------------------------------|--|--|

| Pin Names                      | Description                            | HIGH/LOW | Output I <sub>OH</sub> /I <sub>OL</sub> |  |  |

| Ē                              | Enable Input (Active LOW)              | 1.0/1.0  | 20 μA/–0.6 mA                           |  |  |

| D <sub>0</sub> -D <sub>5</sub> | Data Inputs                            | 1.0/1.0  | 20 μA/–0.6 mA                           |  |  |

| CP                             | Clock Pulse Input (Active Rising Edge) | 1.0/1.0  | 20 µA/–0.6 mA                           |  |  |

| $Q_0 - Q_5$                    | Outputs                                | 50/33.3  | –1 mA/20 mA                             |  |  |

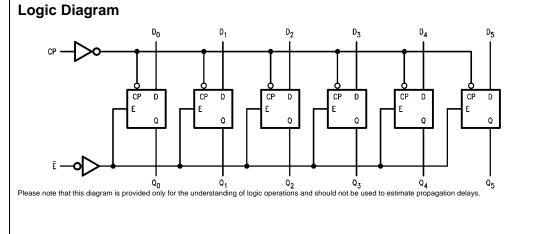

#### **Functional Description**

# The 74F378 consists of six edge-triggered D-type flip-flops with individual D inputs and Q inputs. The Clock (CP) and Enable $(\overline{E})$ inputs are common to all flip-flops.

When the  $\overline{\mathsf{E}}$  input is LOW, new data is entered into the register on the LOW-to-HIGH transition of the CP input. When the  $\overline{E}$  input is HIGH the register will retain the present data independent of the CP input.

#### **Truth Table**

|   | Inputs |                | Output         |

|---|--------|----------------|----------------|

| Ē | СР     | D <sub>n</sub> | Q <sub>n</sub> |

| н | ~      | Х              | No Change      |

| L | ~      | н              | н              |

| L | ~      | L              | L              |

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

#### Absolute Maximum Ratings(Note 1)

Storage Temperature Ambient Temperature under Bias Junction Temperature under Bias  $V_{CC}$  Pin Potential to Ground Pin Input Voltage (Note 2) Input Current (Note 2) Voltage Applied to Output in HIGH State (with  $V_{CC} = 0V$ ) Standard Output 3-STATE Output Current Applied to Output in LOW State (Max) -65°C to +150°C -55°C to +125°C -55°C to +150°C -0.5V to +7.0V -0.5V to +7.0V -30 mA to +5.0 mA

-0.5V to V<sub>CC</sub>

-0.5V to +5.5V

twice the rated I<sub>OL</sub> (mA)

# Recommended Operating Conditions

Free Air Ambient Temperature Supply Voltage

0°C to +70°C

74F378

+4.5V to +5.5V

**Note 1:** Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

| Symbol           | Parameter                                | Min              | Тур | Max  | Units | V <sub>cc</sub> | Conditions                                           |

|------------------|------------------------------------------|------------------|-----|------|-------|-----------------|------------------------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                       | 2.0              |     |      | V     |                 | Recognized as a HIGH Signa                           |

| VIL              | Input LOW Voltage                        |                  |     | 0.8  | V     |                 | Recognized as a LOW Signal                           |

| V <sub>CD</sub>  | Input Clamp Diode Voltage                |                  |     | -1.2 | V     | Min             | I <sub>IN</sub> = -18 mA                             |

| V <sub>OH</sub>  | Output HIGH 10% V <sub>C</sub>           | <sub>C</sub> 2.5 |     |      | V     | Min             | I <sub>OH</sub> = -1 mA                              |

|                  | Voltage 5% V <sub>C</sub>                | 2.7              |     |      |       |                 | $I_{OH} = -1 \text{ mA}$                             |

| V <sub>OL</sub>  | Output LOW 10% V <sub>C</sub><br>Voltage | c                |     | 0.5  | V     | Min             | I <sub>OL</sub> = 20 mA                              |

| Ι <sub>ΙΗ</sub>  | Input HIGH<br>Current                    |                  |     | 5.0  | μΑ    | Max             | V <sub>IN</sub> = 2.7V                               |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test     |                  |     | 7.0  | μΑ    | Max             | V <sub>IN</sub> = 7.0V                               |

| ICEX             | Output HIGH<br>Leakage Current           |                  |     | 50   | μΑ    | Max             | V <sub>OUT</sub> = V <sub>CC</sub>                   |

| V <sub>ID</sub>  | Input Leakage<br>Test                    | 4.75             |     |      | v     | 0.0             | I <sub>ID</sub> = 1.9 μA<br>All Other Pins Grounded  |

| I <sub>OD</sub>  | Output Leakage<br>Circuit Current        |                  |     | 3.75 | μΑ    | 0.0             | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded |

| Ι <sub>ΙL</sub>  | Input LOW Current                        |                  |     | -0.6 | mA    | Max             | $V_{IN} = 0.5V$                                      |

| los              | Output Short-Circuit Current             | -60              |     | -150 | mA    | Max             | V <sub>OUT</sub> = 0V                                |

| I <sub>CCL</sub> | Power Supply Current                     |                  | 30  | 45   | mA    | Max             | $V_{O} = LOW$                                        |

#### **DC Electrical Characteristics**

|                  |                         |     | $T_{A} = +25^{\circ}C$ $V_{CC} = +5.0V$ |     |     | $T_A = -55^{\circ}C \text{ to } +125^{\circ}C$<br>$V_{CC} = +5.0V$ |     | $T_A = 0^\circ C \text{ to } +70^\circ C$<br>$V_{CC} = +5.0V$ |    |

|------------------|-------------------------|-----|-----------------------------------------|-----|-----|--------------------------------------------------------------------|-----|---------------------------------------------------------------|----|

| Symbol           | Parameter               |     | С <sub>С</sub> = 50 рF                  |     |     | $C_L = 50 \text{ pF}$                                              |     | $C_L = 50 \text{ pF}$                                         |    |

|                  |                         | Min | Тур                                     | Max | Min | Max                                                                | Min | Max                                                           |    |

| f <sub>MAX</sub> | Maximum Input Frequency | 80  | 100                                     |     | 70  |                                                                    | 80  |                                                               | MH |

| t <sub>PLH</sub> | Propagation Delay       | 3.0 | 5.5                                     | 7.5 | 3.0 | 10.0                                                               | 3.0 | 8.5                                                           |    |

| t <sub>PHL</sub> | CP to Q <sub>n</sub>    | 3.5 | 6.0                                     | 8.5 | 3.5 | 10.5                                                               | 3.5 | 9.5                                                           | ns |

# AC Operating Requirements

|                    |                         | <b>T</b> <sub>A</sub> = + | $T_A = +25^{\circ}C$<br>$V_{CC} = +5.0V$ |      | $T_{A} = -55^{\circ}C \text{ to } +125^{\circ}C$ $V_{CC} = +5.0V$ |      | $T_A = 0^\circ C \text{ to } +70^\circ C$<br>$V_{CC} = +5.0V$ |    |  |

|--------------------|-------------------------|---------------------------|------------------------------------------|------|-------------------------------------------------------------------|------|---------------------------------------------------------------|----|--|

| Symbol             | Parameter               | V <sub>CC</sub> =         |                                          |      |                                                                   |      |                                                               |    |  |

|                    |                         | Min                       | Max                                      | Min  | Max                                                               | Min  | Max                                                           |    |  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW | 4.0                       |                                          | 5.0  |                                                                   | 4.0  |                                                               |    |  |

| t <sub>S</sub> (L) | D <sub>n</sub> to CP    | 4.0                       |                                          | 5.0  |                                                                   | 4.0  |                                                               | 20 |  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW  | 0                         |                                          | 2.0  |                                                                   | 0    |                                                               | ns |  |

| t <sub>H</sub> (L) | D <sub>n</sub> to CP    | 0                         |                                          | 2.0  |                                                                   | 0    |                                                               |    |  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW | 6.0                       |                                          | 4.5  |                                                                   | 6.0  |                                                               |    |  |

| t <sub>S</sub> (L) | E to CP                 | 10.0                      |                                          | 13.0 |                                                                   | 10.0 |                                                               |    |  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW  | 0                         |                                          | 0    |                                                                   | 0    |                                                               | ns |  |

| t <sub>H</sub> (L) | E to CP                 | 0                         |                                          | 0    |                                                                   | 0    |                                                               |    |  |

| t <sub>W</sub> (H) | CP Pulse Width          | 4.0                       |                                          | 5.0  |                                                                   | 4.0  |                                                               |    |  |

| t <sub>W</sub> (L) | HIGH or LOW             | 6.0                       |                                          | 7.5  |                                                                   | 6.0  |                                                               | ns |  |

www.fairchildsemi.com

74F378

74F378 Parallel D-Type Register with Enable