#### FAIRCHILD

SEMICONDUCTOR

### 74F524 8-Bit Registered Comparator

#### **General Description**

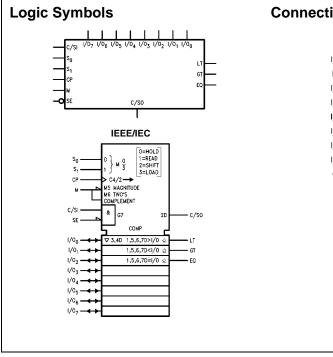

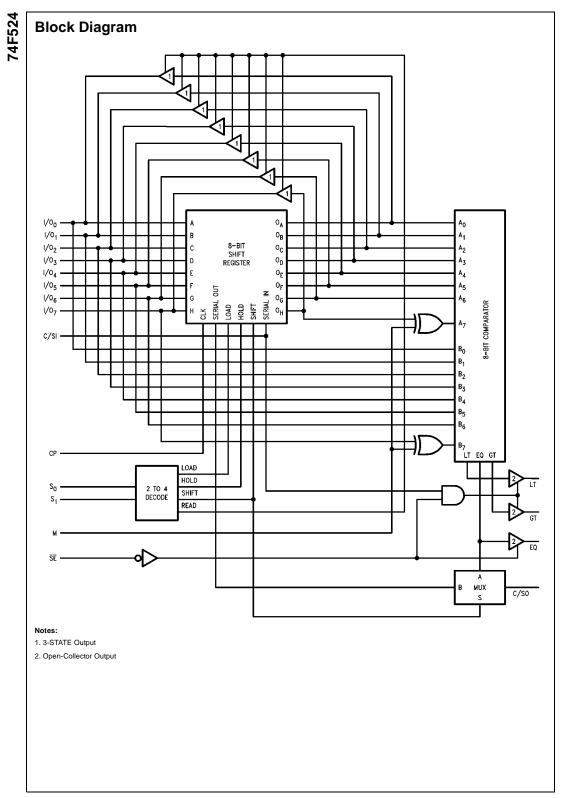

The 74F524 is an 8-bit bidirectional register with parallel input and output plus serial input and output progressing from LSB to MSB. All data inputs, serial and parallel, are loaded by the rising edge of the input clock. The device functions are controlled by two control lines (S<sub>0</sub>, S<sub>1</sub>) to execute shift, load, hold and read out.

An 8-bit comparator examines the data stored in the registers and on the data bus. Three true-HIGH, open-collector outputs representing "register equal to bus", "register greater than bus" and "register less than bus" are provided. These outputs can be disabled to the OFF state by the use of Status Enable ( $\overline{SE}$ ). A mode control has also been provided to allow twos complement as well as magnitude compare. Linking inputs are provided for expansion to longer words.

#### Features

■ 8-Bit bidirectional register with bus-oriented input-output

April 1988

Revised August 1999

- Independent serial input-output to register

- Register bus comparator with "equal to", "greater than" and "less than" outputs

- Cascadable in groups of eight bits

- Open-collector comparator outputs for AND-wired expansion

- Twos complement or magnitude compare

#### **Ordering Code:**

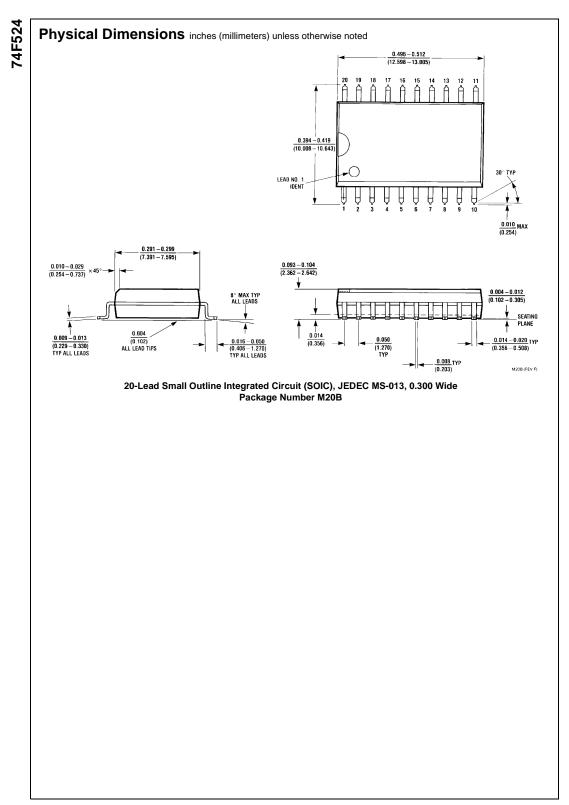

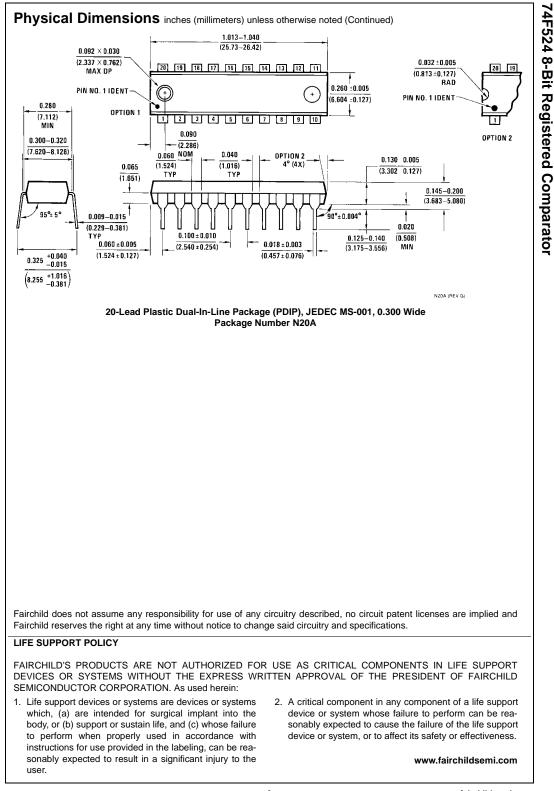

| Order Number | Package Number | Package Description                                                       |

|--------------|----------------|---------------------------------------------------------------------------|

| 74F524SC     | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

| 74F524PC     | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide     |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

#### **Connection Diagram**

© 1999 Fairchild Semiconductor Corporation DS009546

# 74F524

#### Unit Loading/Fan Out

| Dia Manag                          | Description                            | U.L.              | Input I <sub>IH</sub> /I <sub>IL</sub>  |

|------------------------------------|----------------------------------------|-------------------|-----------------------------------------|

| Pin Names                          | Description                            | HIGH/LOW          | Output I <sub>OH</sub> /I <sub>OL</sub> |

| S <sub>0</sub> , S <sub>1</sub>    | Mode Select Inputs                     | 1.0/1.0           | 20 μA/–0.6 mA                           |

| C/SI                               | Status Priority or Serial Data Input   | 1.0/1.0           | 20 µA/–0.6 mA                           |

| СР                                 | Clock Pulse Input (Active Rising Edge) | 1.0/1.0           | 20 µA/–0.6 mA                           |

| SE                                 | Status Enable Input (Active LOW)       | 1.0/1.0           | 20 µA/–0.6 mA                           |

| М                                  | Compare Mode Select Input              | 1.0/1.0           | 20 µA/–0.6 mA                           |

| I/O <sub>0</sub> –I/O <sub>7</sub> | Parallel Data Inputs or                | 3.5/1.083         | 70 μA/–0.65 mA                          |

|                                    | 3-STATE Parallel Data Outputs          | 150/40 (33.3)     | –3 mA/24 mA (20 mA)                     |

| C/SO                               | Status Priority or Serial Data Output  | 50/33.3           | -1 mA/20 mA                             |

| LT                                 | Register Less Than Bus Output          | OC (Note 1) /33.3 | (Note 1) /20 mA                         |

| EQ                                 | Register Equal Bus Output              | OC(Note 1) /33.3  | (Note 1) /20 mA                         |

| GT                                 | Register Greater Than Bus Output       | OC(Note 1) /33.3  | (Note 1) /20 mA                         |

Note 1: OC = Open Collector

#### **Number Representation Select Table**

| Μ | Operation               |  |

|---|-------------------------|--|

| L | Magnitude Compare       |  |

| Н | Twos Complement Compare |  |

#### Select Truth Table

| S <sub>0</sub> | S <sub>1</sub> | Operation                                              |

|----------------|----------------|--------------------------------------------------------|

| L              | L              | Hold—Retains Data in Shift Register                    |

| L              | н              | Read—Read Contents in Register onto Data Bus,          |

|                |                | Data Remains in Register Unaffected by Clock           |

| н              | L              | Shift—Allows Serial Shifting on Next Rising Clock Edge |

| Н              | Н              | Load—Load Data on Bus into Register                    |

#### **Status Truth Table**

(Hold Mode)

|    | Inputs               |                                                                     |    | Outputs |    |      |  |  |  |

|----|----------------------|---------------------------------------------------------------------|----|---------|----|------|--|--|--|

| SE | C/SI Data Comparison |                                                                     | EQ | GT      | LT | C/SO |  |  |  |

| Н  | н                    | Х                                                                   | н  | н       | н  | 1    |  |  |  |

| L  | L                    | $O_{A} - O_{H} > I/O_{0} - I/O_{7}$                                 | L  | н       | н  | L    |  |  |  |

| Х  | L                    | $O_A - O_H = I / O_0 - I / O_7$                                     | н  | н       | н  | L    |  |  |  |

| н  | L                    | $O_A - O_H < I / O_0 - I / O_7$                                     | L  | н       | н  | L    |  |  |  |

| н  | н                    | $O_{A} - O_{H} > I/O_{0} - I/O_{7}$                                 | L  | н       | L  | L    |  |  |  |

| н  | н                    | $O_A - O_H = I / O_0 - I / O_7$                                     | н  | L       | L  | Н    |  |  |  |

| L  | н                    | 0 <sub>A</sub> -0 <sub>H</sub> < I/0 <sub>0</sub> -I/0 <sub>7</sub> | L  | L       | н  | L    |  |  |  |

1 = HIGH if data are equal, otherwise LOW H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

#### **Functional Description**

The 74F524 contains eight D-type flip-flops connected as a shift register with provision for either parallel or serial loading. Parallel data may be read from or loaded into the registers via the data bus  $I/O_0$ - $I/O_7$ . Serial data is entered from the C/SI input and may be shifted into the register and out through the C/SO output. Both parallel and serial data entry occur on the rising edge of the input clock (CP). The operation of the shift register is controlled by two signals S<sub>0</sub> and S<sub>1</sub> according to the Select Truth Table. The 3-STATE paral-

lel output buffers are enabled only in the Read mode.

One port of an 8-bit comparator is attached to the data bus while the other port is tied to the outputs of the internal register. Three active-OFF, open-collector outputs indicate whether the contents held in the shift register are "greater than", (GT), "less than" (LT), or "equal to" (EQ) the data on the input bus. A HIGH signal on the Status Enable ( $\overline{SE}$ ) input disables these outputs to the OFF state. A mode control input (M) allows selection between a straightforward magnitude compare or a comparison between twos complement numbers.

For "greater than" or "less than" detection, the C/SI input must be held HIGH, as indicated in the Status Truth Table. The internal logic is arranged such that a LOW signal on the C/SI input disables the "greater than" and "less than" outputs. The C/SO output will be forced HIGH if the "equal to" status condition exists, otherwise C/SO will be held LOW. These facilities enable the 74F524 to be cascaded for word length greater than eight bits.

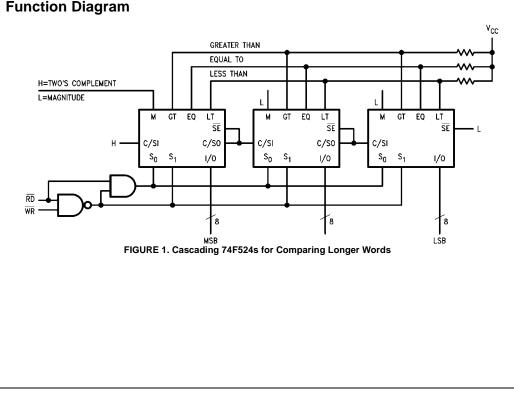

Word length expansion (in groups of eight bits) can be achieved by connecting the C/SO output of the more significant byte to the C/SI input of the next less significant byte and also to its own  $\overline{SE}$  input (see Figure 1). The C/SI input of the most significant device is held HIGH while the  $\overline{SE}$ input of the least significant device is held LOW. The corresponding status outputs are AND-wired together. In the case of twos complement number compare, only the Mode input to the most significant device should be HIGH. The Mode inputs to all other cascaded devices are held LOW.

Suppose that an inequality condition is detected in the most significant device. Assuming that the byte stored in the register is greater than the byte on the data bus, the EQ and LT outputs will be pulled LOW and the GT output will float HIGH. Also the C/SO output of the most significant device will be forced LOW, disabling the subsequent devices but enabling its own status outputs. The correct status condition is thus indicated. The same applies if the registered byte is less than the data byte, only in this case the EQ and GT outputs go LOW and LT output floats HIGH. If an equality condition is detected in the most significant device, its C/SO output is forced HIGH. This enables the next less significant device and also disables its own status outputs. In this way, the status output priority is handed down to the next less significant device which now effectively becomes the most significant byte. The worst case propagation delay for a compare operation involving "n" cascaded 74F524s will be when an equality condition is detected in all but the least significant byte. In this case, the status priority has to ripple all the way down the chain before the correct status output is established. Typically, this will take 35 + 6(n-2) ns.

www.fairchildsemi.com

4

#### Absolute Maximum Ratings(Note 2)

Storage Temperature Ambient Temperature under Bias Junction Temperature under Bias  $V_{CC}$  Pin Potential to Ground Pin Input Voltage (Note 3) Input Current (Note 3) Voltage Applied to Output in HIGH State (with  $V_{CC} = 0V$ ) Standard Output 3-STATE Output Current Applied to Output in LOW State (Max)

-65°C to +150°C -55°C to +125°C -55°C to +150C -0.5V to +7.0V -0.5V to +7.0V -30 mA to +5.0 mA

-0.5V to V<sub>CC</sub>

-0.5V to +5.5V

twice the rated  $I_{OL}$  (mA)

## Recommended Operating Conditions

Free Air Ambient Temperature Supply Voltage

0°C to +70°C +4.5V to +5.5V 74F524

**Note 2:** Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

| Symbol                             | Parar                | neter               | Min  | Тур | Max  | Units | Vcc   | Conditions                                |

|------------------------------------|----------------------|---------------------|------|-----|------|-------|-------|-------------------------------------------|

| VIH                                | Input HIGH Voltage   |                     | 2.0  |     |      | V     |       | Recognized as a HIGH Signal               |

| VIL                                | Input LOW Voltage    |                     |      |     | 0.8  | V     |       | Recognized as a LOW Signal                |

| V <sub>CD</sub>                    | Input Clamp Diode \  | /oltage             |      |     | -1.2 | V     | Min   | I <sub>IN</sub> = -18 mA                  |

| V <sub>OH</sub>                    | Output HIGH          | 10% V <sub>CC</sub> | 2.5  |     |      |       |       | I <sub>OH</sub> = -1 mA                   |

|                                    | Voltage              | 10% V <sub>CC</sub> | 2.4  |     |      | v     | Min   | $I_{OH} = -3 \text{ mA}$                  |

|                                    |                      | 5% V <sub>CC</sub>  | 2.7  |     |      | v     | IVIIN | $I_{OH} = -1 \text{ mA}$                  |

|                                    |                      | 5% V <sub>CC</sub>  | 2.7  |     |      |       |       | $I_{OH} = -3 \text{ mA}$                  |

| V <sub>OL</sub>                    | Output LOW           | 10% V <sub>CC</sub> |      |     | 0.5  |       |       | $I_{OL} = 20 \text{ mA} (I/O_n)$          |

|                                    | Voltage              | 10% V <sub>CC</sub> |      |     | 0.5  | V     | Min   | I <sub>OL</sub> = 24 mA (LT, GT, EQ, C/SC |

| I <sub>IH</sub>                    | Input HIGH Current   |                     |      |     | 5.0  | μΑ    | Max   | V <sub>IN</sub> = 2.7V                    |

| I <sub>BVI</sub>                   | Input HIGH Current   |                     |      |     | 7.0  |       | Maria | V <sub>IN</sub> = 7.0V                    |

|                                    | Breakdown Test       |                     |      |     | 7.0  | μA    | Max   |                                           |

| ICEX                               | Output HIGH          |                     |      |     | 50   |       | Мах   | $V_{OUT} = V_{CC} (I/O_n, C/SO)$          |

|                                    | Leakage Current      |                     |      |     | 50   | μA    | IVIAX |                                           |

| V <sub>ID</sub>                    | Input Leakage        |                     | 4.75 |     |      | v     | 0.0   | I <sub>ID</sub> = 1.9 μA                  |

|                                    | Test                 |                     | 4.75 |     |      | v     | 0.0   | All Other Pins Grounded                   |

| I <sub>OD</sub>                    | Output Leakage       |                     |      |     | 3.75 |       | A 0.0 | V <sub>IOD</sub> = 150 mV                 |

|                                    | Circuit Current      |                     |      |     | 3.75 | μA    | 0.0   | All Other Pins Grounded                   |

| IIL                                | Input LOW Current    |                     |      |     | -0.6 | mA    | Max   | $V_{IN} = 0.5V$                           |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Cur   | rrent               |      |     | 70   | μΑ    | Max   | $V_{I/O} = 2.7V$                          |

| I <sub>IL</sub> + I <sub>OZL</sub> | Output Leakage Cur   | rrent               |      |     | -650 | μΑ    | Max   | $V_{I/O} = 0.5V$                          |

| los                                | Output Short-Circuit | Current             | -60  |     | -150 | mA    | Max   | $V_{OUT} = 0V$                            |

| I <sub>OHC</sub>                   | Open Collector, Out  | put                 |      |     | 250  |       | Min   | V – V                                     |

|                                    | OFF Leakage Test     |                     |      |     | 250  | μA    | IVIIN | $V_{OUT} = V_{CC}$                        |

| ICCH                               | Power Supply Curre   | ent                 |      | 128 | 180  | mA    | Max   | V <sub>O</sub> = HIGH                     |

| I <sub>CCL</sub>                   | Power Supply Curre   | ent                 |      | 128 | 180  | mA    | Max   | $V_0 = LOW$                               |

| I <sub>CCZ</sub>                   | Power Supply Curre   | ent                 | 1    | 128 | 180  | mA    | Max   | $V_{O} = HIGH Z$                          |

#### **DC Electrical Characteristics**

| Symbol                               | Parameter                                                  |              | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = +5.0V$ $C_{L} = 50 \text{ pF}$ |              | Unit         |              |     |

|--------------------------------------|------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------|--------------|--------------|--------------|-----|

|                                      |                                                            | Min          | Тур                                                                                    | Max          | Min          | Max          |     |

| f <sub>MAX</sub>                     | Maximum Shift Frequency                                    | 50           | 75                                                                                     |              | 50           |              | MF  |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 9.0          | 16.5                                                                                   | 20.0         | 9.0          | 21.0         |     |

| t <sub>PHL</sub>                     | I/O <sub>n</sub> to EQ                                     | 5.0          | 9.5                                                                                    | 12.0         | 5.0          | 13.0         |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 8.5          | 14.1                                                                                   | 19.0         | 8.5          | 20.0         | ns  |

| t <sub>PHL</sub>                     | I/O <sub>n</sub> to GT                                     | 6.5          | 13.0                                                                                   | 16.5         | 6.5          | 17.5         |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 7.0          | 15.5                                                                                   | 20.0         | 7.0          | 21.0         |     |

| t <sub>PHL</sub>                     | I/O <sub>n</sub> to LT                                     | 4.5          | 10.0                                                                                   | 14.0         | 4.5          | 15.0         |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 8.0          | 15.2                                                                                   | 19.5         | 8.0          | 20.5         | ns  |

| t <sub>PHL</sub>                     | I/O <sub>n</sub> to C/SO                                   | 6.0          | 12.5                                                                                   | 16.0         | 6.0          | 17.0         |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 10.0         | 20.0                                                                                   | 25.0         | 10.0         | 26.0         |     |

| t <sub>PHL</sub>                     | CP to EQ                                                   | 4.0          | 8.5                                                                                    | 16.5         | 4.0          | 17.5         | -   |

| t <sub>PLH</sub>                     | Propagation Delay<br>CP to GT                              | 10.0         | 16.5                                                                                   | 21.0         | 10.0         | 22.0         | ns  |

| t <sub>PHL</sub>                     |                                                            | 8.5          | 17.0                                                                                   | 22.0         | 8.5          | 23.0         |     |

| t <sub>PLH</sub>                     | Propagation Delay<br>CP to LT                              | 9.0          | 20.0<br>13.5                                                                           | 25.0<br>17.0 | 9.0          | 26.0<br>18.0 |     |

| t <sub>PHL</sub>                     | Propagation Delay                                          | 5.5          | 13.0                                                                                   | 17.0         | 5.5          | 16.0         |     |

| t <sub>PLH</sub>                     | CP to C/SO (Load)                                          | 8.5          | 16.5                                                                                   | 21.0         | 8.5          | 22.0         | n   |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 5.0          | 10.0                                                                                   | 13.0         | 5.0          | 14.0         | 112 |

| t <sub>PHL</sub>                     | CP to C/SO (Serial Shift)                                  | 4.5          | 9.0                                                                                    | 11.5         | 4.5          | 12.5         |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 9.0          | 15.0                                                                                   | 19.0         | 9.0          | 20.0         |     |

| t <sub>PHL</sub>                     | C/SI to GT                                                 | 3.0          | 6.5                                                                                    | 8.5          | 3.0          | 9.5          | ns  |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 8.0          | 15.5                                                                                   | 20.0         | 8.0          | 21.0         |     |

| t <sub>PHL</sub>                     | C/SI to LT                                                 | 3.5          | 6.5                                                                                    | 8.5          | 3.5          | 9.5          |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 6.5          | 11.5                                                                                   | 14.5         | 6.5          | 15.5         | ns  |

| t <sub>PHL</sub>                     | S <sub>0</sub> , S <sub>1</sub> to C/SO                    | 5.5          | 14.0                                                                                   | 18.0         | 5.5          | 19.0         |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 3.5          | 8.0                                                                                    | 10.5         | 3.5          | 11.5         |     |

| t <sub>PHL</sub>                     | SE to EQ                                                   | 2.5          | 6.0                                                                                    | 8.0          | 2.5          | 9.0          |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 6.5          | 12.5                                                                                   | 16.0         | 6.5          | 17.0         | ns  |

| t <sub>PHL</sub>                     | SE to GT                                                   | 3.5          | 6.0                                                                                    | 8.0          | 3.5          | 9.0          |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 5.0          | 10.5                                                                                   | 13.5         | 5.0          | 14.5         |     |

| t <sub>PHL</sub>                     | SE to LT                                                   | 3.5          | 6.0                                                                                    | 8.0          | 3.5          | 9.0          |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 4.0          | 8.5                                                                                    | 11.0         | 4.0          | 12.0         | ns  |

| t <sub>PHL</sub>                     | C/SI to C/SO                                               | 4.0          | 8.5                                                                                    | 11.0         | 4.0          | 12.0         |     |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 8.0          | 15.0                                                                                   | 19.5         | 8.0          | 20.5         |     |

| t <sub>PHL</sub>                     | M to GT                                                    | 6.0          | 12.0                                                                                   | 17.5         | 6.0          | 18.5         | ns  |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 8.0          | 17.0                                                                                   | 22.0         | 8.0          | 23.0         |     |

| t <sub>PHL</sub>                     | M to LT<br>Propagation Delay                               | 4.5          | 9.5                                                                                    | 12.0         | 4.5          | 13.0         |     |

| t <sub>PLH</sub>                     |                                                            | 15.0         | 25.0<br>15.0                                                                           | 33.0<br>19.0 | 15.0         | 35.0         |     |

| t <sub>PHL</sub>                     | S <sub>0</sub> , S <sub>1</sub> to EQ                      | 9.0          | 15.0                                                                                   | 19.0         | 9.0          | 20.0         | -   |

| t <sub>PLH</sub>                     | Propagation Delay                                          | 10.5<br>10.5 | 18.0                                                                                   | 23.0<br>23.0 | 10.5<br>10.5 | 24.0<br>24.0 | ns  |

| t <sub>PHL</sub>                     | S <sub>0</sub> , S <sub>1</sub> to GT<br>Propagation Delay | 13.0         | 22.0                                                                                   | 23.0         | 13.0         | 30.0         | -   |

| t <sub>PLH</sub>                     | $S_0, S_1$ to LT                                           | 13.0         | 19.0                                                                                   | 28.0         | 13.0         | 25.0         |     |

|                                      | Output Enable Time                                         | 4.5          | 19.0                                                                                   | 13.0         | 4.5          | 14.0         |     |

| t <sub>PZH</sub>                     | $S_0, S_1$ to I/O <sub>n</sub>                             | 5.5          | 11.0                                                                                   | 15.0         | 4.5<br>5.5   | 14.0         |     |

| t <sub>PZL</sub><br>t <sub>PHZ</sub> | Output Disable Time                                        | 3.5          | 8.0                                                                                    | 12.0         | 3.5          | 13.0         | ns  |

| чрни<br>t <sub>PLZ</sub>             | $S_0, S_1$ to $I/O_n$                                      | 4.5          | 9.6                                                                                    | 12.5         | 4.5          | 13.5         |     |

| Symbol             |                                        | T <sub>A</sub> = +25°C | T <sub>A</sub> = 0°C to | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$<br>$V_{CC} = +5.0V$ |    |

|--------------------|----------------------------------------|------------------------|-------------------------|-----------------------------------------------------------------|----|

|                    | Parameter                              | $V_{CC} = +5.0V$       | V <sub>CC</sub> = +     |                                                                 |    |

|                    |                                        | Min Ma                 | x Min                   | Max                                                             |    |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                | 6.0                    | 6.0                     |                                                                 |    |

| t <sub>S</sub> (L) | I/O <sub>n</sub> to CP                 | 6.0                    | 6.0                     |                                                                 |    |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                 | 0                      | 0                       |                                                                 | ns |

| t <sub>H</sub> (L) | I/O <sub>n</sub> to CP                 | 0                      | 0                       |                                                                 |    |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                | 10.0                   | 10.0                    |                                                                 |    |

| t <sub>S</sub> (L) | S <sub>0</sub> or S <sub>1</sub> to CP | 10.0                   | 10.0                    |                                                                 |    |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                 | 0                      | 0                       |                                                                 | ns |

| t <sub>H</sub> (L) | S <sub>0</sub> or S <sub>1</sub> to CP | 0                      | 0                       |                                                                 |    |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                | 7.0                    | 7.0                     |                                                                 |    |

| t <sub>S</sub> (L) | C/SI to CP                             | 7.0                    | 7.0                     |                                                                 |    |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                 | 0                      | 0                       |                                                                 | ns |

| t <sub>H</sub> (L) | C/SI to CP                             | 0                      | 0                       |                                                                 |    |

| t <sub>W</sub> (H) | Clock Pulse Width, HIGH                | 5.0                    | 5.0                     |                                                                 | ns |

74F524