Technology

## 128K x 8 BIT PROGRAMMABLE EEPROM 8090

X

н

Bowmar/White Technolog

2 FF SF WOOD ST. . PHOENIX, AZ 85040 437-1520 • TWX: 910-951-4203

Write Inhibit

## 28K x 8 BIT PROFRAMMABLE FROM - 809

## **DEVICE OPERATION**

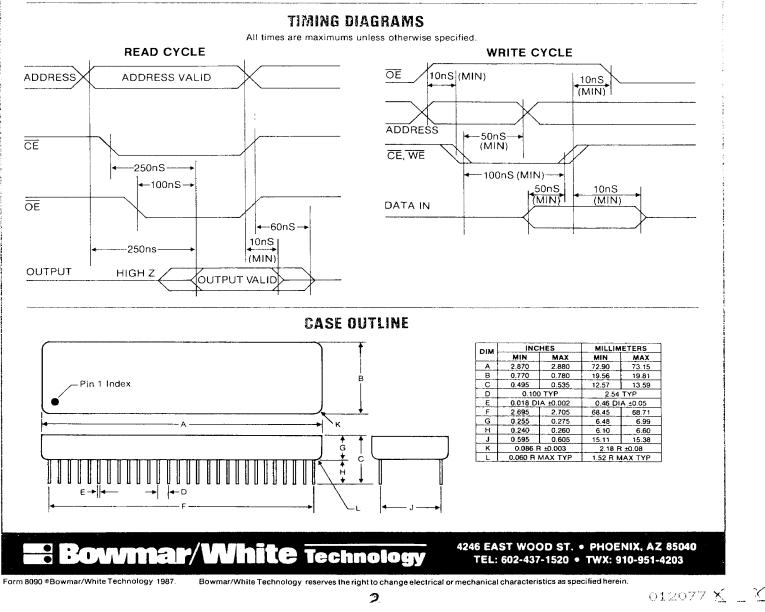

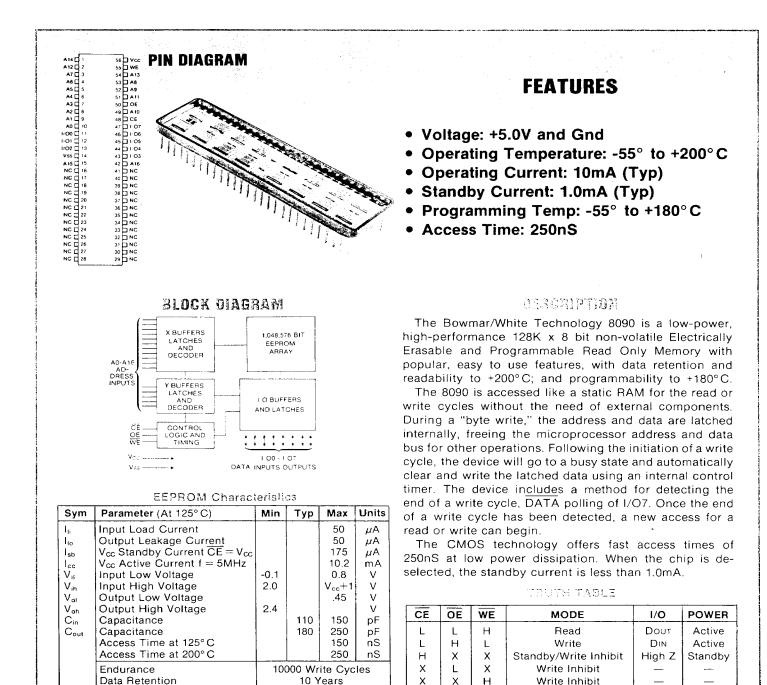

- **READ**The 8090 is accessed like a static RAM. When<br/>CE and OE are low and WE is high, the data<br/>stored at the memory location determined by<br/>the address pins is asserted on the outputs.<br/>The outputs are put in a high impedance<br/>state whenever CE or OE is high. This dual<br/>line control gives designers increased flexi-<br/>bility in preventing bus contention.

- BYTEWriting data into the 8090 is similar to writing<br/>into a static RAM. A low pulse on the WE or<br/>CE input with OE high and CE or WE low<br/>(respectively) initiates a byte write. The ad-<br/>dress location is latched on the falling edge<br/>of WE (or CE); the new data is latched on the<br/>rising edge. Internally the device performs a<br/>self-clear before write. Once a byte write has<br/>been started, it will automatically time it-<br/>self to completion. Write cycle is 1mS max.

- DATA POLLING

The 8090 also utilizes DATA POLLING to signal the completion of a write cycle. During a write cycle, an attempted read of the data being written results in the compliment of that data for I/O7 (the other outputs are indeterminate). When the write cycle is finished, true data appears on all outputs.

WRITE PROTEC-TION Inadvertent writes to the device are protected against in the following ways: (a) Vcc sense—if Vcc is below 3.8V, the write function is inhibited; (b) Vcc power on delay once Vcc has reached 3.8V, the device will automatically time out 5mS before allowing a byte write; (c) Write Inhibit—holding any one of OE low, CE high or WE high inhibits byte write cycles.