# INTEGRATED CIRCUITS

Preliminary specification Supersedes data of 1998 Apr 23 IC20 Data Handbook 1999 Apr 15

# 83C748/87C748

### DESCRIPTION

The Philips 83C748/87C748 offers the advantages of the 80C51 architecture in a small package and at low cost.

The 8XC748 Microcontroller is fabricated with Philips high-density CMOS technology. Philips epitaxial substrate minimizes CMOS latch-up sensitivity.

The 8XC748 contains a  $2k \times 8$  ROM (83C748) EPROM (87C748), a  $64 \times 8$  RAM, 19 I/O lines, a 16-bit auto-reload counter/timer, a four-source, fixed-priority level interrupt structure, and an on-chip oscillator.

## **FEATURES**

- 80C51 based architecture

- Small package sizes

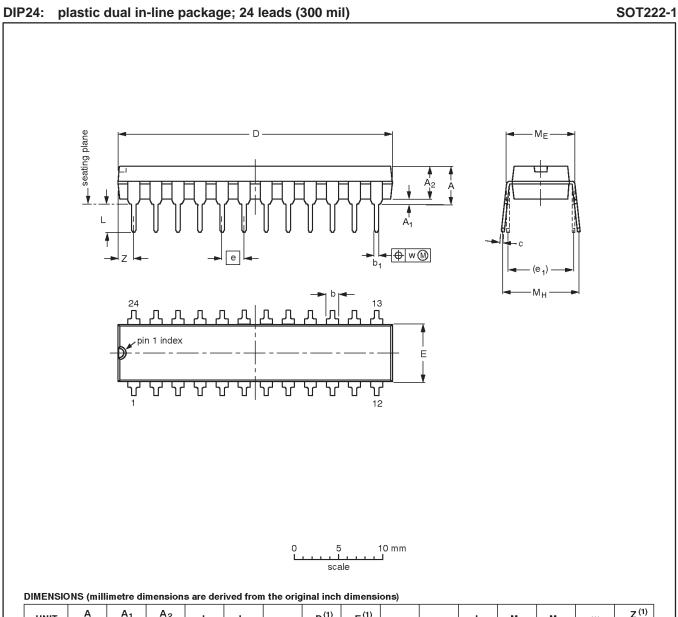

- 24-pin DIP (300 mil "skinny DIP")

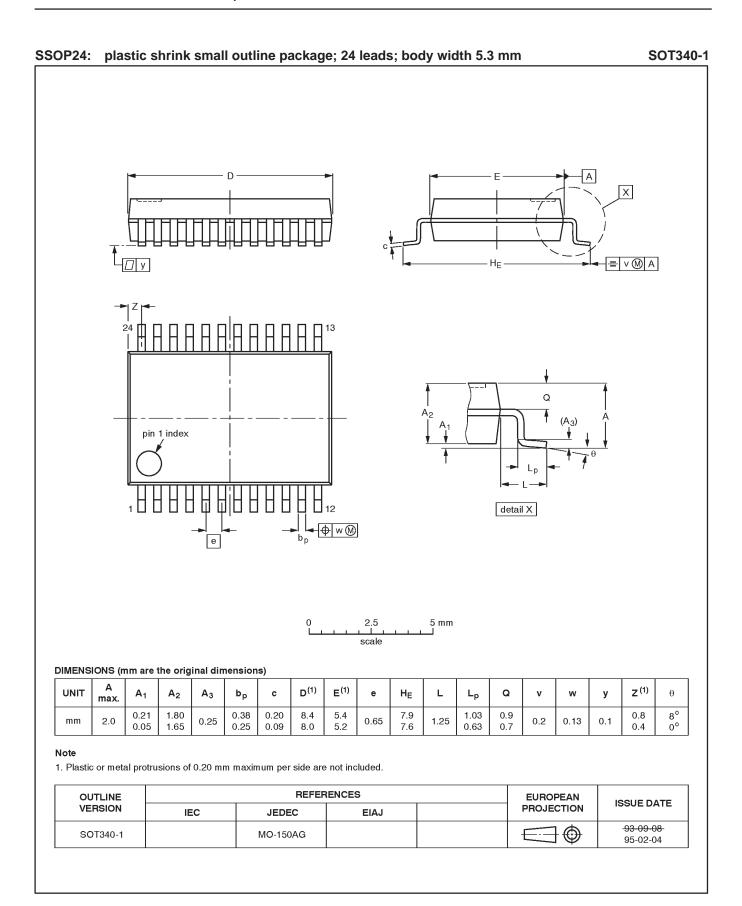

- 24-pin Shrink Small Outline Package (SSOP)

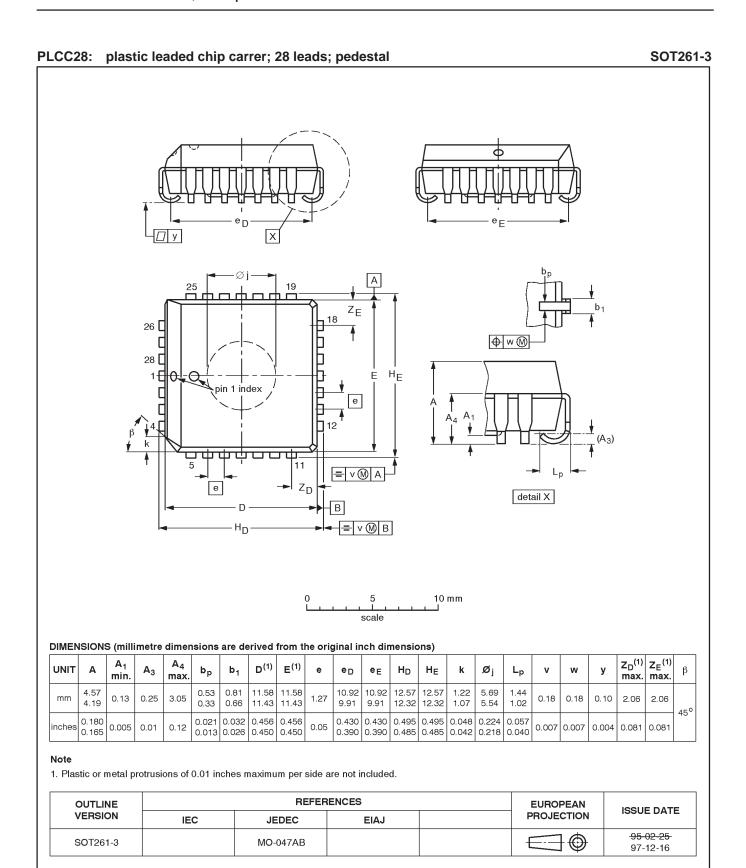

- 28-pin PLCC

- 87C748 available in erasable quartz lid or one-time programmable plastic packages

- Wide oscillator frequency range: -3.5 to 16MHz

- Low power consumption:

- Normal operation: less than 11mA @ 5V, 12MHz

- Idle mode

- Power-down mode

- 2k × 8 ROM (83C748)

2k × 8 EPROM (87C748)

- 64 × 8 RAM

- 16-bit auto reloadable counter/timer

- 10-bit fixed-rate timer

- Boolean processor

- CMOS and TTL compatible

- Well suited for logic replacement, consumer and industrial applications

- LED drive outputs

## **ORDERING INFORMATION**

| ROM           | EPROM <sup>1</sup>                                                                    |     | EPROM <sup>1</sup> TEMPERATURE RANGE <sup>°</sup> C<br>AND PACKAGE |           | FREQUENCY<br>MHz | DRAWING<br>NUMBER |

|---------------|---------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|-----------|------------------|-------------------|

| P83C748EBP N  | P87C748EBP N OTP                                                                      |     | 0 to +70, Plastic Dual In-line Package                             | 3.5 to 16 | SOT222-1         |                   |

| P83C748EBA A  | 8EBA A         P87C748EBA A         OTP         0 to +70, Plastic Leaded Chip Carrier |     | 3.5 to 16                                                          | SOT261-3  |                  |                   |

| P83C748EBD DB | P87C748EBD DB                                                                         | OTP | 0 to +70, Shrink Small Outline Package                             | 3.5 to 16 | SOT340-1         |                   |

NOTE:

1. OTP = One Time Programmable EPROM.

# 030740/070740

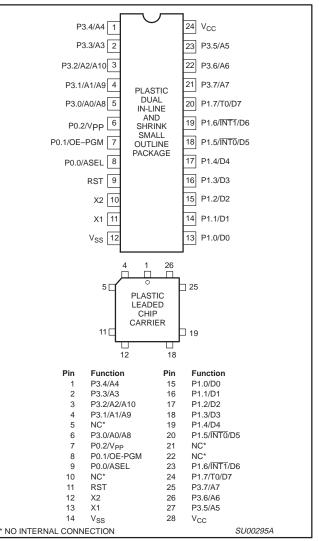

### **PIN CONFIGURATIONS**

# 83C748/87C748

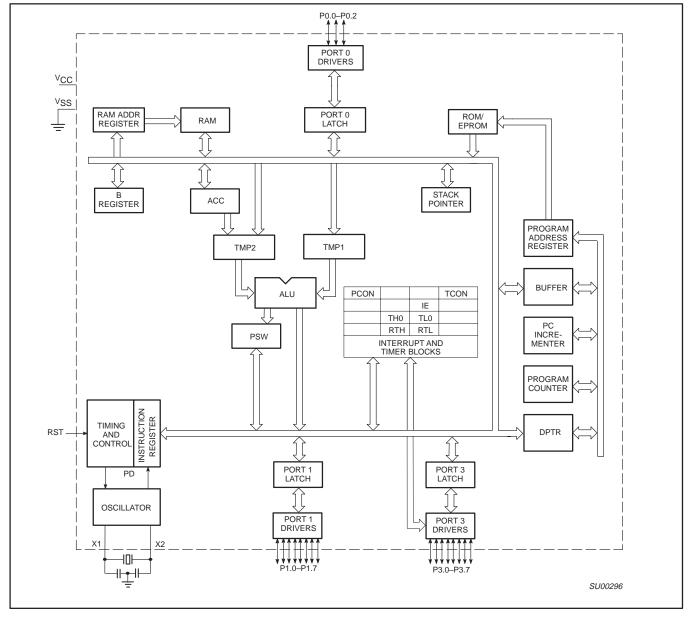

## **BLOCK DIAGRAM**

# 83C748/87C748

### **PIN DESCRIPTIONS**

| MNEMONIC         DIP/<br>SSOP         LCC         TYPE         NAME AND FUNCTION           V <sub>SS</sub> 12         14         1         Circuit Ground Potential           V <sub>CC</sub> 24         28         1         Supply voltage during normal, idle, and power-down operation.           P0.0–P0.2         8–6         9–7         I/O         Port 0: Port 0: is a 3-bit open-drain, bidfrectional port. Port 0 pins that have 1s written to them float, and in that state can be used as singhi-impedance inputs. These pins are driven low if the port register bit is written with a 0. The state of the pin can always be readfrom the port register by the program.<br>Po.0 and PO.1 are open drain bidfrectional I/O pins. While these differ from "standard TTL", characteristics, they are close enough for the pins to still be used as general-purpose I/O. Port 0 also provides alternate functions for programming the EPROM memory as follows:<br>V/P (P0.2) – Programming voltage input. (See Note 1).<br>OE/PGM = 0 program mode.<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | PIN NO. |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC         24         28         1         Supply voltage during normal, idle, and power-down operation.           P0.0-P0.2         8-6         9-7         I/O         Port 0: Port 0 is a 3-bit open-drain, bidirectional port. Port 0 pins that have 1s written to them float, and in that state can be used as high-impedance inputs. These pins are driven low if the port register bit is written with a 0. The state of the pin can always be read from the port register by the program. P0.0 and P0.1 are open drain bidirectional I/O pins. While these differ from "standard TTL" characteristics, they are close enough for the pins to still be used as general-purpose I/O. Port 0 also provides alternate functions for programming the EPROM memory as follows:           P0.0         N/A         Vpe (P0.2) – Programming voltage input. (See Note 1).           OEPRGM (P0.1) – Input which indicates which bits of the EPROM address are applied to port 3. ASEL = 0 low address byte available on port 3.           ASEL (P0.0) – Input which indicates which bits of the EPROM address are applied to port 3. ASEL = 0 low address byte available on port 3.           P1.0-P1.7         13-20         15-20, 12.           18         20         1           19         23         1           19         23         1           19         23         1           19         23         1           10-D-P1.7         13-20         15-20, 10/C           10.7         13-7         6.4-1, 10/C </th <th>MNEMONIC</th> <th></th> <th>LCC</th> <th>TYPE</th> <th>NAME AND FUNCTION</th>                                                                                                                                                                                                                                                   | MNEMONIC        |         | LCC | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                    |

| P0.0-P0.2       8-6       9-7       I/O       Port 0: Port 0 is a 3-bit open-drain, bidirectional port. Port 0 pins that have 1s written to them float, and in that state can be used as high-impedance inputs. These pins are driven low if the porgram. P0.0 and P0.1 are open drain bidirectional I/O pins. While these differ from "standard TTL" characteristics, they are close enough for the pins to still be used as general-purpose I/O. Port 0 also provides alternate functions for programming the EPROM memory as follows:         6       7       N/A       Vpp (P0.2) - Programming voltage input. (See Note 1).         0.2FPGM (P0.1) - Input which specifies verify mode).       OE/PGM (P0.1) - Input which specifies verify mode).         0.2FPGM (P0.1) - Input which is specifies verify mode).       OE/PGM = 0 output enabled (verify mode).         0.2FPGM (P0.1) - Input which indicates which bits of the EPROM address are applied to port 3.         ASEL (P0.0) - Input which indicates which bits of the EPROM contents in the verify mode.         P1.0-P1.7       13-20       15-20,         V/D       Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Algoe DC Electrical Characteristics: I_1). Port 1 serves to output the address during the program mode. Port 1 also serves the special function for source unrent because of the internal pull-ups. GC ED C Electrical Characteristics: I_1). Port 1 serves to output the address strip the value of the internal pull-ups. GC ED C Electrical Characteristics: I_1). Port 1 serves to output the address during the program mode. Port 1 also serves the special function features of the 80CS1 family as listed below:         P1.0-P1.7 <td>V<sub>SS</sub></td> <td>12</td> <td>14</td> <td>I</td> <td>Circuit Ground Potential</td>       | V <sub>SS</sub> | 12      | 14  | I    | Circuit Ground Potential                                                                                                                                                                                                                                                                                                                                                                                             |

| and in that state can be used as high-impedance inputs. These pins are driven low if the port register bit is written with a 0. The state of the pin can always be read from the port register by the program.         P0.0 and P0.1 are open drain bidirectional I/O pins. While these differ from "standard TTL" characteristics, they are close enough for the pins to still be used as general-purpose I/O. Port 0 also provides alternate functions for programming the EPROM memory as follows:         6       7       N/A       Vpp (P0.2) – Programming voltage input. (See Note 1).         7       8       1       OE/POM (P0.1) – Input which specifies verify mode (output enable) or the program mode.         02/POM = 0 program mode.       8       9       1       ASEL (P0.0) – Input which indicates which bits of the EPROM address are applied to port 3. ASEL = 1 high address byte available on port 3.         ASEL = 1 owa darkers byte available on port 3.       ASEL = 1 high address byte available on port 3.         ASEL = 1 bigh address byte available on port 3.       ASEL = 1 high address byte available on port 3.         ASEL = 1 bigh address byte available on port 3.       ASEL = 1 high address byte available on port 3.         ASEL = 1 bigh address byte available on port 3.       ASEL = 1 high address byte available on port 3.         ASEL = 1 high address byte available on port 3.       ASEL = 1 high address byte available on port 3.         ASEL = 1 high address byte available on port 3.       ASEL = 1 high address byte available on port 3.         ASEL = 1 figh address b                                                                                                                                                                                                                  | V <sub>CC</sub> | 24      | 28  | 1    | Supply voltage during normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                        |

| 67N/AVspc (P0.2) - Programming voltage input. (See Note 1).781OE/PGM (P0.1) - Input which specifies verify mode (output enable) or the program mode.<br>OE/PGM = 0 program mode.891ASEL (P0.0) - Input which specifies verify mode (output enable) or the program mode.<br>OE/PGM = 0 program mode.891ASEL (P0.0) - Input which indicates which bits of the EPROM address are applied to port 3.<br>ASEL = 1 high address byte available on port 3.<br>ASEL = 1 high address byte available on port 3.<br>ASEL = 1 high address byte available on port 3.<br>ASEL = 1 high address byte available on port 3.<br>ASEL = 1 high address byte available on port 3.<br>Caracteristics: II_U. Port 1: son 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written<br>to the mare pulled high by the internal pull-ups and can be used as inputs, As inputs, port 1 pins<br>that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical<br>Characteristics: II_U.) Port 1 serves to output the addressed EPROM contents in the verify mode and<br>accepts as inputs the value to program into the selected address during the program mode. Port 1<br>also serves the special function features of the 80C51 family as listed below:P3.0-P3.75-1,<br>23-216.4-1,<br>27-25I/O<br>27-25Port 3 son 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written<br>to the mare pulled high by the internal pull-ups. Port 3 pins that have 1s written<br>to the mare pulled high by the internal pull-ups. Port 3 pins that have 1s written<br>to the mare externally pulled low will source current because of the pull-ups. Rot 3 pins that have 1s written<br>to the are respecial function features of the 80C51 family as listed below:P3.0-P3.7<                   | P0.0-P0.2       | 8–6     | 9–7 | I/O  | and in that state can be used as high-impedance inputs. These pins are driven low if the port register                                                                                                                                                                                                                                                                                                               |

| 7       8       1       OE/PGM (P0.1) – Input which specifies verify mode (output enable) or the program mode.<br>OE/PGM = 1 output enabled (verify mode).         8       9       1       ASEL (P0.0) – Input which indicates which bits of the EPROM address are applied to port 3.<br>ASEL = 0 low address byte available on port 3.<br>ASEL = 0 low address byte available on port 3 (only the three least significant bits are used).         P1.0–P1.7       13–20       15–20,<br>23, 24       I/O       Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins<br>that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical<br>Characteristics: III). Port 1 serves to output the addressed EPROM contents in the verify mode and<br>accepts as inputs the value to program into the selected address during the program mode. Port 1<br>also serves the special function features of the 80C51 family as listed below:         P3.0–P3.7       5-1,<br>23–21       6, 4-1,<br>27–25       I/O       Port 3: Fort 3 as 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: II_I). Port 3 also functions as the address input for the EPROM memory location to be<br>programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.         RST       9       11       1       Resest: A high on this pin for two machine cycles while t |                 |         |     |      | characteristics, they are close enough for the pins to still be used as general-purpose I/O. Port 0 also provides alternate functions for programming the EPROM memory as follows:                                                                                                                                                                                                                                   |

| 8       9       I       ASEL = 0 low address byte available on port 3.<br>ASEL = 0 low address byte available on port 3.<br>ASEL = 1 high address byte available on port 3.<br>ASEL = 1 high address byte available on port 3 (only the three least significant bits are used).         P1.0–P1.7       13–20       15–20,<br>23, 24       I/O       Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. Port 1 also serves the special function features of the 80C51 family as listed below:         18       20       1       INTT (P1.6): External interrupt.         20       24       1       TO (P1.7): Timer 0 external input.         P3.0–P3.7       5–1,<br>23–21       6, 4–1,<br>27–25       I/O       Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Gee DC Electrical<br>Characteristics: In_L). Port 3 also functions as the address input for the EPROM memory locatin to be              |                 |         |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1.0-P1.713-2015-20,<br>23, 24I/OPort 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins<br>that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical<br>Characteristics: III.). Port 1 serves to output the addressed EPROM contents in the verify mode and<br>accepts as inputs the value to program into the selected address during the program mode. Port 1<br>also serves the special function features of the 80C51 family as listed below:18201INTT (P1.6): External interrupt.<br>1920241T0 (P1.7): Timer 0 external input.20241T0 (P1.7): Timer 0 external pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: III.). Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: III.). Port 3 also functions as the address input for the EPROM memory location to be<br>programmed (or verified). The 11-bit address is multiplexed into this port as specified by PO.0/ASEL.RST911IReset: A high on this pin for two machine cycles while the oscillator is running, resets the device.<br>An internal diffused resistor to Vss permits a power-on RESET using only an external capacitor to<br>Vcc. After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places<br>the device in the prog      |                 | 7       | 8   |      | OE/PGM = 1 output enabled (verify mode).                                                                                                                                                                                                                                                                                                                                                                             |

| 23, 24to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins<br>that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical<br>Characteristics: IIL). Port 1 serves to output the addressed EPROM contents in the verify mode and<br>accepts as inputs the value to program into the selected address during the program mode. Port 1<br>also serves the special function features of the 80C51 family as listed below:18201INTT (P1.6): External interrupt.19231INTT (P1.6): External interrupt.20241T0 (P1.7): Timer 0 external input.P3.0-P3.75-1,<br>23-216, 4-1,<br>27-25I/OPort 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written<br>to them are epulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: II_L). Port 3 also functions as the address input for the EPROM memory location to be<br>programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.RST911IReset: A high on this pin for two machine cycles while the oscillator is running, resets the device.<br>An internal diffused resistor to V <sub>SS</sub> permits a power-on RESET using only an external calcor to<br>V <sub>CC</sub> . After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places<br>the device in the programming state allowing programming address, data and V <sub>PP</sub> to be applied for<br>programming or verification purposes. The RESET serial sequence must be synchronized with the<br>X1 input.X11113I                                                                     |                 | 8       | 9   | I    | ASEL = 0 low address byte available on port 3.                                                                                                                                                                                                                                                                                                                                                                       |

| 19<br>2023<br>241INT1 (P1.6): External interrupt.<br>T0 (P1.7): Timer 0 external input.P3.0-P3.75-1,<br>23-216, 4-1,<br>27-25I/OPort 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: IL). Port 3 also functions as the address input for the EPROM memory location to be<br>programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.RST911IReset: A high on this pin for two machine cycles while the oscillator is running, resets the device.<br>An internal diffused resistor to V <sub>SS</sub> permits a power-on RESET using only an external capacitor to<br>V <sub>CC</sub> . After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places<br>the device in the programming or verification purposes. The RESET serial sequence must be synchronized with the<br>X1 input.X11113ICrystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.<br>X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the<br>programming state.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P1.0–P1.7       | 13–20   |     | I/O  | to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 1 serves to output the addressed EPROM contents in the verify mode and accepts as inputs the value to program into the selected address during the program mode. Port 1 |

| 2024IT0 (P1.7): Timer 0 external input.P3.0-P3.75-1,<br>23-216, 4-1,<br>27-25I/OPort 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: II). Port 3 also functions as the address input for the EPROM memory location to be<br>programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.RST911IReset: A high on this pin for two machine cycles while the oscillator is running, resets the device.<br>An internal diffused resistor to V <sub>SS</sub> permits a power-on RESET using only an external capacitor to<br>V <sub>CC</sub> . After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places<br>the device in the programming state allowing programming address, data and V <sub>PP</sub> to be applied for<br>programming or verification purposes. The RESET serial sequence must be synchronized with the<br>X1 input.X11113ICrystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.<br>X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the<br>programming state.                                                                                                                                                                                                                                                                                                                                                                                                                |                 | 18      |     | 1    |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P3.0-P3.75-1,<br>23-216, 4-1,<br>27-25I/OPort 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written<br>to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: I <sub>IL</sub> ). Port 3 also functions as the address input for the EPROM memory location to be<br>programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.RST911IReset: A high on this pin for two machine cycles while the oscillator is running, resets the device.<br>An internal diffused resistor to V <sub>SS</sub> permits a power-on RESET using only an external capacitor to<br>V <sub>CC</sub> . After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places<br>the device in the programming state allowing programming address, data and V <sub>PP</sub> to be applied for<br>programming or verification purposes. The RESET serial sequence must be synchronized with the<br>X1 input.X11113ICrystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.<br>X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the<br>programming state.                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |         |     | 1    |                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23-2127-25to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins<br>that are externally being pulled low will source current because of the pull-ups. (See DC Electrical<br>Characteristics: IL). Port 3 also functions as the address input for the EPROM memory location to be<br>programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.RST911IReset: A high on this pin for two machine cycles while the oscillator is running, resets the device.<br>An internal diffused resistor to V <sub>SS</sub> permits a power-on RESET using only an external capacitor to<br>V <sub>CC</sub> . After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places<br>the device in the programming state allowing programming address, data and V <sub>PP</sub> to be applied for<br>programming or verification purposes. The RESET serial sequence must be synchronized with the<br>X1 input.X11113ICrystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.<br>X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the<br>programming state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | 20      | 24  |      | T0 (P1.7): Timer 0 external input.                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>An internal diffused resistor to V<sub>SS</sub> permits a power-on RESET using only an external capacitor to V<sub>CC</sub>. After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places the device in the programming state allowing programming address, data and V<sub>PP</sub> to be applied for programming or verification purposes. The RESET serial sequence must be synchronized with the X1 input.</li> <li>X1 11 13 I Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits. X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the programming state.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P3.0–P3.7       |         |     | I/O  | to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: $I_{ L }$ ). Port 3 also functions as the address input for the EPROM memory location to be                                                                                                 |

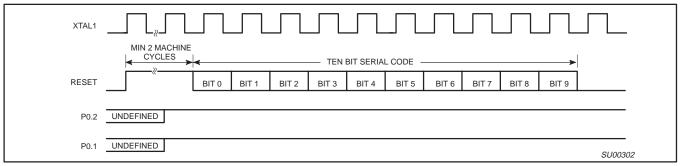

| X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the programming state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RST             | 9       | 11  |      | An internal diffused resistor to $V_{SS}$ permits a power-on RESET using only an external capacitor to $V_{CC}$ . After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places the device in the programming state allowing programming address, data and $V_{PP}$ to be applied for programming or verification purposes. The RESET serial sequence must be synchronized with the  |

| X2 10 12 O Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X1              | 11      | 13  | I    | X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X2              | 10      | 12  | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                           |

NOTE:

When P0.2 is at or close to 0 volts, it may affect the internal ROM operation. It is recommended that P0.2 be tied to V<sub>CC</sub> via a small pull-up (e.g. 2kΩ).

## ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

| PARAMETER                                           | RATING                        | UNIT |

|-----------------------------------------------------|-------------------------------|------|

| Storage temperature range                           | -65 to +150                   | °C   |

| Voltage from $V_{CC}$ to $V_{SS}$                   | –0.5 to +6.5                  | V    |

| Voltage from any pin to $V_{SS}$ (except $V_{PP}$ ) | –0.5 to V <sub>CC</sub> + 0.5 | V    |

| Power dissipation                                   | 1.0                           | W    |

| Voltage on V <sub>PP</sub> pin to V <sub>SS</sub>   | 0 to +13.0                    | V    |

| Maximum I <sub>OL</sub> per I/O pin                 | 10                            | mA   |

NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

2. This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

83C748/87C748

# DC ELECTRICAL CHARACTERISTICS

$T_{amb} = 0^{\circ}C$  to +70°C,  $V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = 0V^{1}$

| SYMBOL           | PARAMETER                                                     | TEST CONDITIONS                                                                          | LIN                     | UNIT                   |    |  |

|------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------|------------------------|----|--|

| STWBOL           | FARAMETER                                                     | TEST CONDITIONS                                                                          | MIN                     | MAX                    | 7  |  |

| V <sub>IL</sub>  | Input low voltage                                             |                                                                                          | -0.5                    | 0.2V <sub>DD</sub> 0.1 | V  |  |

| VIH              | Input high voltage, except X1, RST                            |                                                                                          | 0.2V <sub>CC</sub> +0.9 | V <sub>CC</sub> +0.5   | V  |  |

| V <sub>IH1</sub> | Input high voltage, X1, RST                                   |                                                                                          | 0.7V <sub>CC</sub>      | V <sub>CC</sub> +0.5   | V  |  |

|                  | P0.2                                                          |                                                                                          |                         |                        |    |  |

| V <sub>IL1</sub> | Input low voltage                                             |                                                                                          | -0.5                    | 0.3V <sub>CC</sub>     | V  |  |

| V <sub>IH2</sub> | Input high voltage                                            |                                                                                          | 0.7V <sub>CC</sub>      | V <sub>CC</sub> +0.5   | V  |  |

| V <sub>OL</sub>  | Output low voltage, ports 1 and 3                             | $I_{OL} = 1.6 m A^2$                                                                     |                         | 0.45                   | V  |  |

| V <sub>OL1</sub> | Output low voltage, port 0.2                                  | $I_{OL} = 3.2 m A^2$                                                                     |                         | 0.45                   | V  |  |

| V <sub>OH</sub>  | Output high voltage, ports 1 and 3                            | I <sub>OH</sub> = -60μA                                                                  | 2.4                     |                        | V  |  |

|                  |                                                               | I <sub>OH</sub> = -25μA                                                                  | 0.75V <sub>CC</sub>     |                        | V  |  |

|                  |                                                               | I <sub>OH</sub> = −10μA                                                                  | 0.9V <sub>CC</sub>      |                        | V  |  |

|                  | Port 0.0 and 0.1 – Drivers                                    |                                                                                          |                         |                        |    |  |

| V <sub>OL2</sub> | Output low voltage                                            | I <sub>OL</sub> = 3mA                                                                    |                         | 0.4                    | V  |  |

|                  | Driver, receiver combined:                                    | (over V <sub>CC</sub> range)                                                             |                         |                        |    |  |

| С                | Capacitance                                                   |                                                                                          |                         | 10                     | pF |  |

| IIL              | Logical 0 input current, ports 1 and 3                        | V <sub>IN</sub> = 0.45V                                                                  |                         | -50                    | μΑ |  |

| I <sub>TL</sub>  | Logical 1 to 0 transition current, ports 1 and 3 <sup>3</sup> | V <sub>IN</sub> = 2V (0 to 70°C)                                                         |                         | -650                   | μΑ |  |

| ILI              | Input leakage current, port 0                                 | $0.45 < V_{IN} < V_{CC}$                                                                 |                         | ±10                    | μΑ |  |

| R <sub>RST</sub> | Internal pull-down resistor                                   |                                                                                          | 25                      | 175                    | kΩ |  |

| C <sub>IO</sub>  | Pin capacitance                                               | Test freq = 1MHz,<br>T <sub>amb</sub> = 25°C                                             |                         | 10                     | pF |  |

| I <sub>PD</sub>  | Power-down current <sup>4</sup>                               | $V_{CC} = 2$ to $V_{CC}$ max                                                             |                         | 50                     | μΑ |  |

| V <sub>PP</sub>  | V <sub>PP</sub> program voltage (for 87C748 only)             | $V_{SS} = 0V$<br>$V_{CC} = 5V\pm10\%$<br>$T_{amb} = 21^{\circ}C \text{ to } 27^{\circ}C$ | 12.5                    | 13.0                   | V  |  |

| I <sub>PP</sub>  | Program current (for 87C748 only)                             | V <sub>PP</sub> = 13.0V                                                                  |                         | 50                     | mA |  |

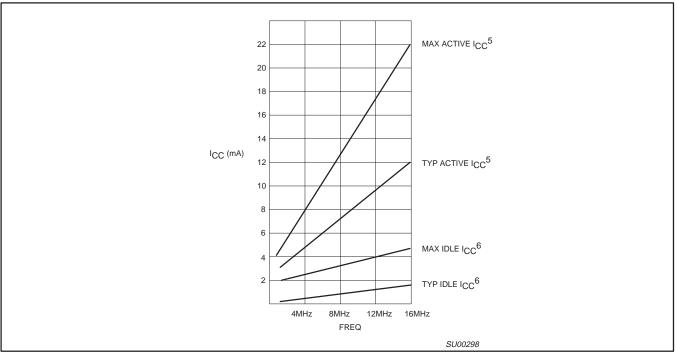

| I <sub>CC</sub>  | Supply current (see Figure 2)                                 |                                                                                          |                         |                        |    |  |

NOTES:

1. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

2. Under steady state (non-transient) conditions, IOL must be externally limited as follows:

| Maximum I <sub>OI</sub> | per port pin:   | _10mA |

|-------------------------|-----------------|-------|

| Maximum I               | per 8-bit port: | 26mA  |

- Maximum IOL per 8-bit port:

- Maximum total IOL for all outputs: 67mA

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

3. Pins of ports 1 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when VIN is approximately 2V.

4. Power-down I<sub>CC</sub> is measured with all output pins disconnected; port 0 = V<sub>CC</sub>; X2, X1 n.c.; RST = V<sub>SS</sub>.

Active loc: is measured with all output pins disconnected; X1 driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5V, V<sub>IH</sub> = V<sub>CC</sub> - 0.5V; X2 n.c.; RST = port 0 = V<sub>CC</sub>. I<sub>CC</sub> will be slightly higher if a crystal oscillator is used.

Idle I<sub>CC</sub> is measured with all output pins disconnected; X1 driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5V, V<sub>IH</sub> = V<sub>CC</sub> - 0.5V; X2 n.c.; port 0 = V<sub>CC</sub>; RST = V<sub>SS</sub>.

# 83C748/87C748

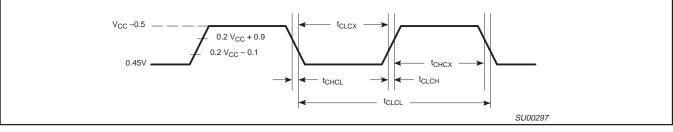

# **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0^{\circ}C$  to +70°C,  $V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = 0V^{1, 2}$

|                     |                       | 16MHz | CLOCK | VARIABL    |          |            |

|---------------------|-----------------------|-------|-------|------------|----------|------------|

| SYMBOL              | PARAMETER             | MIN   | MAX   | MIN        | MAX      | UNIT       |

| 1/t <sub>CLCL</sub> | Oscillator frequency: |       |       | 3.5<br>3.5 | 12<br>16 | MHz<br>MHz |

| External Cl         | ock (Figure 1)        |       |       |            |          |            |

| t <sub>CHCX</sub>   | High time             | 20    |       | 20         |          | ns         |

| t <sub>CLCX</sub>   | Low time              | 20    |       | 20         |          | ns         |

| t <sub>CLCH</sub>   | Rise time             |       | 20    |            | 20       | ns         |

| t <sub>CHCL</sub>   | Fall time             |       | 20    |            | 20       | ns         |

NOTES:

1. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

2. Load capacitance for ports = 80pF.

# **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

- C Clock

- D Input data

Q - Output data T - Time

L - Logic level low

- V Valid

- X No longer a valid logic level

- Z Float

H - Logic level high

Figure 1. External Clock Drive

## **ROM CODE SUBMISSION**

When submitting ROM code for the 83C748, the following must be specified:

1. 2k byte user ROM data

| ADDRESS        | CONTENT | BIT(S) | COMMENT       |  |

|----------------|---------|--------|---------------|--|

| 0000H to 07FFH | DATA    | 7:0    | User ROM Data |  |

# 83C748/87C748

# **OSCILLATOR CHARACTERISTICS**

X1 and X2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator.

To drive the device from an external clock source, X1 should be driven while X2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

## RESET

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods), while the oscillator is running. To insure a good power-up reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles. At power-up, the voltage on  $V_{CC}$  and RST must come up at the same time for a proper start-up.

## **IDLE MODE**

In idle mode, the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

## **POWER-DOWN MODE**

In the power-down mode, the oscillator is stopped and the instruction to invoke power-down is the last instruction executed. Only the contents of the on-chip RAM are preserved. A hardware reset is the only way to terminate the power-down mode. the control bits for the reduced power modes are in the special function register PCON.

# Table 1.External Pin Status During Idle and<br/>Power-Down Modes

| MODE       | Port 0 | Port 1 | Port 2 |

|------------|--------|--------|--------|

| Idle       | Data   | Data   | Data   |

| Power-down | Data   | Data   | Data   |

# 83C748/87C748

# DIFFERENCES BETWEEN THE 8XC748 AND THE 80C51

## Memory Organization

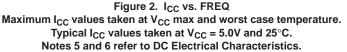

The central processing unit (CPU) manipulates operands in two address spaces as shown in Figure 3. The part's internal memory space consists of 2k bytes of program memory, and 64 bytes of data RAM overlapped with the 128-byte special function register area. The differences from the 80C51 are in RAM size (64 bytes vs. 128 bytes), in external RAM access (not available on the 83C748), in internal ROM size (2k bytes vs. 4k bytes), and in external program memory expansion (not available on the 83C748). The 128-byte special function register (SFR) space is accessed as on the 80C51 with some of the registers having been changed to reflect changes in the 83C748 peripheral functions. The stack may be located anywhere in internal RAM by loading the 8-bit stack pointer (SP). It should be noted that stack depth is limited to 64 bytes, the amount of available RAM. A reset loads the stack pointer with 07 (which is pre-incremented on a PUSH instruction).

## **Program Memory**

On the 8XC748, program memory is 2048 bytes long and is not externally expandable, so the 80C51 instructions MOVX, LJMP, and LCALL are not implemented. The only fixed locations in program memory are the addresses at which execution is taken up in response to reset and interrupts, which are as follows:

|                 | Program Memory |

|-----------------|----------------|

| Event           | Address        |

| Reset           | 000            |

| External INT0   | 003            |

| Counter/timer 0 | 00B            |

| External INT1   | 013            |

| Timer I         | 01B            |

|                 |                |

## **Counter/Timer Subsystem**

The 8XC748 has one counter/timer called timer/counter 0. Its operation is similar to mode 2 operation on the 80C51, but is extended to 16 bits with 16 bits of autoload. The controls for this counter are centralized in a single register called TCON.

Timer I is available for use as a fixed 10-bit time-base, or as a watchdog.

## **Counter Timer – Special Function Register**

The counter/timer has only one mode of operation, so the TMOD SFR is not used. There is also only one counter/timer, so there is no need for the TL1 and TH1 SFRs found on the 80C51. These have been replaced on the 8XC748 by RTL and RTH, the counter/timer reload registers. Table 2 shows the special function registers, their locations, and reset values.

### Interrupt Subsystem – Fixed Priority

The IP register and the 2-level interrupt system of the 80C51 are eliminated. Simultaneous interrupt conditions are resolved by a single-level, fixed priority as follows:

| Highest priority: | Pin INT0             |

|-------------------|----------------------|

|                   | Counter/timer flag 0 |

|                   | Pin INT1             |

| Lowest priority:  | Timer I              |

### Special Function Register – Interrupt Subsystem

Because the interrupt structure is single level on the 83C748, there is no need for the IP SFR, so it is not used.

# Special Function Register – Serial Communications

The 8XC748 contains many of the special function registers (SFR) that are found on the 80C51. Due to the different peripheral features on the 8XC748, there are several additional SFRs. Since the UART found on 80C51 has been removed, the UART SFRs SCON and SBUF have also been removed.

## I/O Port Latches (P0, P1, P3)

The port latches function the same as those on the 80C51. Since there is no port 2 on the 83C748, the P2 latch is not used. Port 0 on the 83C748 has only 3 bits, so only 3 bits of the P0 SFR have a useful function.

## Data Pointer (DPTR)

The data pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). In the 80C51 this register allows the access of external data memory using the MOVX instruction. Since the 83C748 does not support MOVX or external memory accesses, this register is generally used as a 16-bit offset pointer of the accumulator in a MOVC instruction. DPTR may also be manipulated as two independent 8-bit registers.

Figure 3. Memory Map

## Preliminary specification

# 83C748/87C748

| SYMBOL     | DESCRIPTION                        | DIRECT<br>ADDRESS | BI<br>MSB | Γ ADDRE | SS, SYMB | OL, OR A | LTERNAT | IVE PORT | FUNCTIO | N<br>LSB | RESET<br>VALUE |

|------------|------------------------------------|-------------------|-----------|---------|----------|----------|---------|----------|---------|----------|----------------|

| ACC*       | Accumulator                        | E0H               | E7        | E6      | E5       | E4       | E3      | E2       | E1      | E0       | 00H            |

| B*         | B register                         | F0H               | F7        | F6      | F5       | F4       | F3      | F2       | F1      | F0       | 00H            |

| DPTR:      | Data pointer                       |                   |           |         |          |          |         |          |         |          |                |

| DPH<br>DPL | (2 bytes)<br>High byte<br>Low byte | 83H<br>82H        |           |         |          |          |         |          |         |          | 00H<br>00H     |

|            |                                    |                   | AF        | AE      | AD       | AC       | AB      | AA       | A9      | A8       |                |

| IE*#       | Interrupt enable                   | ABH               | EA        | -       | -        | -        | ETI     | EX1      | ET0     | EX0      | 00H            |

|            |                                    |                   |           |         |          |          |         | 82       | 81      | 80       |                |

| P0*#       | Port 0                             | 80H               | -         | -       | -        | -        | -       | -        | -       | -        | xxxxx111B      |

|            |                                    |                   | 97        | 96      | 95       | 94       | 93      | 92       | 91      | 90       |                |

| P1*        | Port 1                             | 90H               | Т0        | INT1    | INTO     | -        | -       | -        | -       | -        | FFH            |

| P3*        | Port 3                             | B0H               | B7        | B6      | B5       | B4       | B3      | B2       | B1      | B0       | FFH            |

| DOON       |                                    | 0711              | <u> </u>  |         |          |          |         |          |         |          |                |

| PCON#      | Power control                      | 87H               | -         | -       | -        | -        | -       | -        | PD      | IDL      | xxxxxx00B      |

|            |                                    |                   | D7        | D6      | D5       | D4       | D3      | D2       | D1      | D0       |                |

| PSW*       | Program status word                | D0H               | CY        | AC      | F0       | RS1      | RS0     | OV       | -       | Р        | 00H            |

| SP         | Stack pointer                      | 81H               |           |         |          |          |         |          |         |          | 07H            |

|            |                                    |                   | 8F        | 8E      | 8D       | 8C       | 8B      | 8A       | 89      | 88       |                |

| TCON*#     | Timer/counter control              | 88H               | GATE      | C/T     | TF       | TR       | IE0     | IT0      | IE1     | IT1      | 00H            |

| TL#<br>TH# | Timer low byte<br>Timer high byte  | 8AH<br>8CH        |           |         |          |          |         |          |         |          | 00H<br>00H     |

| 111#       | Timer nign byte                    | 0011              | DF        | DE      | DD       | DC       | DB      | DA       | D9      | D8       | 0011           |

| TICON*#    | Timer I control                    | D8H/RD            | -         | -       | 0        | TIRUN    | -       | -        | -       | -        | 0000xx00B      |

|            |                                    | WR                | -         | -       | CLRTI    | TIRUN    | -       | -        | -       | -        | ]              |

| RTL#       | Timer low reload                   | 8BH               |           |         |          |          |         |          |         |          | 00H            |

| RTH#       | Timer high reload                  | 8DH               |           |         |          |          |         |          |         |          | 00H            |

## Table 2. 8XC748 Special Function Registers

\* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

#### I/O Port Structure

The 8XC748 has two 8-bit ports (ports 1 and 3) and one 3-bit port (port 0). All three ports on the 8XC748 are bidirectional. Each consists of a latch (special function register P0, P1, P3), an output driver, and an input buffer. Three port 1 pins and two port 0 pins are multifunctional. In addition to being port pins, these pins serve the function of special features as follows:

### Port Pin Alternate Function

- P1.5 INT0 (external interrupt 0 input)

- P1.6 INT1 (external interrupt 1 input)

- P1.7 T0 (timer 0 external input)

Ports 1 and 3 are identical in structure to the same ports on the 80C51. The structure of port 0 on the 8XC748 is similar to that of the 80C51 but does not include address/data input and output circuitry. As on the 80C51, ports 1 and 3 are quasi-bidirectional while port 0 is bidirectional with no internal pullups.

### Timer/Counter

The 8XC748 has two timers: a 16-bit timer/counter and a 10-bit fixed-rate timer. The 16-bit timer/counter's operation is similar to mode 2 operation on the 80C51, but is extended to 16 bits. The timer/counter is clocked by either 1/12 the oscillator frequency or by transitions on the T0 pin. The C/T pin in special function register TCON selects between these two modes. When the TCON TR bit is set, the timer/counter is enabled. Register pair TH and TL are incremented by the clock source. When the register pair overflows, the register pair is reloaded with the values in registers RTH and RTL. The value in the reload registers is left unchanged. See the 83C748 counter/timer block diagram in Figure 4. The TF bit in special function register TCON is set on counter overflow and, if the interrupt is enabled, will generate an interrupt.

#### **TCON Register**

| MSB  |        |                                                                                                                                           |            |            |           |     | LSB |  |  |  |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------|-----|-----|--|--|--|

| GATE | C/T    | TF                                                                                                                                        | TR         | IE0        | IT0       | IE1 | IT1 |  |  |  |

| GATE | a      | <ol> <li>Timer/counter is enabled only when INT0 pin is high,<br/>and TR is 1.</li> <li>Timer/counter is enabled when TR is 1.</li> </ol> |            |            |           |     |     |  |  |  |

| C/T  | 1 – C  | ounter/til                                                                                                                                | mer oper   | ation fror | n T0 pin. |     |     |  |  |  |

| TF   | 0 – C  | 1 – Set on overflow of TH.                                                                                                                |            |            |           |     |     |  |  |  |

| TR   |        | ïmer/cou<br>ïmer/cou                                                                                                                      |            |            |           |     |     |  |  |  |

| IE0  | 1 – E  | dge dete                                                                                                                                  | cted in II | NTO.       |           |     |     |  |  |  |

| IT0  | 1 – 11 | NTO is ed                                                                                                                                 | ge trigge  | red.       |           |     |     |  |  |  |

|      | 0 – 11 | NTO is lev                                                                                                                                | /el sensit | ive.       |           |     |     |  |  |  |

| IE1  | 1 – E  | dge dete                                                                                                                                  | cted on I  | NT1.       |           |     |     |  |  |  |

| IT1  | 1 – 1  | NT1 is ed                                                                                                                                 | ge trigge  | red.       |           |     |     |  |  |  |

|      | 0 – 1  | NT1 is lev                                                                                                                                | vel sensit | ive.       |           |     |     |  |  |  |

These flags are functionally identical to the corresponding 80C51 flags, except that there is only one timer on the 83C748 and the flags are therefore combined into one register.

Note that the positions of the IE0/IT0 and IE1/IT1 bits are transposed from the positions used in the standard 80C51 TCON register.

#### Timer I Implementation

Timer I is clocked once per machine cycle, which is the oscillator frequency divided by 12. The timer operation is enabled by setting the TIRUN bit (bit 4) in the I2CFG register. Writing a 0 into the TIRUN bit will stop and clear the timer. The timer is 10 bits wide, and when it reaches the terminal count of 1024, it carries out and sets the Timer I interrupt flag. An interrupt will occur if the Timer I interrupt is enabled by bit ETI (bit 4) of the Interrupt Enable (IE) register, and global interrupts are enabled by bit EA (bit 7) of the same IE register.

The vector address for the Timer I interrupt is 1Bhex, and the interrupt service routine must start at this address. As with all 8051 family microcontrollers, only the Program Counter is pushed onto the stack upon interrupt (other registers that are used both by the interrupt service routine and elsewhere must be explicitly saved). The Timer I interrupt flag is cleared by setting the CKRTI bit (bit 5 of the 11CFG register. For more information, see application note AN427.

#### Interrupts

The interrupt structure is a four-source, one-level interrupt system. Interrupt sources common to the 80C51 are the external interrupts ( $\overline{\text{INT0}}$ ,  $\overline{\text{INT1}}$ ) and the timer/counter interrupt (ET0). Timer I interrupt (ETI) is the other interrupt source. The interrupt sources are listed below in their order of polling sequence priority.

Upon interrupt or reset the program counter is loaded with specific values for the appropriate interrupt service routine in program memory. These values are:

| F               | Program Memory |          |

|-----------------|----------------|----------|

| Event           | Address        | Priority |

| Reset           | 000            | Highest  |

| INT0            | 003            |          |

| Counter/Timer 0 | 00B            |          |

| INT1            | 013            |          |

| Timer I         | 01B            | Lowest   |

The interrupt enable register (IE) is used to individually enable or disable the four sources. Bit  $\overline{\text{EA}}$  in the interrupt enable register can be used to globally enable or disable all interrupt sources. The interrupt enable register is described below. All other interrupt details are based on the 80C51 interrupt architecture.

#### Interrupt Enable Register

| ĒĀ     | х       | х            | _                                                                                                                                                                                          | ETI    | EX1 | ET0 | EX0 |  |

|--------|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|--|

| Symbol | Positio | on           | Fur                                                                                                                                                                                        | nction |     |     |     |  |

| ĒĀ     | IE.7    | will<br>inte | Disables all interrupts. If EA = 0, no interrupt<br>will be acknowledged. If EA = 1, each<br>interrupt source is individually enabled or<br>disabled by setting or clearing its enable bit |        |     |     |     |  |

| -      | IE.6    | Res          | served                                                                                                                                                                                     |        |     |     |     |  |

| -      | IE.5    | Res          | Reserved                                                                                                                                                                                   |        |     |     |     |  |

| _      | IE.4    | Res          | Reserved                                                                                                                                                                                   |        |     |     |     |  |

| ETI | IE.3 | Enables or disables the Timer I overflow interrupt. If ET1 = 0, the Timer I interrupt is disabled.    |

|-----|------|-------------------------------------------------------------------------------------------------------|

| EX1 | IE.2 | Enables or disables external interrupt 1.<br>If EX1 = 0, external interrupt 1 is disabled.            |

| ET0 | IE.1 | Enables or disables the Timer 0 overflow interrupt. If $ET0 = 0$ , the Timer 0 interrupt is disabled. |

| EX0 | IE.0 | Enables or disables external interrupt 0.<br>If EX0 = 0, external interrupt 0 is disabled.            |

osc C/T = 0C TL TH TF Int C/T = 1 T0 Pin TR Reload Gate RTL RTH INT0 Pin SU00300

Figure 4. 83C748 Counter/Timer Block Diagram

# 83C748/87C748

# 83C748/87C748

### 87C748 PROGRAMMING CONSIDERATIONS

### **EPROM Characteristics**

The 87C748 is programmed by using a modified Quick-Pulse Programming algorithm similar to that used for devices such as the 87C451 and 87C51. It differs from these devices in that a serial data stream is used to place the 87C748 in the programming mode.

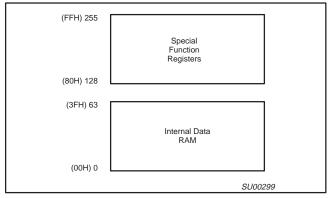

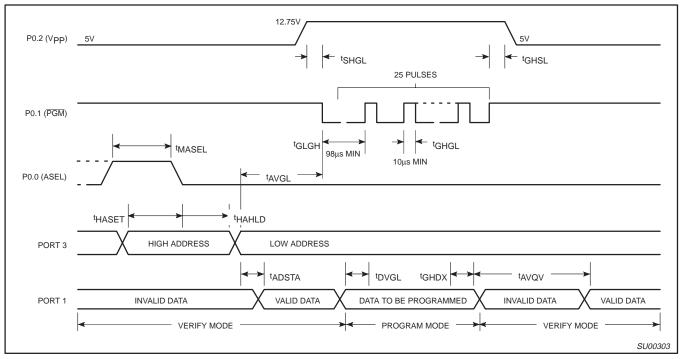

Figure 5 shows a block diagram of the programming configuration for the 87C748. Port pin P0.2 is used as the programming voltage supply input ( $V_{PP}$  signal). Port pin P0.1 is used as the program (PGM/) signal. This pin is used for the 25 programming pulses.

Port 3 is used as the address input for the byte to be programmed and accepts both the high and low components of the eleven bit address. Multiplexing of these address components is performed using the ASEL input. The user should drive the ASEL input high and then drive port 3 with the high order bits of the address. ASEL should remain high for at least 13 clock cycles. ASEL may then be driven low which latches the high order bits of the address internally. the high address should remain on port 3 for at least two clock cycles after ASEL is driven low. Port 3 may then be driven with the low byte of the address. The low address will be internally stable 13 clock cycles later. The address will remain stable provided that the low byte placed on port 3 is held stable and ASEL is kept low. **Note:** ASEL needs to be pulsed high only to change the high byte of the address.

Port 1 is used as a bidirectional data bus during programming and verify operations. During programming mode, it accepts the byte to be programmed. During verify mode, it provides the contents of the EPROM location specified by the address which has been supplied to Port 3.

The XTAL1 pin is the oscillator input and receives the master system clock. This clock should be between 1.2 and 6MHz.

The RESET pin is used to accept the serial data stream that places the 87C748 into various programming modes. This pattern consists of a 10-bit code with the LSB sent first. Each bit is synchronized to the clock input, X1.

#### **Programming Operation**

Figures 6 and 7 show the timing diagrams for the program/verify cycle. RESET should initially be held high for at least two machine cycles. P0.1 (PGM/) and P0.2 (V<sub>PP</sub>) will be at V<sub>OH</sub> as a result of the RESET operation. At this point, these pins function as normal quasi-bidirectional I/O ports and the programming equipment may pull these lines low. However, prior to sending the 10-bit code on the RESET pin, the programming equipment should drive these pins high (V<sub>IH</sub>). The RESET pin may now be used as the serial data input for the data stream which places the 87C748 in the programming mode. Data bits are sampled during the clock high time and thus should only change during the time that the clock is low. Following transmission of the last data bit, the RESET pin should be held low.

Next the address information for the location to be programmed is placed on port 3 and ASEL is used to perform the address multiplexing, as previously described. At this time, port 1 functions as an output.

A high voltage  $V_{PP}$  level is then applied to the  $V_{PP}$  input (P0.2). (This sets Port 1 as an input port). The data to be programmed into the EPROM array is then placed on Port 1. This is followed by a series of programming pulses applied to the PGM/ pin (P0.1). These pulses are created by driving P0.1 low and then high. This pulse is repeated until a total of 25 programming pulses have occurred. At the conclusion of the last pulse, the PGM/ signal should remain high.