# 256Mb Synchronous DRAM Specification

# **A3V56S30FTP A3V56S40FTP**

**Zentel Electronics Corp.**

Revision 1.1 Mar., 2010

# A3V56S30FTP A3V56S40FTP 256M Single Data Rate Synchronous DRAM

## **General Description**

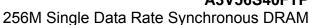

A3V56S30FTP is organized as 4-bank x 8,388,608-word x 8-bit Synchronous DRAM with LVTTL interface and A3V56S40FTP is organized as 4-bank x 4,194,304-word x 16-bit. All inputs and outputs are referenced to the rising edge of CLK. A3V56S30FTP and A3V56S40FTP achieve very high speed data rates up to 166MHz, and are suitable for main memories or graphic memories in computer systems.

#### **Features**

- Single 3.3V ±0.3V power supply

- Maximum clock frequency :

- 6:166MHz<3-3-3>/-7:143MHz<3-3-3>/-75:133MHz<3-3-3>

- Fully synchronous operation referenced to clock rising edge

- 4-bank operation controlled by BA0, BA1 (Bank Address)

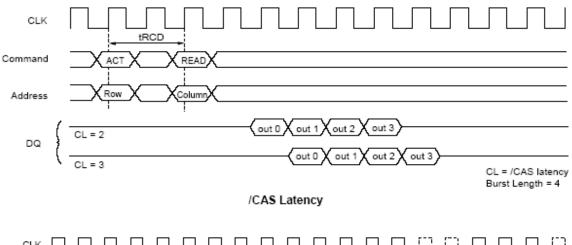

- /CAS latency- 2/3 (programmable)

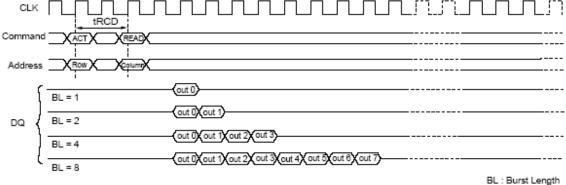

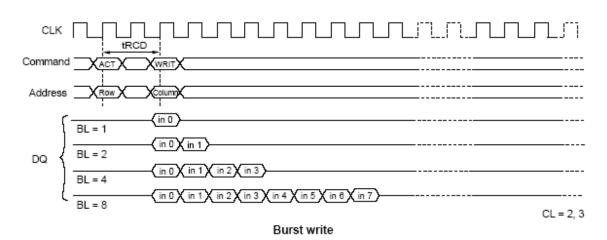

- Burst length- 1/2/4/8/FP (programmable)

- Burst type- Sequential and interleave burst (programmable)

- Byte Control- DQM (A3V56S30FTP), DQML and DQMU (A3V56S40FTP)

- Random column access

- Auto precharge / All bank precharge controlled by A10

- Support concurrent auto-precharge

- Auto and self refresh

- 8192 refresh cycles /64ms

- LVTTL Interface

- Package

400-mil, 54-pin Thin Small Outline (TSOP II) with 0.8mm lead pitch Pb-free package is available

### **Ordering Information**

54Pin TSOPII (400mil x 875mil)

| 011 11 1001 11 (10011 | III X 07 OITIII) |                |

|-----------------------|------------------|----------------|

| Part No.              | Max. Frequency   | Supply Voltage |

| A3V56S30FTP-G6        | 166MHz (CL=3)    | 3.3V           |

| A3V56S30FTP-G7        | 143MHz (CL=3)    | 3.3V           |

| A3V56S30FTP-G75       | 133MHz (CL=3)    | 3.3V           |

| A3V56S40FTP-G6        | 166MHz (CL=3)    | 3.3V           |

| A3V56S40FTP-G7        | 143MHz (CL=3)    | 3.3V           |

| A3V56S40FTP-G75       | 133MHz (CL=3)    | 3.3V           |

Zentel Electronics reserves the right to change products or specification without notice.

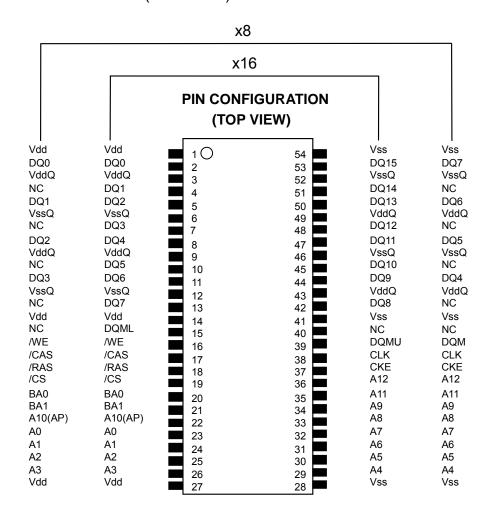

## PIN CONFIGURATION (TOP VIEW)

CLK : Master Clock DQM : Output Disable / Write Mask (A3V56S30FTP)

CKE : Clock Enable DQMU,L : Output Disable / Write Mask (A3V56S40FTP)

/CS: Chip SelectA0-12: Address Input/RAS: Row Address StrobeBA0,1: Bank Address/CAS: Column Address StrobeVdd: Power Supply

/WE : Write Enable VddQ : Power Supply for Output

DQ0-7 : Data I/O (A3V56S30FTP) Vss : Ground

Note: This figure shows the A3V56S30FTP The A3V56S40FTP configuration is 8192x512x16 of cell array and DQ0-15

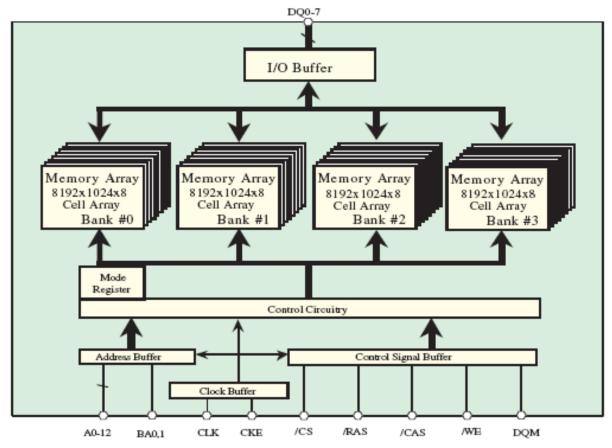

## **Type Designation Code**

| Pin Desci              | riptions |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL                 | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLK                    | Input    | Clock: CLK is driven by the system clock. All SDRAM input signals are sampled on the positive edge of CLK. CLK also increments the internal burst counter and controls the output registers.                                                                                                                                                                                                                                                                                                                                                       |

| CKE                    | Input    | Clock Enable: CKE activates (HIGH) and deactivates (LOW) the CLK signal. Deactivating the clock provides PRECHARGE POWER-DOWN and SELF REFRESH operation (all banks idle), ACTIVE POWER-DOWN (row active in any bank), or CLOCK SUSPEND operation (burst / access in progress). CKE is synchronous except after the device enters self refresh mode, where CKE becomes asynchronous until after exiting the same mode. The input buffers, including CLK, are disabled during self refresh mode, providing low standby power. CKE may be tied HIGH. |

| /CS                    | Input    | Chip Select: /CS enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when /CS is registered HIGH. /CS provides for external bank selection on systems with multiple banks. /CS is considered part of the command code.                                                                                                                                                                                                                                                                            |

| /CAS,<br>/RAS,<br>/WE  | Input    | Command Inputs: /CAS, /RAS, and /WE (along with /CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQM,<br>DQML,<br>DQMU, | Input    | Input / Output Mask: DQM is sampled HIGH and is an input mask signal for write accesses and an output disable signal for read accesses. Input data is masked during a WRITE cycle. The output buffers are placed in a High-Z state (two-clock latency) when during a READ cycle. DQM corresponds to DQ0–DQ7 (A3V56S30FTP). DQML corresponds to DQ0–DQ7, DQMU corresponds to DQ8–DQ15 (A3V56S40FTP).                                                                                                                                                |

| BA0, BA1               | Input    | Bank Address Input(s): BA0 and BA1 define to which bank the ACTIVE, READ, WRITE or PRECHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A0-A12                 | Input    | A0-12 specify the Row / Column Address in conjunction with BA0,1. The Row Address is specified by A0-12. The Column Address is specified by A0-9(x8) and A0-8(x16). A10 is also used to indicate precharge option. When A10 is high at a read / write command, an auto precharge is performed. When A10 is high at a precharge command, all banks are precharged.                                                                                                                                                                                  |

| DQ0-DQ15               | I/O      | Data Input / Output: Data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NC                     | -        | Internally Not Connected: These could be left unconnected, but it is recommended they be connected or Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VddQ                   | Supply   | Data Output Power: Provide isolated power to output buffers for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VssQ                   | Supply   | Data Output Ground: Provide isolated ground to output buffers for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vdd                    | Supply   | Power for the input buffers and core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vss                    | Supply   | Ground for the input buffers and core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                             | Symbol    | Value      | Unit |

|---------------------------------------|-----------|------------|------|

| Voltage on any pin relative to Vss    | Vin,Vout  | -1.0 ~ 4.6 | V    |

| Voltage on VDD supply relative to Vss | Vdd, VddQ | -1.0 ~ 4.6 | V    |

| Storage temperature                   | Тѕтс      | -55 ~ +150 | °C   |

| Operating ambient temperature         | Та        | 0 ~ 70     | °C   |

| Power dissipation                     | Pb        | 1.0        | W    |

| Short circuit current                 | los       | 50         | mA   |

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition. Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

#### DC OPERATING CONDITIONS

Recommended operating conditions (Voltage referenced to Vss = 0V, TA = 0 to 70°C)

| Parameter                 | Symbol | Min  | Тур | Max       | Unit | Note         |

|---------------------------|--------|------|-----|-----------|------|--------------|

| Cumply voltage            | Vdd    | 3.0  | 3.3 | 3.6       | V    |              |

| Supply voltage            | VddQ   | 3.0  | 3.3 | 3.6       | V    |              |

| Input logic high voltage  | Vih    | 2.0  | Vdd | Vdd + 0.3 | V    | 1            |

| Input logic low voltage   | VIL    | -0.3 | 0   | 0.8       | V    | 2            |

| Output logic high voltage | Vон    | 2.4  | -   | -         | V    | Iон = -0.1mA |

| Output logic low voltage  | Vol    | -    | -   | 0.4       | V    | IoL = 0.1mA  |

| Input leakage current     | lıL    | -10  | -   | 10        | uA   | 3            |

| Output leakage current    | loL    | -10  | -   | 10        | uA   | 3            |

- 1. VIH(max) = 4.6V AC for pulse width ≤ 10ns acceptable.

- 2. VIL(min) = -1.5V AC for pulse width ≤ 10ns acceptable.

3. Any input 0V ≤ VIN ≤ VDD + 0.3V, all other pins are not under test = 0V.

4. Dout is disabled , 0V ≤ VOUT ≤ VDD.

#### **CAPACITANCE** (Vdd = VddQ = 3.3V, T<sub>A</sub> = 25°C, f = 1MHz, pin under test biased at 1.4V.)

| Parameter                    | Symbol | Min | Max | Unit | Note |

|------------------------------|--------|-----|-----|------|------|

| Clock                        | Cclk   | 2   | 3.5 | pF   |      |

| /CAS,/RAS,/WE,/CS,CKE,DQMU/L | Cin    | 2   | 3.5 | pF   |      |

| Address                      | Cadd   | 2   | 3.5 | pF   |      |

| DQ0~DQ15                     | Соит   | 3.5 | 5.5 | pF   |      |

## 256M Single Data Rate Synchronous DRAM

## **DC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted, Ta = 0 to 70°C)

| Parameter                                      | Symbol | Test Condition                                                                                    | Organization |     | Version |     | Unit   | Note |

|------------------------------------------------|--------|---------------------------------------------------------------------------------------------------|--------------|-----|---------|-----|--------|------|

| raiailletei                                    | Symbol | rest condition                                                                                    |              | -6  | -7      | -75 | Ollit  | Note |

| Operating Current                              | Icc1   | Burst length = 2<br>trc = trc(min)                                                                | X 8          | 105 | 105     | 100 | mA     | 1    |

| (One Bank Active)                              | 1001   | lo = 0 mA                                                                                         | X 16         | 110 | 110     | 105 | 1117 ( | ·    |

| Precharge Standby<br>Current in                | Icc2P  | CKE = VIL(max), tcc = 10ns                                                                        | X 8 / X 16   |     | 12      |     | mA     |      |

| power-down mode                                | Icc2PS | CKE & CLK = VI∟(max), tcc = ∞                                                                     | X 8 / X 16   |     | 5       |     | IIIA   |      |

| Precharge Standby<br>Current<br>non power-down | Icc2N  | CKE = VIH(min), CS = VIH(min),<br>tcc = 10ns<br>Input signals are changed one<br>time during 20ns | X 8 / X 16   |     | 38      |     | mA     |      |

| mode                                           | Icc2NS | CKE = Vih(min), CLK = Vil(max),<br>tcc = ∞<br>Input signals are stable                            | X 8 / X 16   |     | 28      |     |        |      |

| Active Standby<br>Current                      | ІссзР  | CKE = VIL(max), tcc = 10ns                                                                        | X 8 / X 16   |     | 35      |     | mA     |      |

| power-down mode<br>(One Bank Active)           | Icc3PS | CKE & CLK = Vi∟(max), tcc = ∞                                                                     | X 8 / X 16   |     | 20      |     |        |      |

| Active Standby<br>Current<br>non power-down    | ІссзN  | CKE = VIH(min), CS = VIH(min),<br>tcc = 10ns<br>Input signals are changed one<br>time during 20ns | X 8 / X 16   |     | 65      |     | mA     |      |

| mode<br>(One Bank Active)                      | Icc3NS | CKE = VIH(min), CLK = VIL(max),<br>tcc = ∞<br>Input signals are stable                            | X 8 / X 16   |     | 45      |     | 1117   |      |

| Operating Current<br>(Burst Mode)              | Icc4   | Io = 0 mA Page burst 4Banks Activated tccd = 2CLKs                                                | X 8 / X 16   | 105 | 100     | 95  | mA     | 1    |

| Refresh Current                                | Icc5   | tarfc = tarfc(min)                                                                                | X 8 / X 16   | 150 | 140     | 130 | mA     | 2    |

| Self Refresh Current                           | Icc6   | CKE = 0.2V                                                                                        | X 8 / X 16   | 6   | 6       | 6   | mA     |      |

### NOTES:

- 1. Measured with outputs open.

- Refresh period is 64ms.

Unless otherwise noted, input swing level is CMOS(VIH /VIL=VDDQ/VSSQ).

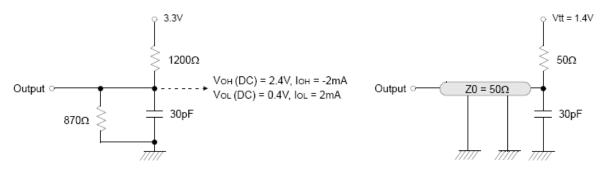

## AC OPERATING TEST CONDITIONS (VDD = VddQ = $3.3V \pm 0.3V$ , TA = 0 to $70^{\circ}$ C)

| Parameter                                 | Value        | Unit |

|-------------------------------------------|--------------|------|

| AC input levels (Vih/Vil)                 | 2.4 / 0.4    | V    |

| Input timing measurement reference level  | 1.4          | V    |

| Input rise and fall time                  | tr/tf = 1/1  | Ns   |

| Output timing measurement reference level | 1.4          | V    |

| Output load condition                     | See Figure 2 |      |

(Fig. 1) DC output load circuit

(Fig. 2) AC output load circuit

### **OPERATING AC PARAMETER**

| Parameter                              | Symbol     |     |     | Unit | Note |   |

|----------------------------------------|------------|-----|-----|------|------|---|

| r ai ailletei                          | Symbol     | -6  | -7  | -75  |      |   |

| Row active to row active delay         | trrd(min)  | 12  | 14  | 15   | ns   | 1 |

| RAS to CAS delay                       | trcd(min)  | 18  | 20  | 20   | ns   | 1 |

| Row precharge time                     | trp(min)   | 18  | 20  | 20   | ns   | 1 |

| Row active time                        | tras(min)  | 42  | 45  | 45   | ns   | 1 |

| Row active time                        | tras(max)  | 100 | 100 | 100  | us   |   |

| Row cycle time                         | trc(min)   | 60  | 63  | 65   | ns   | 1 |

| Last data in to row precharge          | trdl(min)  | 2   | 2   | 2    | CLK  | 2 |

| Last data in to Active delay           | tdal(min)  | 5   | 5   | 5    | CLK- |   |

| Last data in to new col. address delay | tcdl(min)  | 1   | 1   | 1    | CLK  | 2 |

| Last data in to burst stop             | tBDL(min)  | 1   | 1   | 1    | CLK  | 2 |

| Mode register set cycle time           | tmrd(min)  | 2   | 2   | 2    | CLK  |   |

| Refresh interval time                  | tref(max)  | 64  | 64  | 64   | ms   |   |

| Auto refresh cycle time                | tarfc(min) | 60  | 70  | 75   | ns   |   |

<sup>1.</sup> The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then rounding off to the next higher integer.

2. Minimum delay is required to complete write.

| AC CHARACTERIS            | STICS (AC operatin   | g conditions ι | unless oth | nerwise no |     |     |     |     |      |      |

|---------------------------|----------------------|----------------|------------|------------|-----|-----|-----|-----|------|------|

| Paramet                   | er                   | Symbol         | -          | 6          | -   | 7   | -7  | 75  | Unit | Note |

| T drumet                  |                      | Cymbol         | Min        | Max        | Min | Max | Min | Max | Omit | Note |

| CLK cycle time            | CAS latency=3        | tcc (3)        | 6          |            | 7   |     | 7.5 |     | ns   | 1    |

| OLIV CYCIE UITIE          | CAS latency=2        | tcc (2)        | 10         |            | 10  |     | 10  |     | 113  | '    |

| CLK to valid output delay | CAS latency=3        | tsac (3)       |            | 5.4        |     | 5.4 |     | 5.4 | 20   | 1,2  |

| CLK to valid output delay | CAS latency=2        | tsac (2)       |            | 5.4        |     | 5.4 |     | 6   | ns   | 1,2  |

| CAS latency               |                      | toh (3)        | 2.5        |            | 2.5 |     | 2.5 |     | ns   | 2    |

| Output data floid time    | CAS latency=2        | toh (2)        | 2.5        |            | 2.5 |     | 2.5 |     | 10   |      |

| CLK high pulse width      | CLK high pulse width |                | 2.5        |            | 2.5 |     | 2.5 |     | ns   | 3    |

| CLK low pulse width       |                      | tcL            | 2.5        |            | 2.5 |     | 2.5 |     | ns   | 3    |

| Input setup time          |                      | tsı            | 1.5        |            | 1.5 |     | 1.5 |     | ns   | 3    |

| Input hold time           |                      | tнı            | 1          |            | 1   |     | 1   |     | ns   | 3    |

| Transition time of CLK    |                      | tτ             | 0.3        | 1.5        | 0.3 | 1.5 | 0.3 | 1.5 | ns   |      |

| CLK to output in Low-Z    |                      | tsız           | 1          |            | 1   |     | 1   |     |      |      |

| CLK to output in Hi-Z     | CAS latency=3        | tsHz           |            | 5.4        |     | 5.4 |     | 5.4 | ns   |      |

| OLIV to output in Fin-2   | CAS latency=2        | ISHZ           |            | 5.4        |     | 5.4 |     | 6   | 115  |      |

<sup>1.</sup> Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.

## **TRUTH TABLE**

### **Command Truth Table**

| COMMAND                   | Symbol | CKEn-1 | CKEn | /CS | /RAS | /CAS | /WE | BA1 | BA0 | A10/<br>AP | A12-11,<br>A9 ~ A0 |

|---------------------------|--------|--------|------|-----|------|------|-----|-----|-----|------------|--------------------|

| Device deselect           | DSL    | Н      | Χ    | Н   | Χ    | Χ    | Χ   | Χ   | Χ   | Χ          | Χ                  |

| No operation              | NOP    | Н      | Χ    | L   | Н    | Н    | Н   | Χ   | Χ   | Χ          | Χ                  |

| Burst stop                | BST    | Н      | Χ    | L   | Н    | Н    | L   | Χ   | Χ   | Χ          | Χ                  |

| Read                      | RD     | Н      | Χ    | L   | Н    | L    | Н   | V   | V   | L          | V                  |

| Read with auto precharge  | RDA    | Н      | Χ    | L   | Н    | L    | Н   | V   | V   | Н          | V                  |

| Write                     | WR     | Н      | Χ    | L   | Н    | L    | L   | V   | V   | L          | V                  |

| Write with auto precharge | WRA    | Н      | Χ    | L   | Н    | L    | L   | V   | V   | Н          | V                  |

| Bank activate             | ACT    | Н      | Χ    | L   | L    | Н    | Н   | V   | V   | V          | V                  |

| Precharge select bank     | PRE    | Н      | Χ    | L   | L    | Н    | L   | V   | V   | L          | X                  |

| Precharge all banks       | PALL   | Н      | Χ    | L   | L    | Н    | L   | Χ   | Χ   | Н          | Χ                  |

| Mode register set         | MRS    | Н      | X    | L   | L    | L    | L   | L   | L   | L          | OP code            |

<sup>(</sup>V=Valid, X=Don't Care, H=Logic High, L=Logic Low)

## **CKE Truth Table**

| Current state                         | Function                                 | Symbol | CKEn-1 | CKEn | /CS | /RAS | /CAS | /WE | /Address |

|---------------------------------------|------------------------------------------|--------|--------|------|-----|------|------|-----|----------|

| Activating                            | Enter Clock suspend or                   |        | Н      | L    | L   | V    | V    | V   | V        |

| Activating                            | Active power down                        |        | Н      | L    | Н   | Χ    | Χ    | Χ   | Х        |

| Clock suspend or<br>Active power down |                                          | L      | L      | Х    | Х   | Х    | Х    | Х   |          |

| Clock suspend or                      | Active power down  Exit Clock suspend or |        |        |      |     |      |      |     |          |

| Active power down                     | Active power down                        |        | L      | Н    | Х   | Х    | Х    | X   | Х        |

| All banks idle                        | Auto refresh command                     |        | Н      | Н    | L   | L    | L    | Н   | Χ        |

| All banks idle Enter Self refresh     |                                          | SREF   | Н      | L    | L   | L    | L    | Н   | Χ        |

| All banks idla                        | Enter Procharge newer down               |        | Н      | L    | L   | Н    | Н    | Н   | Χ        |

| All banks idle                        | Enter Precharge power down               |        | Н      | L    | Н   | Χ    | Χ    | Χ   | Х        |

| Self refresh                          | Exit Self refresh                        |        | L      | Н    | L   | Н    | Н    | Н   | Х        |

| Sell refresh                          | Exit Sell Tellesii                       |        | L      | Н    | Н   | Χ    | Χ    | Χ   | Х        |

| Precharge power                       | Evit Drochago nover down                 |        | L      | Н    | L   | Н    | Н    | Н   | Х        |

| down                                  | Exit Prechage power down                 |        | L      | Н    | Н   | Х    | Х    | Х   | Х        |

| Precharge power down                  | Maintain Precharge power down            |        | L      | L    | Х   | Х    | Х    | Х   | х        |

<sup>(</sup>V=Valid, X=Don't Care, H=Logic High, L=Logic Low)

## 256M Single Data Rate Synchronous DRAM

## **Function Truth Table**

| Current state   | /CS          | /RAS | /CAS | /WE      | /Address  | Command  | Action                                     | Notes |

|-----------------|--------------|------|------|----------|-----------|----------|--------------------------------------------|-------|

| Idle            | <u>H</u>     | X    | Χ    | Χ        | X         | DESL     | NOP                                        |       |

|                 | _L           | Н    | Н    | Н        | X         | NOP      | NOP                                        |       |

|                 | <u> </u>     | Н    | Н    | L        | X         | BST      | ILLEGAL                                    | 2     |

|                 | <u> </u>     | Н    | L    | Н        | BA,CA,A10 | RD/RDA   | ILLEGAL                                    | 2     |

|                 | <u> </u>     | Н    | L    | L        | BA,CA,A10 | WR/WRA   | ILLEGAL                                    | 2     |

|                 | <u> </u>     | L    | Н    | Н        | BA,RA     | ACT      | Bank active                                |       |

|                 | L            | L    | Н    | L        | BA,A10    | PRE/PALL | NOP                                        | 4     |

|                 | L            | L    | L    | Н        | X         | REF      | Auto refresh                               | 5     |

|                 | L            | L    | L    | L        | OC        | MRS      | Mode register set                          | 5     |

| Row active      | <u>H</u>     | X    | Χ    | Χ        | Χ         | DESL     | NOP                                        |       |

|                 | L            | Н    | Н    | Н        | X         | NOP      | NOP                                        |       |

|                 | <u> </u>     | Н    | Н    | L        | X         | BST      | ILLEGAL                                    | 2     |

|                 | L            | Н    | L    | Н        | BA,CA,A10 | RD/RDA   | Begin read, determine AP                   |       |

|                 | L            | Н    | L    | L        | BA,CA,A10 | WR/WRA   | Begin write, determine AP                  |       |

|                 | L            | L    | Н    | Н        | BA,RA     | ACT      | Bank active / ILLEGAL                      | 2     |

|                 | L            | L    | Н    | L        | BA,A10    | PRE/PALL | Precharge / Precharge all banks            |       |

|                 | L            | L    | L    | Н        | Χ         | REF      | ILLEGAL                                    |       |

|                 | L            | L    | L    | L        | OC        | MRS      | ILLEGAL                                    |       |

| Read            | <u>H</u>     | Χ    | Χ    | Χ        | X         | DESL     | Continue burst to end                      |       |

|                 | L            | Н    | Н    | Н        | Χ         | NOP      | Continue burst to end                      |       |

|                 | L            | Н    | Н    | L        | Χ         | BST      | Terminate burst                            |       |

|                 | L            | Н    | L    | Н        | BA,CA,A10 | RD/RDA   | Terminate burst, begin read, determine AP  | 3     |

|                 | L            | Н    | L    | L        | BA,CA,A10 | WR/WRA   | Terminate burst, begin write, determine AP | 3     |

|                 | L            | L    | Н    | Н        | BA,RA     | ACT      | Bank active / ILLEGAL                      | 2     |

| _               | L            | L    | Н    | L        | BA,A10    | PRE/PALL | Terminate burst, precharge                 |       |

|                 | L            | L    | L    | Н        | Χ         | REF      | ILLEGAL                                    |       |

|                 | L            | L    | L    | L        | OC        | MRS      | ILLEGAL                                    |       |

| Write           | Н            | Χ    | Χ    | Χ        | Χ         | DESL     | Continue burst to end                      |       |

|                 | L            | Н    | Н    | Н        | Χ         | NOP      | Continue burst to end                      |       |

|                 | L            | Н    | Н    | L        | Χ         | BST      | Terminate burst                            |       |

|                 | L            | Н    | L    | Н        | BA,CA,A10 | RD/RDA   | Terminate burst, begin read, determine AP  | 3     |

|                 | L            | Н    | L    | L        | BA,CA,A10 | WR/WRA   | Terminate burst, begin write, determine AP | 3     |

|                 | L            | L    | Н    | Н        | BA,RA     | ACT      | Bank active / ILLEGAL                      | 2     |

|                 | L            | L    | Н    | L        | BA,A10    | PRE/PALL | Terminate burst, precharge                 |       |

|                 | L            | L    | L    | Н        | Χ         | REF      | ILLEGAL                                    |       |

|                 | L            | L    | L    | L        | OC        | MRS      | ILLEGAL                                    |       |

| Read with auto  | Н            | Χ    | Χ    | Χ        | Χ         | DESL     | Continue burst to end                      |       |

| orecharge       | L            | Н    | Н    | Н        | Χ         | NOP      | Continue burst to end                      |       |

|                 | L            | Н    | Н    | L        | Χ         | BST      | ILLEGAL                                    |       |

|                 | L            | Н    | L    | Н        | BA,CA,A10 | RD/RDA   | Support concurrent auto-precharge          | 2     |

|                 | L            | Н    | L    | L        | BA,CA,A10 | WR/WRA   | Support concurrent auto-precharge          | 2     |

|                 | L            | L    | Н    | Н        | BA,RA     | ACT      | Bank active / ILLEGAL                      | 2     |

|                 | L            | L    | Н    | L        | BA,A10    | PRE/PALL | ILLEGAL                                    | 2     |

|                 | L            | L    | L    | Н        | Χ         | REF      | ILLEGAL                                    |       |

|                 | L            | L    | L    | L        | OC        | MRS      | ILLEGAL                                    |       |

| Write with auto | Н            | Х    | Х    | Х        | X         | DESL     | Continue burst to end                      |       |

| precharge       | L            | Н    | Н    | Н        | X         | NOP      | Continue burst to end                      |       |

| . 3             | Ī            | H    | H    | L L      | X         | BST      | ILLEGAL                                    |       |

|                 | 亡            | H    | L    | H        | BA,CA,A10 | RD/RDA   | Support concurrent auto-precharge          | 2     |

|                 | 亡            | H    | L    | L.       | BA,CA,A10 | WR/WRA   | Support concurrent auto-precharge          | 2     |

|                 | Ť            | L    | H    | H        | BA,RA     | ACT      | Bank active / ILLEGAL                      | 2     |

|                 | 一            | L    | H    | <u> </u> | BA,A10    | PRE/PALL | ILLEGAL                                    | 2     |

|                 | <del>-</del> | L    | L    | H        | X         | REF      | ILLEGAL                                    |       |

|                 |              |      |      |          |           |          |                                            |       |

# **A3V56S30FTP A3V56S40FTP**

## 256M Single Data Rate Synchronous DRAM

| Current state  | /CS | /RAS     | /CAS | /WE | /Address  | Command  | Action                     | Notes |

|----------------|-----|----------|------|-----|-----------|----------|----------------------------|-------|

| Precharging    | Н   | Χ        | Χ    | Χ   | Χ         | DESL     | NOP, idle after tRP        |       |

|                | L   | Н        | Н    | Н   | Χ         | NOP      | NOP, idle after tRP        |       |

|                | L   | Н        | Н    | L   | Χ         | BST      | ILLEGAL                    | 2     |

|                | L   | Н        | L    | Н   | BA,CA,A10 | RD/RDA   | ILLEGAL                    | 2     |

|                | L   | Н        | L    | L   | BA,CA,A10 | WR/WRA   | ILLEGAL                    | 2     |

|                | L   | L        | Н    | Н   | BA,RA     | ACT      | Bank active / ILLEGAL      | 2     |

|                | L   | L        | Н    | L   | BA,A10    | PRE/PALL | Nop, idle after tRP        | 4     |

|                | L   | L        | L    | Н   | Χ         | REF      | ILLEGAL                    |       |

|                | L   | L        | L    | L   | OC        | MRS      | ILLEGAL                    |       |

| Row activating | Н   | Х        | Х    | Х   | Χ         | DESL     | NOP, row active after tRCD |       |

| · ·            | L   | Н        | Н    | Н   | Х         | NOP      | NOP, row active after tRCD |       |

|                | L   | Н        | Н    | L   | Х         | BST      | ILLEGAL                    | 2     |

|                | L   | Н        | L    | Н   | BA,CA,A10 | RD/RDA   | ILLEGAL                    | 2     |

|                | L   | Н        | L    | L   | BA,CA,A10 | WR/WRA   | ILLEGAL                    | 2     |

|                | L   | L        | Н    | Н   | BA,RA     | ACT      | ILLEGAL                    | 2     |

|                | L   | L        | Н    | L   | BA,A10    | PRE/PALL | ILLEGAL                    | 2     |

|                | L   | L        | L    | Н   | Χ         | REF      | ILLEGAL                    |       |

|                | L   | L        | L    | L   | OC        | MRS      | ILLEGAL                    |       |

| Write          | Н   | Χ        | Χ    | Х   | Х         | DESL     | NOP                        |       |

| recovering     | L   | Н        | Н    | Н   | Х         | NOP      | NOP                        |       |

|                | L   | Н        | Н    | L   | Х         | BST      | ILLEGAL                    | 2     |

|                | L   | Н        | L    | Н   | BA,CA,A10 | RD/RDA   | Begin read, determine AP   |       |

|                | L   | Н        | L    | L   | BA,CA,A10 | WR/WRA   | Begin write, determine AP  |       |

|                | L   | L        | Н    | Н   | BA,RA     | ACT      | ILLEGAL                    | 2     |

|                | L   | L        | Н    | L   | BA,A10    | PRE/PALL | ILLEGAL                    | 2     |

|                | L   | L        | L    | Н   | X         | REF      | ILLEGAL                    |       |

|                | L   | L        | L    | L   | OC        | MRS      | ILLEGAL                    |       |

| Refreshing     | Н   | Х        | Х    | Х   | X         | DESL     | NOP, idle after tARFC      |       |

| 3              | L   | Н        | Н    | Н   | Х         | NOP      | NOP, idle after tARFC      |       |

|                | L   | Н        | Н    | L   | Х         | BST      | ILLEGAL                    |       |

|                | L   | Н        | L    | Н   | BA,CA,A10 | RD/RDA   | ILLEGAL                    |       |

|                | L   | Н        | L    | L   | BA,CA,A10 | WR/WRA   | ILLEGAL                    |       |

|                | L   | L        | Н    | Н   | BA,RA     | ACT      | ILLEGAL                    |       |

|                | L   | L        | Н    | L   | BA,A10    | PRE/PALL | ILLEGAL                    |       |

|                | L   | L        | L    | Н   | X         | REF      | ILLEGAL                    |       |

|                | L   | L        | L    | L   | OC        | MRS      | ILLEGAL                    |       |

| Mode register  | Н   | Х        | Χ    | Х   | X         | DESL     | NOP, idle after tMRD       |       |

| accessing      | L   | H        | Н    | Н   | X         | NOP      | NOP, idle after tMRD       |       |

| 3              | ī   | Н        | Н    | Ĺ   | X         | BST      | ILLEGAL                    |       |

|                | L   | H        | Ĺ    |     | BA,CA,A10 | RD/RDA   | ILLEGAL                    |       |

|                | ī   | H        | -Ē   | - L | BA,CA,A10 | WR/WRA   | ILLEGAL                    |       |

|                | ī   | <u> </u> | H    | H   | BA,RA     | ACT      | ILLEGAL                    |       |

|                | ī   | Ĺ        | H    | L   | BA,A10    | PRE/PALL | ILLEGAL                    |       |

|                | ī   | L        | L.   | H   | X         | REF      | ILLEGAL                    |       |

|                |     | <u> </u> | L    | L   | OC        | MRS      | ILLEGAL                    |       |

## A3V56S30FTP A3V56S40FTP 256M Single Data Rate Synchronous DRAM

- Notes: 1. All entries assumes that CKE was High during the preceding clock cycle and the current clock cycle.

2. ILLEGAL to the bank in specified state; function may be legal in the bank indicated by BA, depending on the state of that bank.

- 3. Must satisfy bus contention, bus turn around, write recovery requirements.

- 4. NOP to bank precharging or in idle state. May precharge bank indicated by BA.

- 5. ILLEGAL if any bank is not idle.

ILLEGAL: Device operation and/or data-integrity are not guaranteed.

## A3V56S30FTP A3V56S40FTP

## 256M Single Data Rate Synchronous DRAM

#### MODE REGISTER FIELD TABLE TO PROGRAM MODES

Register Programmed with Normal MRS

| Address  | BA0 | BA1 | A12 | A11 | A10/AP | A9 | A8 | A7 | A6          | A5 | A4 | А3           | A2 | A1  | Α0 |

|----------|-----|-----|-----|-----|--------|----|----|----|-------------|----|----|--------------|----|-----|----|

| Function | 0   | 0   | 0   | 0   | 0      | WB | 0  | 0  | CAS Latency |    | ВТ | Burst Length |    | gth |    |

#### **MRS Mode**

|    | CAS Latency |    |          | Burst Type |            |    |    | В  | urst Length | Write Burst Mode |    |                         |

|----|-------------|----|----------|------------|------------|----|----|----|-------------|------------------|----|-------------------------|

| A6 | A5          | A4 | Latency  | A3         | Туре       | A2 | A1 | A0 | BT=0        | BT=1             | A9 | Туре                    |

| 0  | 0           | 0  | Reserved | 0          | Sequential | 0  | 0  | 0  | 1           | 1                | 0  | Programmed Burst Length |

| 0  | 0           | 1  | Reserved | 1          | Interleave | 0  | 0  | 1  | 2           | 2                | 1  | Single Location Access  |

| 0  | 1           | 0  | 2        |            |            | 0  | 1  | 0  | 4           | 4                |    |                         |

| 0  | 1           | 1  | 3        |            |            | 0  | 1  | 1  | 8           | 8                |    |                         |

| 1  | 0           | 0  | Reserved |            |            | 1  | 0  | 0  | Reserved    | Reserved         |    |                         |

| 1  | 0           | 1  | Reserved |            |            | 1  | 0  | 1  | Reserved    | Reserved         |    |                         |

| 1  | 1           | 0  | Reserved |            |            | 1  | 1  | 0  | Reserved    | Reserved         |    |                         |

| 1  | 1           | 1  | Reserved |            |            | 1  | 1  | 1  | Full Page   | Reserved         |    |                         |

#### **BURST SEQUENCE**

| BURST LENGTH  | STARTING COLUMN                                       | ORDER OF ACCESSES WITHIN A BURST       |                  |  |  |  |  |

|---------------|-------------------------------------------------------|----------------------------------------|------------------|--|--|--|--|

|               | ADDRESS                                               | TYPE=SEQUENTIAL                        | TYPE=INTERLEAVED |  |  |  |  |

|               | A0                                                    |                                        |                  |  |  |  |  |

| 2             | 0                                                     | 0-1                                    | 0-1              |  |  |  |  |

|               | 1                                                     | 1-0                                    | 1-0              |  |  |  |  |

|               | A1 A0                                                 |                                        |                  |  |  |  |  |

|               | 0 0                                                   | 0-1-2-3                                | 0-1-2-3          |  |  |  |  |

| 4             | 0 1                                                   | 1-2-3-0                                | 1-0-3-2          |  |  |  |  |

|               | 1 0                                                   | 2-3-0-1                                | 2-3-0-1          |  |  |  |  |

|               | 1 1                                                   | 3-0-1-2                                | 3-2-1-0          |  |  |  |  |

|               | A2 A1 A0                                              |                                        |                  |  |  |  |  |

|               | 0 0 0                                                 | 0-1-2-3-4-5-6-7                        | 0-1-2-3-4-5-6-7  |  |  |  |  |

|               | 0 0 1                                                 | 1-2-3-4-5-6-7-0                        | 1-0-3-2-5-4-7-6  |  |  |  |  |

|               | 0 1 0                                                 | 2-3-4-5-6-7-0-1                        | 2-3-0-1-6-7-4-5  |  |  |  |  |

| 8             | 0 1 1                                                 | 3-4-5-6-7-0-1-2                        | 3-2-1-0-7-6-5-4  |  |  |  |  |

|               | 1 0 0                                                 | 4-5-6-7-0-1-2-3                        | 4-5-6-7-0-1-2-3  |  |  |  |  |

|               | 1 0 1                                                 | 5-6-7-0-1-2-3-4                        | 5-4-7-6-1-0-3-2  |  |  |  |  |

|               | 1 1 0                                                 | 6-7-0-1-2-3-4-5                        | 6-7-4-5-2-3-0-1  |  |  |  |  |

|               | 1 1 1                                                 | 7-0-1-2-3-4-5-6                        | 7-6-5-4-3-2-1-0  |  |  |  |  |

| Full Page (y) | N=A0 - A9 (x8)<br>N=A0 - A8 (x16)<br>(location 0 - y) | Cn, Cn+1, Cn+2, Cn+3,<br>Cn+4,Cn-1, Cn | Not Supported    |  |  |  |  |

- 1. For full-page accesses: y = 1023 (x8), 511 (x16).

- For a burst length of two, A1–A9(A8) select the block-of-two burst; A0 selects the starting column within the block.

For a burst length of four, A2–A9(A8) select the block-of-four burst; A0–A1 select the starting column within the block.

For a burst length of eight, A3–A9(A8) select the block-of-eight burst; A0–A2 select the starting column within the block.

For a full-page burst, the full row is selected and A0–A9(A8) select the starting column.

- 6. Whenever a boundary of the block is reached within a given sequence above, the following access wraps within the block.

- 7. For a burst length of one, A0-A9(A8) select the unique column to be accessed, and mode register bit A3 is ignored.

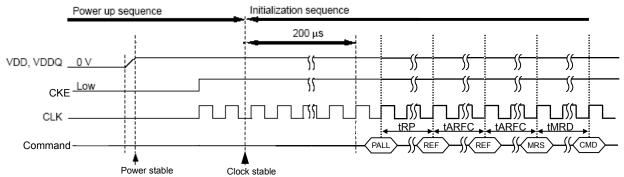

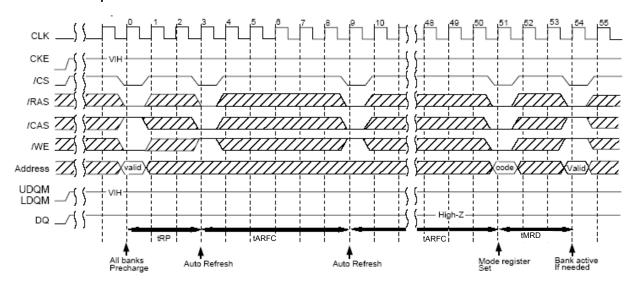

#### Power-up sequence

#### Power-up sequence

- 1. Apply VDD and VDDQ at the same time. Keep CKE low during power up.

- 2. Wait for stable power.

- 3. Start clock and drive CKE high.

Note: Voltage on any input pin must not exceed VDD+0.3V during power up.

#### Initialization sequence

- 4. After stable power and stable clock, wait 200us.

- 5. Issue precharge all command (PALL).

- 6. After tRP delay, set 2 or more auto refresh commands (REF).

- 7. Set the mode register set command (MRS) to initialize the mode register.

Note: We recommend that you keep DQM and CKE high during initialization sequence to prevent data contention on the DQ bus.

Power-up sequence and Initialization sequence

/CAS Latency = 2

#### Operation of the SDRAM

#### **Read/Write Operations**

#### Bank active

Before executing a read or write operation, the corresponding bank and the row address must be activated by the bank active (ACT) command. An interval of tRCD is required between the bank active command input and the following read/write command input.

#### Read operation

A read operation starts when a read command is input. Output buffer becomes Low-Z in the (/CAS Latency - 1) cycle after read command set. The SDRAM can perform a burst read operation.

The burst length can be set to 1, 2, 4 and 8. The start address for a burst read is specified by the column address and the bank select address at the read command set cycle. In a read operation, data output starts after the number of clocks specified by the /CAS Latency. The /CAS Latency can be set to 2 or 3.

When the burst length is 1, 2, 4 and 8 the DOUT buffer automatically becomes High-Z at the next clock after the successive burst-length data has been output.

The /CAS latency and burst length must be specified at the mode register.

Burst Length

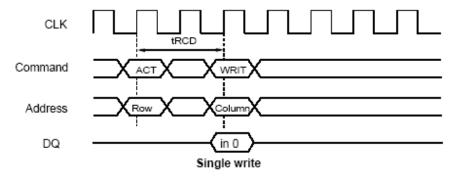

#### Write operation

Burst write or single write mode is selected

1. Burst write: A burst write operation is enabled by setting OPCODE A9 to 0. A burst write starts in the same clock as a write command set. (The latency of data input is 0 clock.) The burst length can be set to 1, 2, 4 and 8, like burst read operations. The write start address is specified by the column address and the bank select address at the write command set cycle.

2. Single write: A single write operation is enabled by setting OPCODE A9 to 1. In a single write operation, data is only written to the column address and the bank select address specified by the write command set cycle without regard to the burst length setting. (The latency of data input is 0 clock).

# A3V56S30FTP A3V56S40FTP 256M Single Data Rate Synchronous DRAM

#### **Auto Precharge**

#### Read with auto-precharge

In this operation, since precharge is automatically performed after completing a read operation, a precharge command need not be executed after each read operation. The command executed for the same bank after the execution of this command must be the bank active (ACT) command.

The next ACT command can be issued at the later time of either tRP after internal precharge or tRC after the previous ACT.

#### Write with auto-precharge

In this operation, since precharge is automatically performed after completing a burst write or single write operation, a precharge command need not be executed after each write operation. The command executed for the same bank after the execution of this command must be the bank active (ACT) command.

The next ACT command can be issued at the later time of either tDAL from the last input data cycle or tRC after the previous ACT.

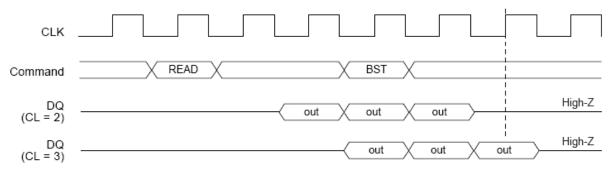

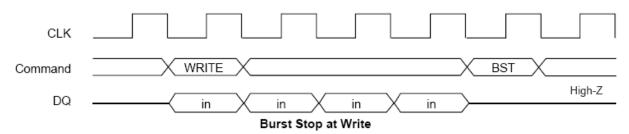

#### **Burst Stop Command**

During a read cycle, when the burst stop command is issued, the burst read data are terminated and the data bus goes to High-Z after the /CAS latency from the burst stop command.

**Burst Stop at Read**

During a write cycle, when the burst stop command is issued, the burst write data are terminated and data bus goes to High-Z at the same clock with the burst stop command.

#### **Command Intervals**

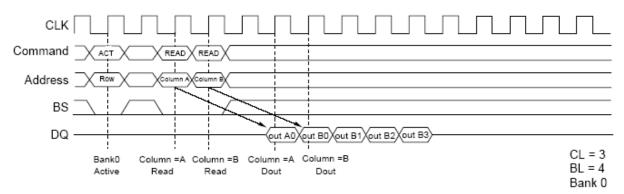

#### Read command to Read command interval

1. Same bank, same ROW address: When another read command is executed at the same ROW address of the same bank as the preceding read command execution, the second read can be performed after an interval of no less than 1 clock. Even when the first command is a burst read that is not yet finished, the data read by the second command will be valid.

READ to READ Command Interval (same ROW address in same bank)

- Same bank, different ROW address: When the ROW address changes on same bank, consecutive read commands cannot be executed; it is necessary to separate the two read commands with a precharge command and a bank active command.

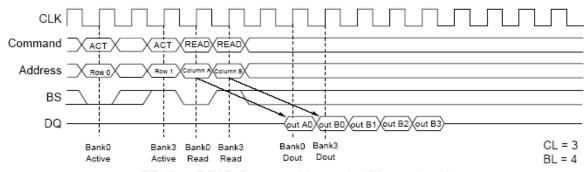

- 3. Different bank: When the bank changes, the second read can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank active state. Even when the first command is a burst read that is not yet finished, the data read by the second command will be valid.

READ to READ Command Interval (different bank)

#### Write command to Write command interval

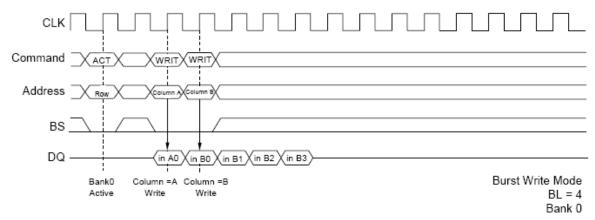

Same bank, same ROW address: When another write command is executed at the same ROW address of the same bank

as the preceding write command, the second write can be performed after an interval of no less than 1 clock. In the case of

burst writes, the second write command has priority.

WRITE to WRITE Command Interval (same ROW address in same bank)

- 2. Same bank, different ROW address: When the ROW address changes, consecutive write commands cannot be executed; it is necessary to separate the two write commands with a precharge command and a bank active command.

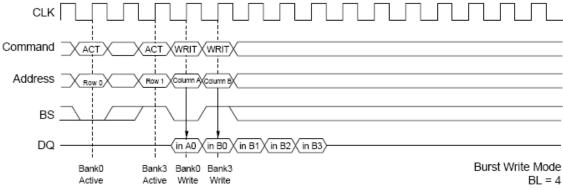

- 3. Different bank: When the bank changes, the second write can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank active state. In the case of burst write, the second write command has priority.

WRITE to WRITE Command Interval (different bank)

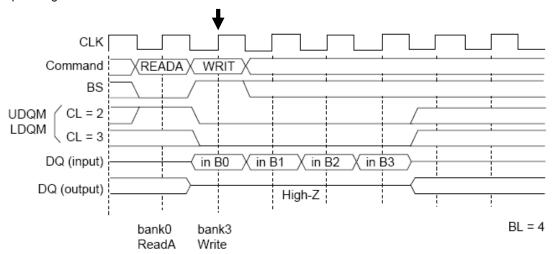

#### Read command to Write command interval

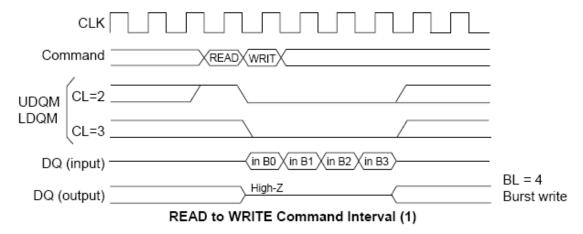

Same bank, same ROW address: When the write command is executed at the same ROW address of the same bank as

the preceding read command, the write command can be performed after an interval of no less than 1 clock. However,

DQMU and DQML must be set High so that the output buffer becomes High-Z before data input.

READ to WRITE Command Interval (2)

- 2. Same bank, different ROW address: When the ROW address changes, consecutive write commands cannot be executed; it is necessary to separate the two commands with a precharge command and a bank active command.

- 3. Different bank: When the bank changes, the write command can be performed after an interval of no less than 1 cycle, provided that the other bank is in the bank active state. However, DQMU and DQML must be set High so that the output buffer becomes High-Z before data input.

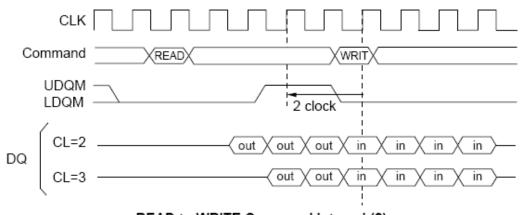

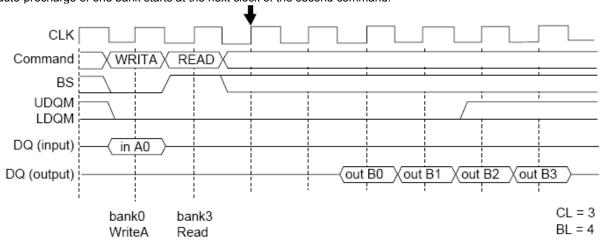

#### Write command to Read command interval:

1. Same bank, same ROW address: When the read command is executed at the same ROW address of the same bank as the preceding write command, the read command can be performed after an interval of no less than 1 clock. However, in the case of a burst write, data will continue to be written until one clock before the read command is executed.

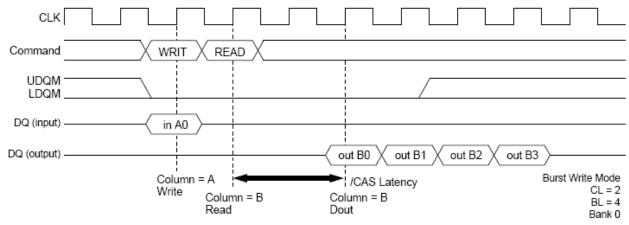

WRITE to READ Command Interval (1)

WRITE to READ Command Interval (2)

- 2. Same bank, different ROW address: When the ROW address changes, consecutive read commands cannot be executed; it is necessary to separate the two commands with a precharge command and a bank active command.

- 3. Different bank: When the bank changes, the read command can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank active state. However, in the case of a burst write, data will continue to be written until one clock before the read command is executed (as in the case of the same bank and the same address).

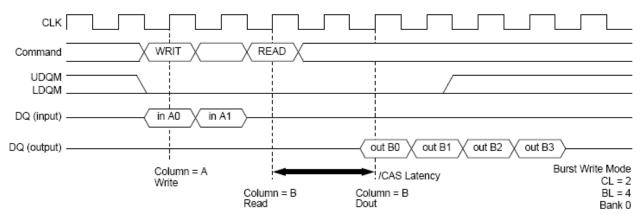

#### Read with auto precharge to Read command interval (concurrent auto-precharge)

1. Different bank: When some banks are in the active state, the second read command (another bank) is executed. Even when the first read with auto-precharge is a burst read that is not yet finished, the data read by the second command is valid. The internal auto-precharge of one bank starts at the clock of the second command.

Note: Internal auto-precharge starts at the timing indicated by "

#### Read with Auto Precharge to Read Command Interval (Different bank)

2. Same bank: The consecutive read command (the same bank) is illegal.

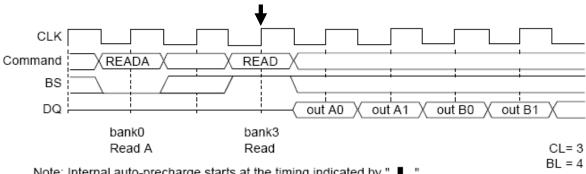

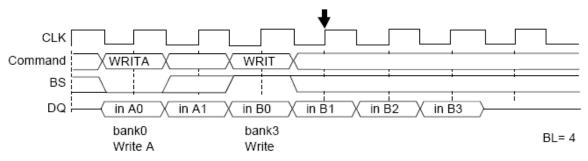

#### Write with auto precharge to Write command interval (concurrent auto-precharge)

1. Different bank: When some banks are in the active state, the second write command (another bank) is executed. In the case of burst writes, the second write command has priority. The internal auto-precharge of one bank starts at the next clock of the second command.

Note: Internal auto-precharge starts at the timing indicated by

### Write with Auto Precharge to Write Command Interval (Different bank)

2. Same bank: The consecutive write command (the same bank) is illegal.

#### Read with auto precharge to Write command interval (concurrent auto-precharge)

Different bank: When some banks are in the active state, the second write command (another bank) is executed. However, DQMU and DQML must be set High so that the output buffer becomes High-Z before data input. The internal auto-precharge of one bank starts at the clock of the second command.

Note: Internal auto-precharge starts at the timing indicated by " ... ".

#### Read with Auto Precharge to Write Command Interval (Different bank)

2. Same bank: The consecutive write command from read with auto precharge (the same bank) is illegal. It is necessary to separate the two commands with a bank active command.

#### Write with auto precharge to Read command interval (concurrent auto-precharge)

1. Different bank: When some banks are in the active state, the second read command (another bank) is executed. However, in case of a burst write, data will continue to be written until one clock before the read command is executed. The internal auto-precharge of one bank starts at the next clock of the second command.

Note: Internal auto-precharge starts at the timing indicated by " lacksquare

#### Write with Auto Precharge to Read Command Interval (Different bank)

2. Same bank: The consecutive read command from write with auto precharge (the same bank) is illegal. It is necessary to separate the two commands with a bank active command.

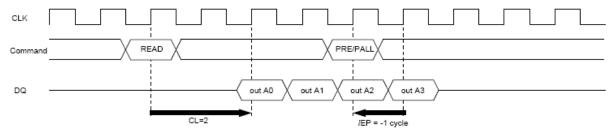

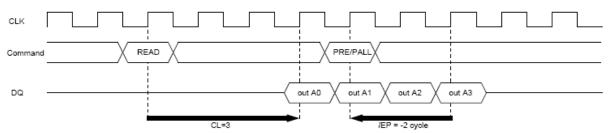

#### Read command to Precharge command interval (same bank)

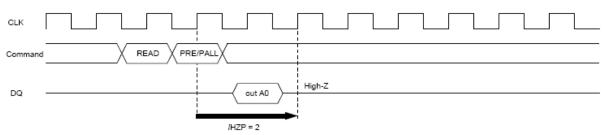

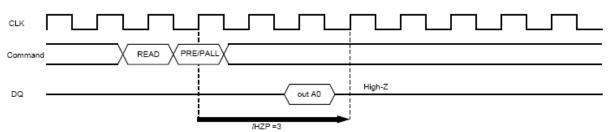

When the precharge command is executed for the same bank as the read command that preceded it, the minimum interval between the two commands is one clock. However, since the output buffer then becomes High-Z after the clocks defined by *l*HZP, there is a case of interruption to burst read data output will be interrupted, if the precharge command is input during burst read. To read all data by burst read, the clocks defined by *l*EP must be assured as an interval from the final data output to precharge command execution.

READ to PRECHARGE Command Interval (same bank): To output all data (CL = 2, BL = 4)

READ to PRECHARGE Command Interval (same bank): To output all data (CL = 3, BL = 4)

READ to PRECHARGE Command Interval (same bank): To stop output data (CL = 2, BL = 1, 2, 4, 8)

READ to PRECHARGE Command Interval (same bank): To stop output data (CL = 3, BL = 1, 2, 4, 8)

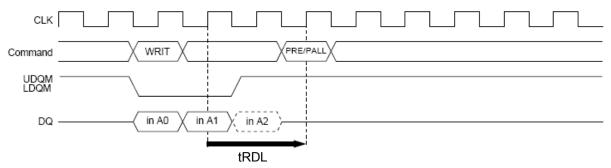

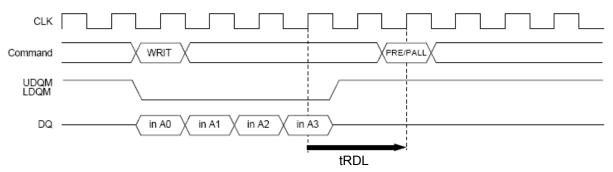

#### Write command to Precharge command interval (same bank)

When the precharge command is executed for the same bank as the write command that preceded it, the minimum interval between the two commands is 1 clock. However, if the burst write operation is unfinished, the input data must be masked by means of DQMU and DQML for assurance of the clock defined by tRDL.

WRITE to PRECHARGE Command Interval (same bank) (BL = 4 (To stop write operation))

WRITE to PRECHARGE Command Interval (same bank) (BL = 4 (To write all data))

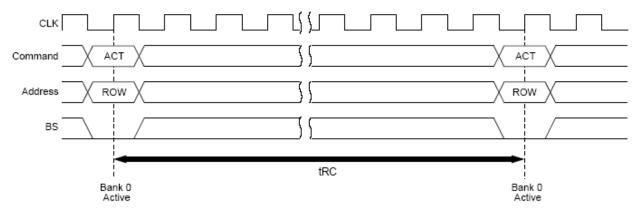

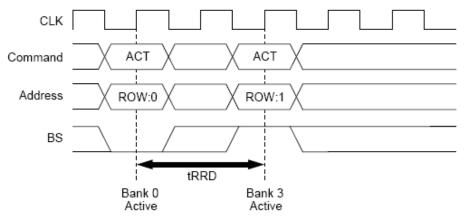

#### Bank active command interval

- 1. Same bank: The interval between the two bank active commands must be no less than tRC.

- 2. In the case of different bank active commands: The interval between the two bank active commands must be no less than tRRD.

Bank Active to Bank Active for Same Bank

Bank Active to Bank Active for Different Bank

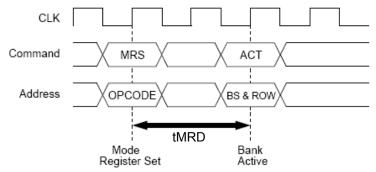

#### Mode register set to Bank active command interval

The interval between setting the mode register and executing a bank active command must be no less than tMRD.

Mode register set to Bank active command interval

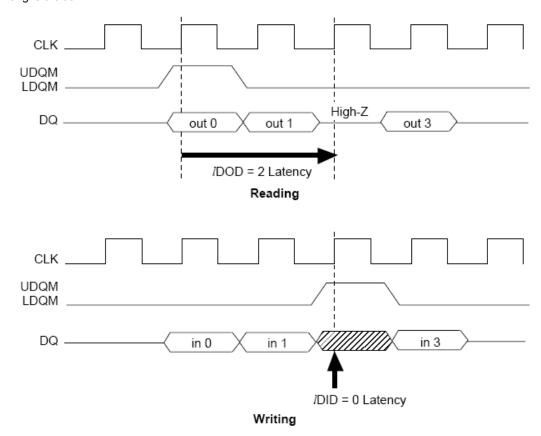

#### **DQM Control**

The DQMU and DQML mask the upper and lower bytes of the DQ data, respectively. The timing of DQMU and DQML is different during reading and writing.

#### Reading

When data is read, the output buffer can be controlled by DQMU and DQML. By setting DQMU and DQML to Low, the output buffer becomes Low-Z, enabling data output. By setting DQMU and DQML to High, the output buffer becomes High-Z, and the corresponding data is not output. However, internal reading operations continue. The latency of DQMU and DQML during reading is 2 clocks.

#### Writing

Input data can be masked by DQMU and DQML. By setting DQM to Low, data can be written. In addition, when DQMU and DQML are set to High, the corresponding data is not written, and the previous data is held. The latency of DQMU and DQML during writing is 0 clock.

## A3V56S30FTP A3V56S40FTP

256M Single Data Rate Synchronous DRAM

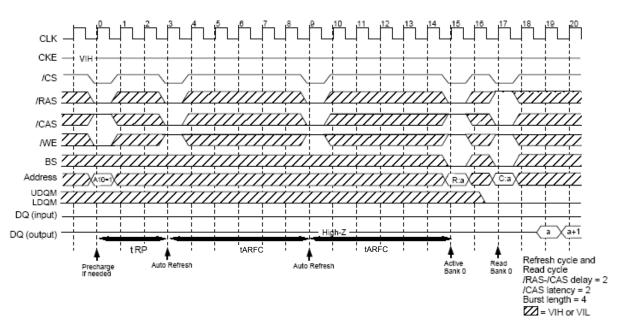

#### Refresh

#### Auto-refresh

All the banks must be precharged before executing an auto-refresh command. Since the auto-refresh command updates the internal counter every time it is executed and determines the banks and the ROW addresses to be refreshed, external address specification is not required. The refresh cycles are required to refresh all the ROW addresses within tREF (max.). The output buffer becomes High-Z after auto-refresh start. In addition, since a precharge has been completed by an internal operation after the auto-refresh, an additional precharge operation by the precharge command is not required.

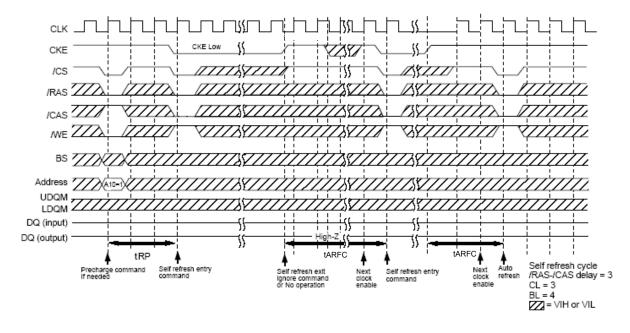

#### Self-refresh

After executing a self-refresh command, the self-refresh operation continues while CKE is held Low. During self-refresh operation, all ROW addresses are refreshed by the internal refresh timer. A self-refresh is terminated by a self-refresh exit command. Before and after self-refresh mode, execute auto-refresh to all refresh addresses in or within tREF(max.) period on the condition 1 and 2 below.

- 1. Enter self-refresh mode within time as below\* after either burst refresh or distributed refresh at equal interval to all refresh addresses are completed.

- Start burst refresh or distributed refresh at equal interval to all refresh addresses within time as below\* after exiting from self-refresh mode.

Note: tREF(max.) / refresh cycles.

#### Others

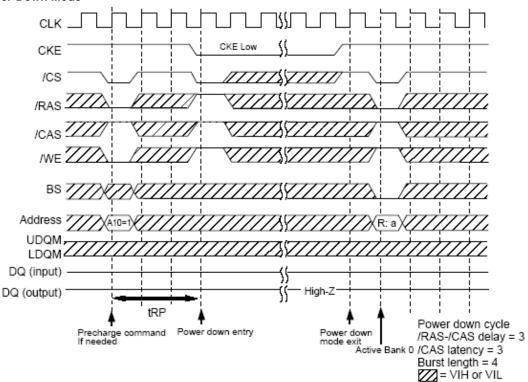

#### Power-down mode

The SDRAM enters power-down mode when CKE goes Low. For cases of all banks in the IDLE state, it is referred to as precharge power-down mode. For cases of any bank in the ACTIVE state, it is referred to as active power-down mode. In power down mode, power consumption is suppressed by deactivating the input buffers excluding CLK and CKE. Power down mode continues while CKE is held Low. In addition, by setting CKE to High, the SDRAM exits from the power down mode, and command input is enabled from the next clock. In this mode, internal refresh is not performed.

#### Clock suspend mode

By driving CKE to Low during a bank active or read/write operation, the SDRAM enters clock suspend mode. During clock suspend mode, external input signals are ignored and the internal state is maintained. When CKE is driven High, the SDRAM terminates clock suspend mode, and command input is enabled from the next clock. For details, refer to the "CKE Truth Table".

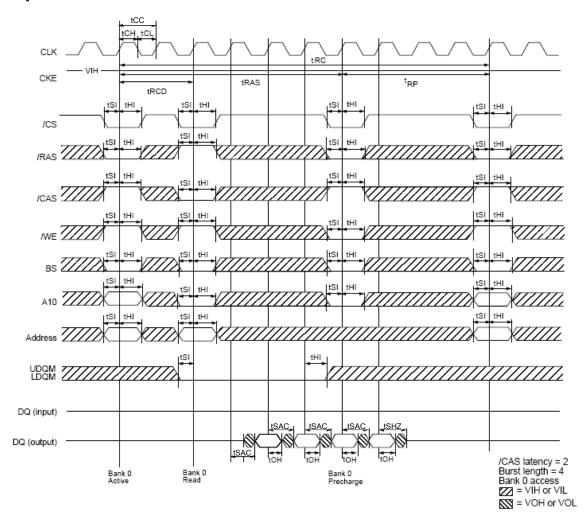

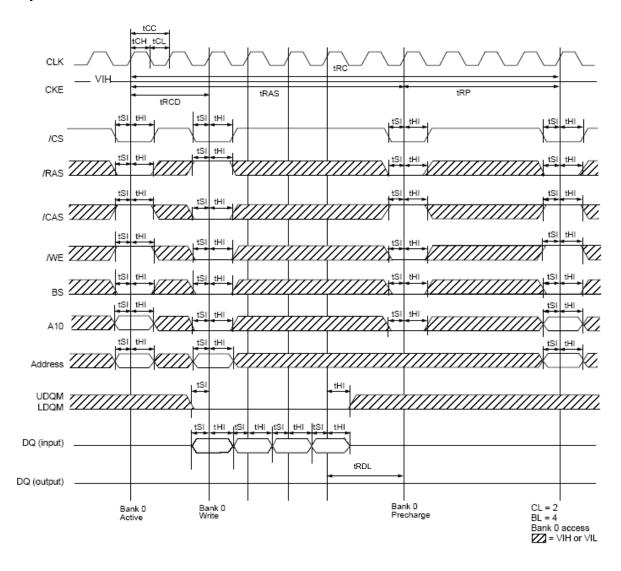

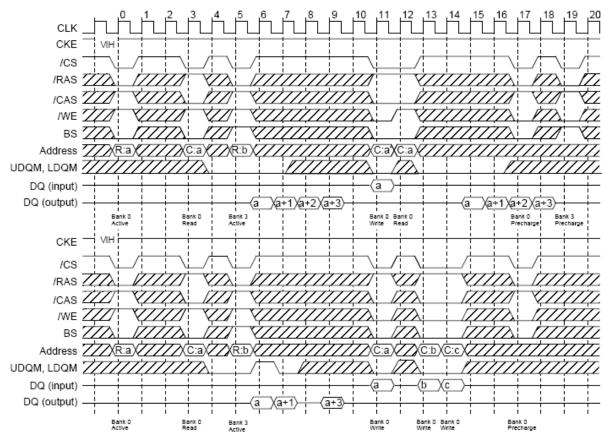

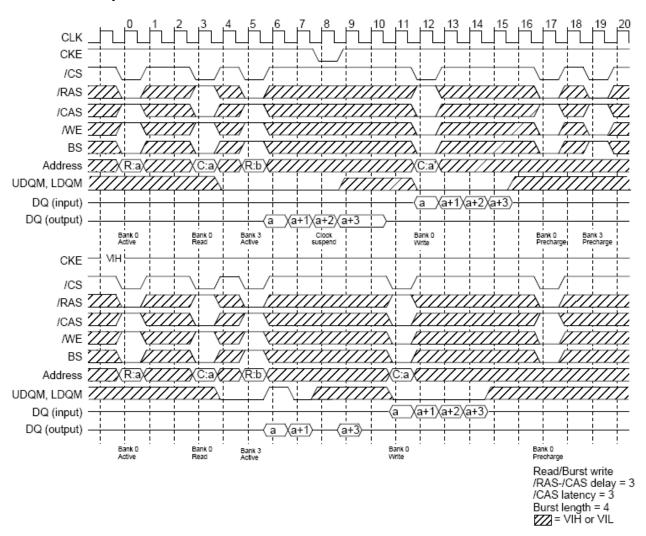

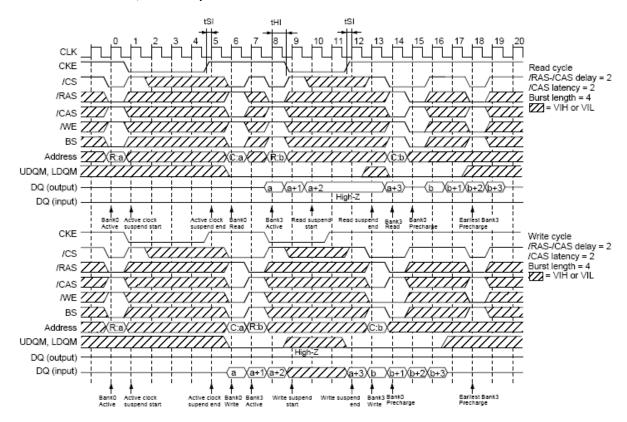

## **Timing Waveforms**

## **Read Cycle**

## **Write Cycle**

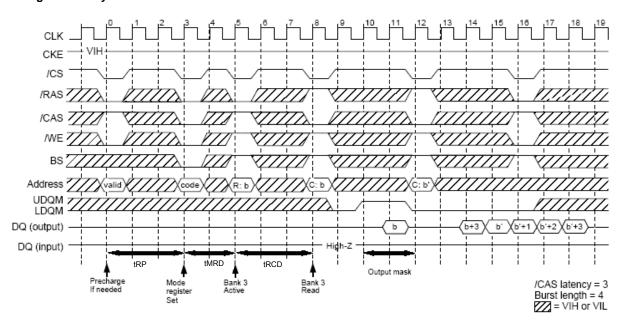

## 256M Single Data Rate Synchronous DRAM

#### **Mode Register Set Cycle**

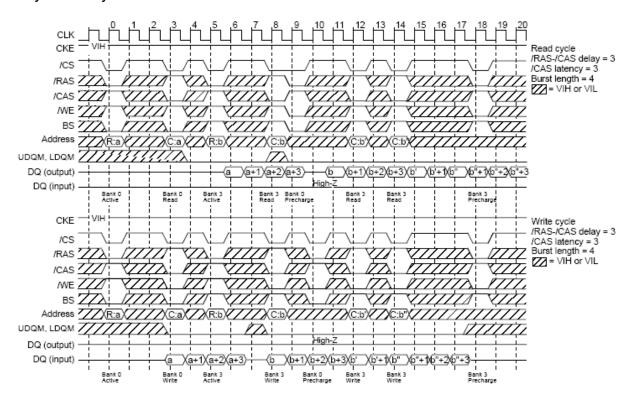

#### Read Cycle/Write Cycle

#### **Read/Single Write Cycle**

Read/Single write

/RAS-/CAS delay = 3

/CAS latency = 3

Burst length = 4

ZZ = VIH or VIL

#### **Read/Burst Write Cycle**

#### **Auto Refresh Cycle**

### Self Refresh Cycle

#### Active Power-Down Mode, Clock Suspend Mode

#### **Precharge Power-Down Mode**

#### **Initialization Sequence**

## Important Notice:

Zentel DRAM products are not intended for medical implementation, airplane and transportation instrument, safety equipments, or any other applications for life support or where Zentel products failure could result in life loss, personal injury, or environment damage. Zentel customers who purchase Zentel products for use in such applications do so in their own risk and fully agree Zentel accepts no liability for any damage from this improper use.