# ACT15530 **CMOS Manchester Encoder / Decoder**

#### **Features**

- MIL-STD-1553 Compatible

- 1.25 Megabit/sec Maximum Data Rate

- Sync Identification and Lock-in

- Clock Recovery

- Manchester II Encode / Decode

- Separate Encoder and Decoder Sections

- Low Operating Power

- Military Temperature Range -55°C to +125°C

- Monolithic Single Chip Construction

www.aeroflex.com Valid Word 1 24 VDD Encoder Shift Clock 2 23 Encoder Clock Take Data 3 22 Send Clock In Serial Data Out 4 21 Send Data

CIRCUIT TECHNOLOGY

Decoder Clock 5 20 Sync Select Bipolar Zero In 6 19 Encoder Enable Bipolar One In 7 18 Serial Data In Unipolar Data In 8 17 Bipolar One Out Decoder Shift Clock 9 16 Output Inhibit Command/Data Sync 10 15 Bipolar Zero Out

14 **6** Out 13 Master Reset VSS 12

Decoder Reset 11

Figure 1: Pin Assignments (24-Pin DIP/Flat Package - See Figure 18 for LCC Pkg)

- Available in Commercial and Industrial Temperature Ranges

- Several Package and Quality Options (Consult Factory for Details)

- Direct Replacement for the Obsolete Harris HD15530-9/-2/8 and GEC Plessey Marconi MA15530 / MAS15530 parts

## **General Description**

The ACT15530 is a high performance CMOS integrated circuit used to implement MIL-STD-1553 and similar Manchester II encoded, time division multiplexed, serial data protocols. The device is divided into two independent sections, encoder and decoder, with a common master reset. The function of the encoder section is to produce the sync pulse and parity bit, and encode the data bits. The decoder section recognizes the sync pulse, decodes the data bits and checks for parity.

The ACT15530 is fully guaranteed to support the 1 MHz data rate of MIL-STD-1553 over the full temperature and supply voltage ranges. The device interfaces with CMOS, TTL or N-Channel support circuitry and operates from a standard 5 volt supply. The circuit can also be used in many party line digital data communications applications where high reliability command and control signals are required. Using Aeroflex transceivers products (4400 Series) the Bit Error Rates (BER) and Word Error Rates (WER) of MIL-STD-1553 can be achieved (Refer to MIL-STD-1553 Multiplex Applications Handbook "MIL-HDBK-1553").

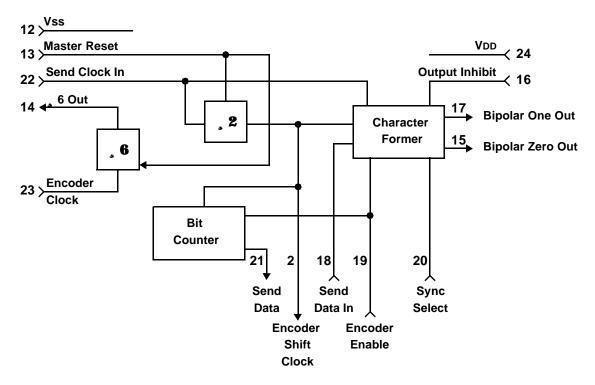

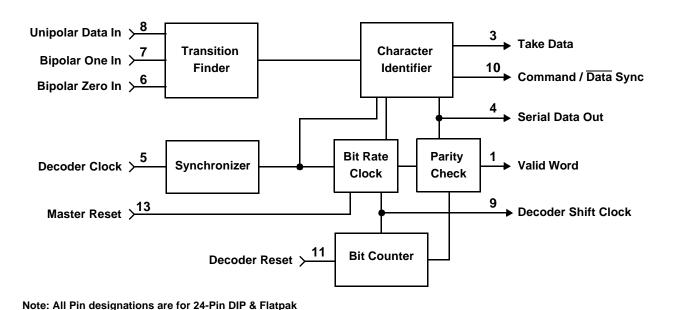

Note: All Pin designations are for 24-Pin DIP & Flatpak

Figure 2: Encoder Block Diagram

Figure 3: Decoder Block Diagram

# **Pin Designations**

| Pin | Input | Output   | Enc      | Dec      | Function            | Comment                                                                                                                                                                                                                                                            |

|-----|-------|----------|----------|----------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   |       | ✓        |          | 1        | Valid word          | A 'high' signals the receipt of a valid word                                                                                                                                                                                                                       |

| 2   |       | 1        | 1        |          | Encoder Shift Clock | Shifts data into the encoder on a 'low' to 'high' transition                                                                                                                                                                                                       |

| 3   |       | 1        |          | <b>\</b> | Take Data           | 'high' during data reception after the sync pulse is identified                                                                                                                                                                                                    |

| 4   |       | ✓        |          | 1        | Serial Data Out     | NRZ output of received data                                                                                                                                                                                                                                        |

| 5   | 1     |          |          | <b>\</b> | Decoder clock       | Clock for the transition finder and synchronizer which generates the clock for the rest of the decoder                                                                                                                                                             |

| 6   | 1     |          |          | ✓        | Bipolar Zero In     | Should be 'high' when the bus is in a negative state.<br>Must be tied 'high' when the unipolar input is used                                                                                                                                                       |

| 7   | 1     |          |          | ✓        | Bipolar One In      | Should be 'high' when the bus is in a positive state.<br>Must be tied 'low' when the unipolar input is used                                                                                                                                                        |

| 8   | 1     |          |          | ✓        | Unipolar Data In    | Input for unipolar data to the transition finder. Must be tied 'low' when not used                                                                                                                                                                                 |

| 9   |       | <b>√</b> |          | ✓        | Decoder Shift Clock | Provides the DECODER CLOCK divided by 12, synchronized by the recovered serial data                                                                                                                                                                                |

| 10  |       | <b>√</b> |          | <b>√</b> | Command/Data Sync   | This output indicates the type of synchronizing character received as follows: If a data synchronizing character was received, this pin is low while the data is decoded. If a command synchronizing character was received, this pin is high during data decoding |

| 11  | 1     |          |          | ✓        | Decoder Reset       | A 'high' during a DECODER SHIFT CLOCK rising edge resets the bit counter                                                                                                                                                                                           |

| 12  | _     | ı        | 1        | 1        | Vss                 | Ground                                                                                                                                                                                                                                                             |

| 13  | ✓     |          | <b>\</b> | <b>\</b> | Master Reset        | A 'high" clears the counters in both sections                                                                                                                                                                                                                      |

| 14  |       | <b>√</b> | <b>\</b> |          | • 6 Out             | Provides the ENCODER CLOCK divided by 6                                                                                                                                                                                                                            |

| 15  |       | <b>√</b> | >        |          | Bipolar Zero Out    | Provides an active 'low' output to the zero or negative sense of a bipolar line driver                                                                                                                                                                             |

| 16  | 1     |          | 1        |          | Output Inhibit      | A 'low' inhibits the BIPOLAR ZERO OUT and BIPOLAR ONE OUT by forcing them to inactive, 'high', states                                                                                                                                                              |

| 17  |       | ✓        | 1        |          | Bipolar One Out     | Provides an active 'low' output to the one or positive sense of a bipolar line driver                                                                                                                                                                              |

| 18  | 1     |          | <b>/</b> |          | Serial Data In      | Receives serial data at the rate of the ENCODER SHIFT CLOCK                                                                                                                                                                                                        |

| 19  | 1     |          | <b>\</b> |          | Encoder Enable      | A 'high' starts the encode cycle provided that the previous cycle is complete                                                                                                                                                                                      |

| 20  | 1     |          | <b>\</b> |          | Sync Select         | A 'high' selects the command sync and a 'low' selects the data sync                                                                                                                                                                                                |

| 21  |       | 1        | <b>\</b> |          | Send Data           | Provides an active 'high' to enable the external serial data source                                                                                                                                                                                                |

| 22  | ✓     |          | 1        |          | Send Clock In       | Clock input at 2 times the data rate                                                                                                                                                                                                                               |

| 23  | 1     |          | 1        |          | Encoder Clock       | Input to the divide by 6 circuit                                                                                                                                                                                                                                   |

| 24  | _     | _        | 1        | 1        | VDD                 | Positive Supply                                                                                                                                                                                                                                                    |

Figure 4: Pin Designations (24-Pin Dip/FlatPack)

# **DC Characteristics and Ratings**

## **Absolute Maximum Ratings**

| Parameter             | Min       | Max        | Units |

|-----------------------|-----------|------------|-------|

| VDD                   | 3         | 7          | V     |

| Input Voltage         | Vss - 0.3 | VDD + 0.3V | V     |

| Operating Temperature | -55       | +125       | °C    |

| Storage Temperature   | -65       | +150       | °C    |

Figure 5: Absolute Maximum Ratings

#### **DC Characteristics**

| Sym               | Parameter                       | Min        | Тур | Max        | Units | Test<br>Conditions                 |

|-------------------|---------------------------------|------------|-----|------------|-------|------------------------------------|

| $V_{IH}$          | Logic "1" Input Voltage         | 70%VDD     | -   | -          | V     |                                    |

| $\vee_{IL}$       | Logic "0" Input Voltage         | -          | -   | 30%VDD     | V     |                                    |

| V <sub>IHC</sub>  | Logic "1" Input Voltage (Clock) | VDD - 0.5V | -   | -          | V     |                                    |

| V <sub>ILC</sub>  | Logic "0" Input Voltage (Clock) | -          | -   | Vss + 0.5V | V     |                                    |

| I <sub>IL</sub>   | Input Leakage Current           | -1.0       |     | +1.0       | μΑ    | 0V ≤ VIN ≤ VDD                     |

| V <sub>OH</sub>   | Logic "1" Output Voltage        | 2.4        | -   | -          | V     | Iон = -3 mA                        |

| V <sub>OL</sub>   | Logic "0" Output Voltage        | -          | -   | 0.4        | V     | IOL = 1.8 mA                       |

| I <sub>DDSB</sub> | Standby Supply Current          | -          | 0.5 | 2.0        | mA    | Output Open<br>VIN = VDD =<br>5.5V |

| I <sub>DDOP</sub> | Operating Supply Current        | -          | 8.0 | 10.0       | mA    | VDD = 5.5V,<br>f = 1MHz            |

| C <sub>IN</sub>   | Input Capacitance               | -          | 5.0 | 7.0        | pF    |                                    |

| C <sub>out</sub>  | Output Capacitance              | -          | 8.0 | 10.0       | pF    |                                    |

$VDD = 5V \pm 10\%$ , over full operating temperature range.

Figure 6: DC Characteristics

## **AC Characteristics**

| Sym  | Sym Parameter            |     | Limits |       |  |

|------|--------------------------|-----|--------|-------|--|

| Sym  | Parameter                | Min | Max    | Units |  |

| fEC  | Encoder clock frequency  | 0   | 15     | MHz   |  |

| fESC | Send clock frequency     | 0   | 2.5    | MHz   |  |

| tECR | Encoder clock rise time  | -   | 8      | ns    |  |

| tECF | Encoder clock fall time  | -   | 8      | ns    |  |

| fED  | Data rate                | 0   | 1.25   | MHz   |  |

| tMR  | Master reset pulse width | 150 | -      | ns    |  |

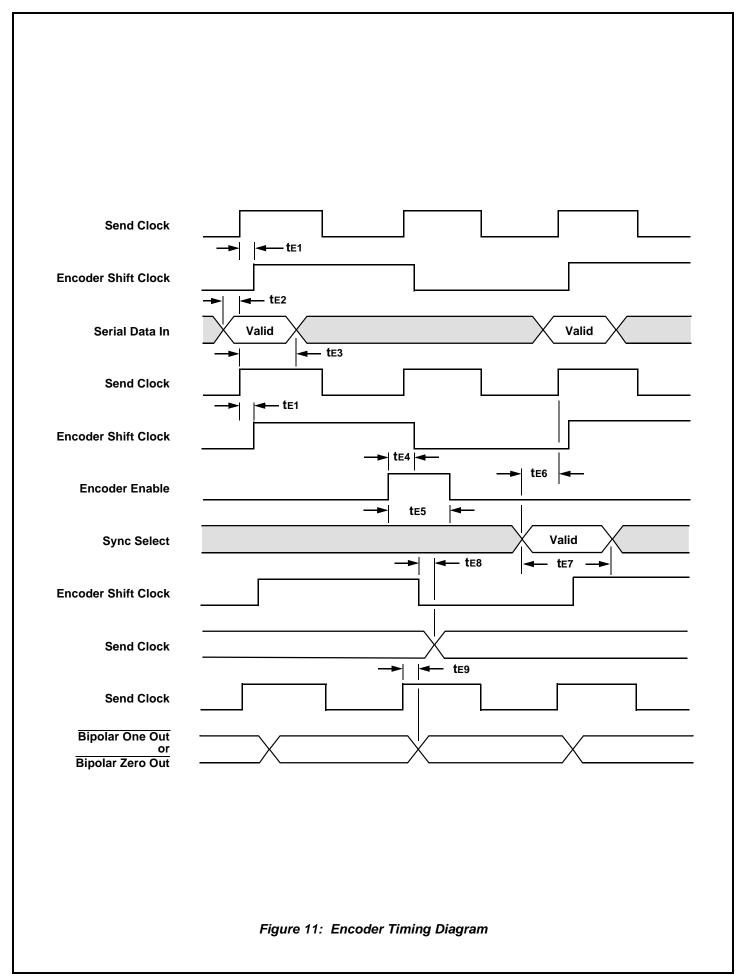

| tE1  | Shift clock delay        | -   | 125    | ns    |  |

| tE2  | Serial data setup time   | 75  | -      | ns    |  |

| tE3  | Serial data hold time    | 75  | -      | ns    |  |

| tE4  | Enable setup time        | 90  | -      | ns    |  |

| tE5  | Enable pulse width       | 100 | -      | ns    |  |

| tE6  | Sync setup time          | 55  | -      | ns    |  |

| tE7  | Sync pulse width         | 150 | -      | ns    |  |

| tE8  | Send data delay          | 0   | 50     | ns    |  |

| tE9  | Bipolar output delay     | -   | 130    | ns    |  |

Figure 7: Encoder Electrical Characteristics

1.  $VDD = 5V \pm 10\%$ , over full operating temperature range. 2. CL=50pF.

| Cum  | Doromotor                  | Limits   |       |          |       |

|------|----------------------------|----------|-------|----------|-------|

| Sym  | Parameter                  | Min      | Тур   | Max      | Units |

| fDC  | Decoder clock frequency    | 0        | •     | 15       | MHz   |

| tDCR | Decoder clock rise time    | -        | -     | 8        | MHz   |

| tDCF | Decoder clock fall time    | -        | -     | 8        | ns    |

| fDD  | Data rate                  | 0        | -     | 1.25     | MHz   |

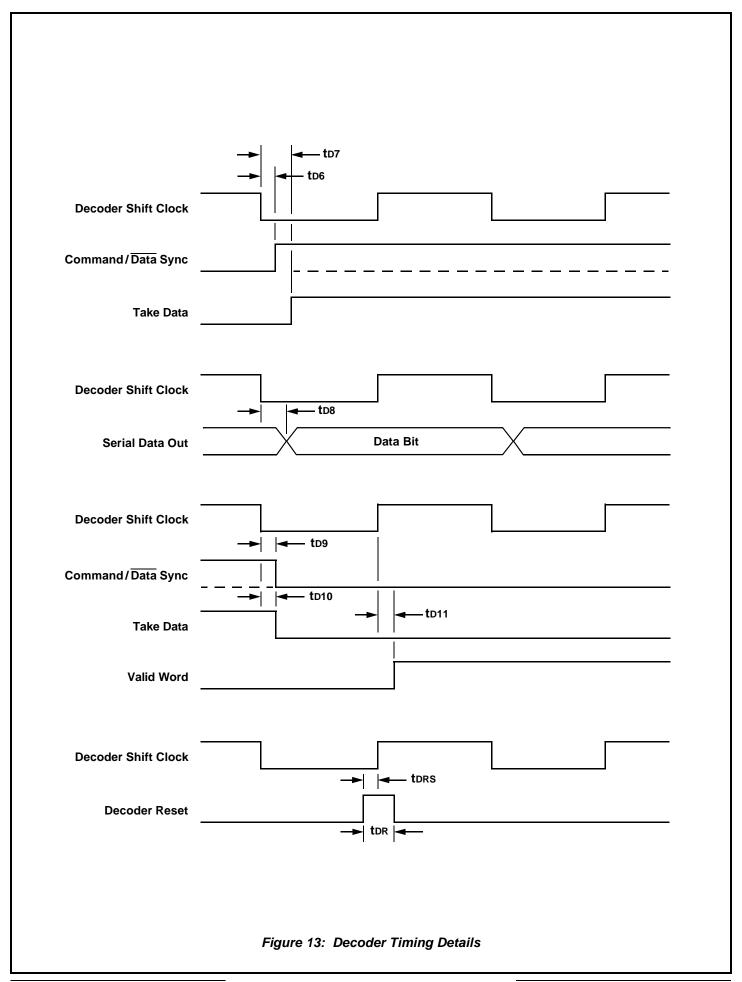

| tDR  | Decoder reset pulse width  | 150      | -     | -        | ns    |

| tDRS | Decoder reset setup time   | 75       | -     | -        | ns    |

| tMR  | Master reset pulse width   | 150      | -     | -        | ns    |

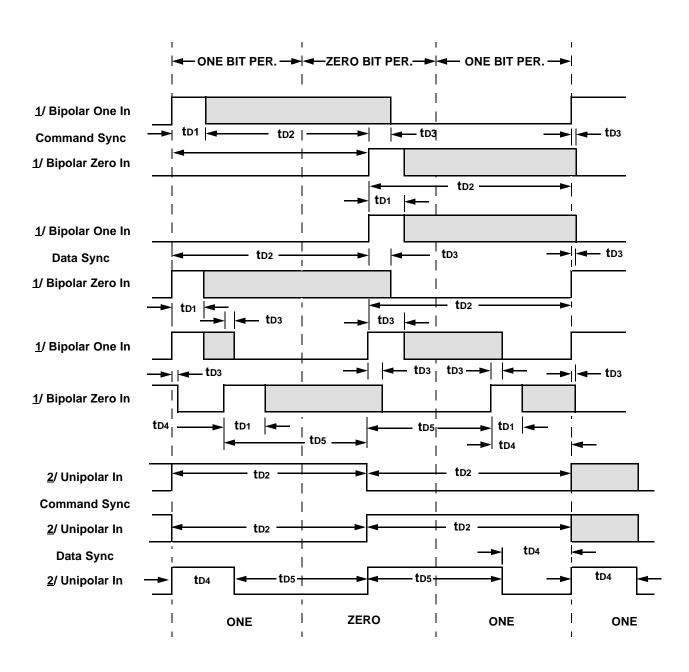

| tD1  | Bipolar data pulse width   | tDC + 10 | -     | -        | ns    |

| tD2  | Sync transition span       | -        | 18tDC | -        | ns    |

| tD3  | One-Zero overlap           | -        | -     | tDC - 10 | ns    |

| tD4  | Short data transition span | -        | 6tDC  | -        | ns    |

| tD5  | Long data transition span  | -        | 12tDC | -        | ns    |

| tD6  | Sync delay (on)            | -20      | -     | 110      | ns    |

| tD7  | Take data delay (on)       | 0        | -     | 110      | ns    |

| tD8  | Serial data out delay      | -        | -     | 80       | ns    |

| tD9  | Sync delay (off)           | 0        | -     | 110      | ns    |

| tD10 | Take data delay (off)      | 0        | -     | 110      | ns    |

| tD11 | Valid word delay           | 0        | -     | 110      | ns    |

Figure 8: Decoder Electrical Characteristics

<sup>1.</sup>  $VDD = 5V \pm 10\%$ , over full operating temperature range. 2. CL=50pF.

<sup>3.</sup> tDC = Decoder clock period = 1/fDC

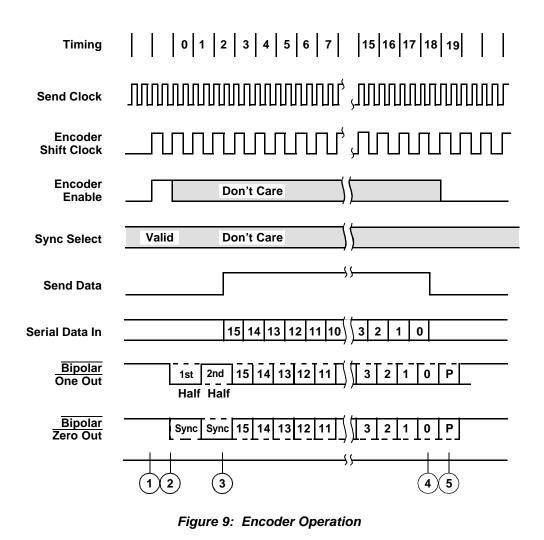

#### **Encoder Operation**

The Encoder requires a single clock with a frequency of twice the desired data rate applied at the SEND CLOCK input. An auxiliary divide by six counter is provided on chip which can be utilised to produce the SEND CLOCK by dividing the DECODER CLOCK.

The Encoder's cycle begins when ENCODER ENABLE is high during a failing edge of ENCODER SHIFT CLOCK ①. This cycle lasts for one word length or twenty ENCODER SHIFT CLOCK periods. At the next low-to-high transition of the ENCODER SHIFT CLOCK, a high at SYNC SELECT input actuates a command sync or a low will produce a data sync for that word ②. When the Encoder is ready to accept data, the SEND DATA output will go high and remain high for sixteen ENCODER SHIFT CLOCK periods 3.

During these sixteen periods the data should be clocked into the SERIAL DATA input with every low-high transition of the ENCODER SHIFT CLOCK 3 - 4. After the sync and the Manchester II coded data are chip transmitted through the  $\overline{\text{BIPOLAR}}$  ONE and  $\overline{\text{BIPOLAR}}$ ZERO outputs, the Encoder adds on an additional bit which is the parity for that word **⑤**. At any time a low in OUTPUT INHIBIT input will force both bipolar outputs to a high state but will not affect the Encoder in any other way. To abort the Encoder transmission a positive pulse must be applied at MASTER RESET. Anytime after or during this pulse, a low to high transition on SEND CLOCK clears the internal counters and initializes the Encoder for a new word.

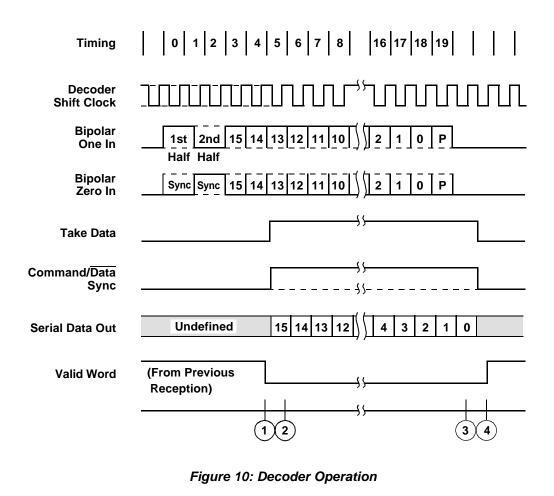

#### **Decoder Operation**

The Decoder requires a single clock with a frequency of 12 times the desired data rate applied at the DECODER CLOCK input. The Manchester II coded data can be presented to the Decoder in one of two ways. The BIPOLAR ONE and BIPOLAR ZERO inputs will accept data from a comparator sensed transformer coupled bus as specified in MIL-STD-1553. The UNIPOLAR DATA input can only accept non-inverted Manchester II coded data (e.g.from BIPOLAR ZERO OUT of an Encoder).

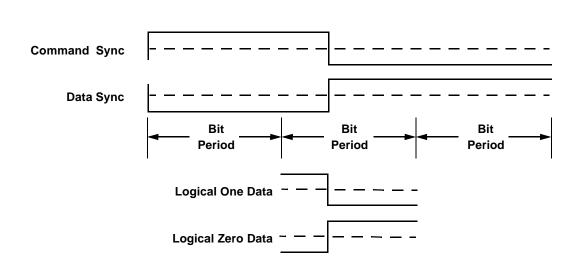

The Decoder is free running and continuously monitors its data input lines for a valid sync character and two valid Manchester data bits to start an output cycle.. When a valid sync is recognized ①, the type of sync is indicated on COMMAND/DATA SYNC output. if the sync character was a command sync, this output will go high ② and remain high for sixteen DECODER SHIFT CLOCK periods ③, otherwise it will remain low. The TAKE DATA

output will go high and remain high ② - ③ while the Decoder is transmitting the decoded data through SERIAL DATA OUT. The decoded data available at SERIAL DATA OUT is in a NRZ format. The DECODER SHIFT CLOCK is provided so that the decoded bits can get shifted into an external register on every low-to-high transition of this clock ② - ③.

After all sixteen decoded bits have been transmitted ③ the data is checked for odd parity. A high on VALID WORD output ④ indicates a successful reception of a word without any Manchester or parity errors. At this time the Decoder is looking for a new sync character to start another output sequence.

At any time in the above sequence, a high input on DECODER RESET during a low-to-high transition of DECODER SHIFT CLOCK will abort transmission and initialize the Decoder to start looking for a new sync character.

Notes: 1. Unipolar In = 02. Bipolar One In = 0

Bipolar Zero In = 1

Figure 12: Decoder Timing Diagram

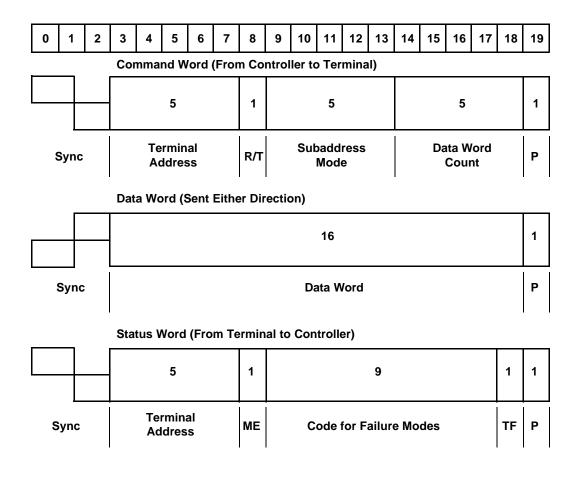

Figure 14: Character Formats

Figure 15: Word Formats

| Valid Word 1          | $\sim$ | 24 VDD              |

|-----------------------|--------|---------------------|

| Encoder Shift Clock 2 |        | 23 Encoder Clock    |

| Take Data 3           |        | 22 Send Clock In    |

| Serial Data Out 4     |        | 21 Send Data        |

| Decoder Clock 5       |        | 20 Sync Select      |

| Bipolar Zero In 6     |        | 19 Encoder Enable   |

| Bipolar One In 7      |        | 18 Serial Data In   |

| Unipolar Data In 8    |        | 17 Bipolar One Out  |

| Decoder Shift Clock 9 |        | 16 Output Inhibit   |

| Command/Data Sync 10  |        | 15 Bipolar Zero Out |

| Decoder Reset 11      |        | 14                  |

| Vss 12                |        | 13 Master Reset     |

| Ref.           | Min.                      | Nom.              | Max.          |  |  |  |

|----------------|---------------------------|-------------------|---------------|--|--|--|

| Α              | -                         | -                 | 5.60 (0.220)  |  |  |  |

| A <sub>1</sub> | 0.38 (0.015)              | -                 | 1.53 (0.060)  |  |  |  |

| b              | 0.35 (0.014)              | -                 | 0.59 (0.023)  |  |  |  |

| С              | 0.20 (0.008)              | -                 | 0.36 (0.014)  |  |  |  |

| D              | -                         | -                 | 30.79 (1.212) |  |  |  |

| е              | -                         | 2.54 (0.100) Typ  | -             |  |  |  |

| e <sub>1</sub> | -                         | 15.24 (0.600) Typ | -             |  |  |  |

| Н              | 4.71 (0.185)              | -                 | 5.38 (0.212)  |  |  |  |

| $M_E$          | -                         | -                 | 15.90 (0.626) |  |  |  |

| W              | -                         | -                 | 1.53 (0.060)  |  |  |  |

| Dime           | Dimensions in mm (inches) |                   |               |  |  |  |

$\mathsf{M}_\mathsf{E}$

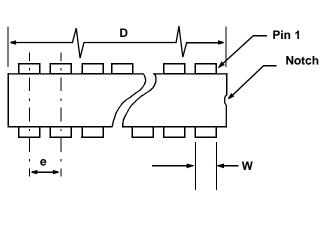

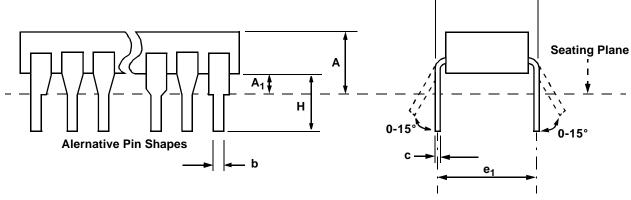

Figure 16: 24-Lead Ceramic DIL (Solder Seal) - Package Style C

## **TOP VIEW** ENCODER SHIFT CLK E TAKE DATA E ROODER SHIFT CI VALID WORD S Vcc E ROODER CLK S SEND CLK IN DECODER CLK SEND DATA 24 NC 23 NC 22 **BIPOLAR ZERO IN** SYNC SELECT 21 **ENCODER ENABLE** BIPOLAR ONE IN 20 SERIAL DATA IN UNIPOLAR DATA IN 10 BIPOLAR ONE OUT DECODER SHIFT CLOCK DECODER RESET GROUND MASTER RESET BIPOLAR ZERO OUT OUTPUT INHIBIT **BOTTOM VIEW** .<u>003</u> .015 .<u>075</u> .095 .<u>006</u> .022 .<u>442</u> .458 .022 .028 .015 MIN .<u>045</u> .055 .<u>050</u> BSC .<u>442</u> .458 .090 MAX .<u>074</u> .088

Figure 18: 28-Leadless Ceramic Chip Carrier - Package Style L

### **Ordering Information**

| Model Number | Part Number                  |  |

|--------------|------------------------------|--|

| ACT15530XX   | See Below or Contact Factory |  |

#### Part Number Breakdown

ACT15530 X X Rel Level

**C** Ceramic DIL (Figure 16)

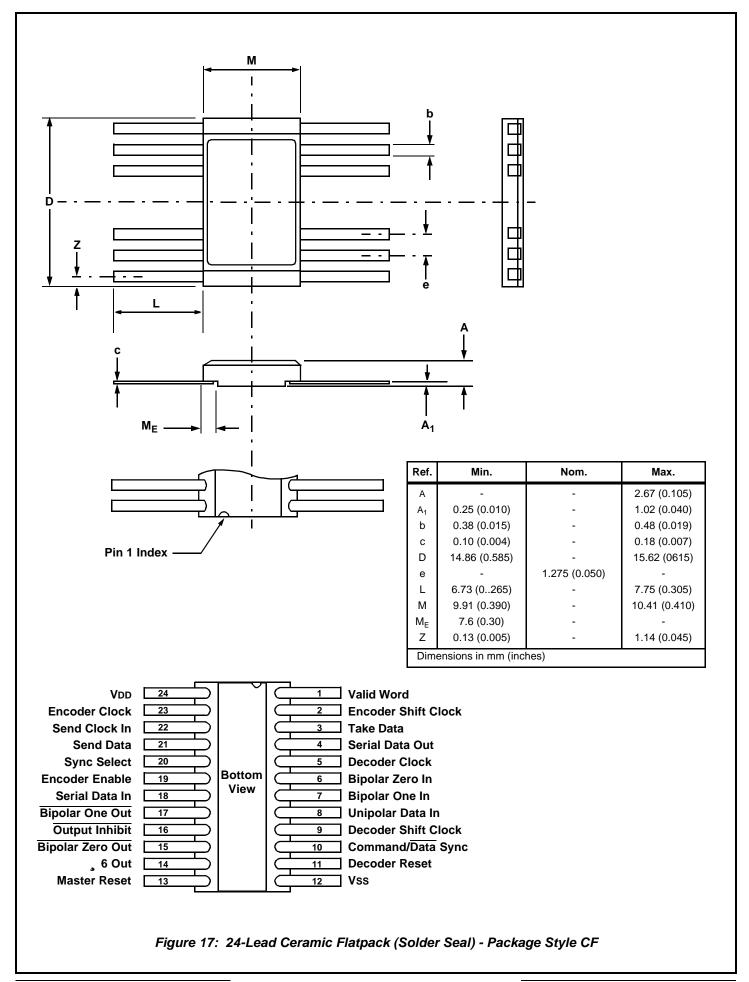

**CF** Flatpack (Figure 17)

L LCC (Figure 18)

N Naked Die \*

Package Type =

P Plastic DIP \*

B Class B Operating Temperature (Figure 5) -55°C to +125°C

C Commercial (0°C to+70°C)

I Industrial (-40°C to +85°C)

S Space \*

\* Contact Factory for Details

**Aeroflex Circuit Technology** 35 South Service Road **Plainview New York 11803**

Specifications subject to change without notice.

FAX:

Telephone: (516) 694-6700 (516) 694-6715

Toll Free Inquiries: 1-(800)THE-1553