## LC<sup>2</sup>MOS GSM Baseband I/O Port

## AD7001

FEATURES

Single +5 V Supply

Single Channel 8-Bit A/D Converter

2.16 MHz Sampling Rate

Receive Difference Amplifier

Programmable Gain Amplifier

Two 10-Bit D/A Converters

2 MHz Throughput Rate

Simultaneous Update Mode

4th Order Antialias Filters

Single Serial Auxiliary 8-Bit D/A Converter

Fast Interface Port

Power Down Mode(s)

On-Chip Voltage Reference

44-Pin PQFP

APPLICATIONS

Digital Cellular Telephony

Private Mobile Telephony

Satellite Baseband Digitization

Radar Signal Processing

Signal Generation and Acquisition

#### GENERAL DESCRIPTION

The AD7001 is a complete low power, LC<sup>2</sup>MOS, input/output port with single +5 V power supply. The part is designed to perform the conversion of I and Q signals in the transmit and receive data paths of Pan-European Digital Cellular Telephone (GSM) systems. However, the device can be used in any application requiring fast and accurate signal conversion in the sub-600 kHz band.

Besides providing two high accuracy 10-bit digital-to-analog converters in the transmit path and a single fast analog-to-digital converter in the receive path, the part also provides antialiasing filters and signal conditioning functions.

A single serial 8-bit DAC is included for such functions as AFC, AGC or carrier signal shaping in the IF/RF portion of the system.

All logic necessary for control of this device is contained on board. A fast data bus allows easy interface with all commonly available microprocessors.

As it is a necessity for all GSM mobile systems to use the lowest possible power, the device has power down options for both the transmit path and the receive path which are independent of each other. The AD7001 is housed in a space efficient 44-pin PQFP (Plastic Quad Flatpack).

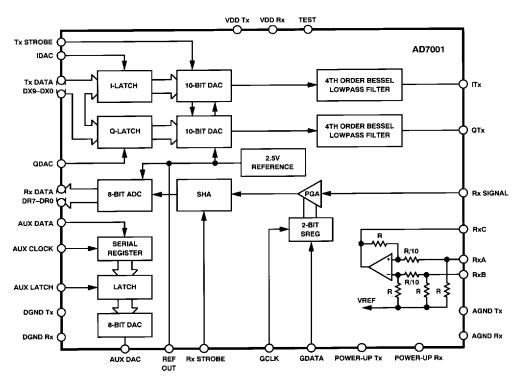

## FUNCTIONAL BLOCK DIAGRAM

## REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

#

| Parameter                            | AD7001A                 | Units                                  | Test Conditions/Comments                                             |

|--------------------------------------|-------------------------|----------------------------------------|----------------------------------------------------------------------|

| ADC SPECIFICATIONS                   |                         |                                        | $POWER-UP Rx = V_{DD}$                                               |

| Resolution                           | 8                       | Bits                                   |                                                                      |

| Signal Input Range                   | $V_{REF} \pm V_{REF}/2$ | Volts                                  | PGA = 1                                                              |

| oighin input rungo                   | $V_{REF} \pm V_{REF}/4$ | Volts                                  | PGA = 2                                                              |

|                                      | $V_{REF} \pm V_{REF}/8$ | Volts                                  | $PGA = 4$ ; All Biased on $V_{REF}$                                  |

| Sampling Rate                        | 2.17                    | MSPS                                   | 7 GIL THE BLUSTE OF TREE                                             |

| DC Accuracy                          | 2.17                    | 1,101 0                                |                                                                      |

| Integral Nonlinearity                | ±1.5                    | LSB max                                | PGA = 1, 2  or  4                                                    |

| Differential Nonlinearity            | ±1.5                    | LSB max                                | PGA = 1, 2 or 4                                                      |

| Offset Error                         |                         | Lob max                                | 1 311 1, 2 31 4                                                      |

|                                      | ±3                      | LSB max                                | PGA = 1                                                              |

| $T_{MIN}$ to $T_{MAX}$               | ±5                      | LSB max                                | PGA = 2                                                              |

| $T_{MIN}$ to $T_{MAX}$               | ±10                     | LSB max                                | PGA = 4                                                              |

| T <sub>MIN</sub> to T <sub>MAX</sub> | <u>-10</u>              | LSD IIIax                              | Positive and Negative                                                |

| Full-Scale Error                     |                         | I CD may                               | PGA = 1                                                              |

| $T_{MIN}$ to $T_{MAX}$               | ±6                      | LSB max                                |                                                                      |

| $T_{MIN}$ to $T_{MAX}$               | ±8                      | LSB max                                | PGA = 2                                                              |

| $T_{MIN}$ to $T_{MAX}$               | ±10                     | LSB max                                | PGA = 4                                                              |

| Input Resistance (DC)                | 5                       | kΩ min                                 |                                                                      |

| Input Capacitance                    | 20                      | pF typ                                 | 77                                                                   |

| Dynamic Specifications               |                         |                                        | $V_{IN} = 500 \text{ kHz Full-Scale Sine Wave,}$                     |

| Signal-to-Noise Ratio                | 40                      | dB min                                 | $f_{SAMPLE} = 2.16 \text{ MHz}; PGA = 1, 2 \text{ or } 4$            |

| Peak Spurious Noise                  | -40                     | dB max                                 | PGA = 1, 2  or  4                                                    |

| Total Harmonic Distortion            | -40                     | dB max                                 | PGA = 1, 2  or  4                                                    |

| Gain Accuracy                        | ±0.5                    | dB max                                 | PGA = 1                                                              |

|                                      | $\pm 0.75$              | dB max                                 | PGA = 2                                                              |

|                                      | ±1.5                    | dB max                                 | PGA = 4                                                              |

| Coding                               | Binary                  |                                        |                                                                      |

| Power-Down Option                    | Yes                     |                                        | POWER-UP Rx = 0 V                                                    |

| DIFFERENCE AMPLIFIER SPECIFICATIONS  |                         |                                        | $POWER-UP Rx = V_{DD}$                                               |

| Differential Gain                    | 19.5                    | dB min                                 | $V_{IN} = 474 \text{ kHz} \pm 80 \text{ kHz}$ ; Biased on $V_{REF}$  |

| Direction duit                       | 21.5                    | dB max                                 | TIN , KEI                                                            |

| Input Common-Mode Rejection Ratio    | 40                      | dB min                                 | RxA = RxB = 0.4  V p-p  @ 500  kHz                                   |

| Distortion                           | - <del>4</del> 0        | dB max                                 | $V_{OUT} = 1 \text{ V p-p } @ 500 \text{ kHz}$ ; Biased on $V_{REF}$ |

| Input Impedance                      | 10                      | di max                                 | TOUT 1 V P P 68 300 Relay Blasser on V REF                           |

| RxA to REF OUT                       | 20/60                   | kΩ min/max                             | 40 kΩ Typical                                                        |

|                                      | 10/40                   | kΩ min/max                             | 25 kΩ Typical                                                        |

| RxB to REF OUT                       |                         | kΩ min/max                             | 6.5 kΩ Typical                                                       |

| RxA to RxB                           | 3/10                    |                                        |                                                                      |

| Output Offset                        | ±20                     | mV max                                 | At RxC When Inputs Are Floating POWER-UP Rx = 0 V                    |

| Power-Down Option                    | Yes                     |                                        |                                                                      |

| SIGNAL DAC SPECIFICATIONS            |                         |                                        | $POWER-UP Rx = V_{DD}$                                               |

| Resolution                           | 10                      | Bits                                   |                                                                      |

| Number of Channels                   | 2                       |                                        |                                                                      |

| Update Rate                          | 2.17                    | MSPS                                   |                                                                      |

| DC Accuracy                          |                         |                                        |                                                                      |

| Integral Nonlinearity                | ±1                      | LSB typ                                |                                                                      |

| Differential Nonlinearity            | ±1                      | LSB typ                                |                                                                      |

| Output Signal Range                  | $V_{REF} \pm V_{REF}/2$ | Volts                                  | Biased on V <sub>REF</sub> ; 10 kΩ/20 pF Load                        |

| Offset Error                         | ±50                     | mV max                                 | 10 0000 0000 Loaded to DAC                                           |

| Dynamic Specifications               |                         |                                        |                                                                      |

| Gain Accuracy                        | ±0.5                    | dB max                                 | Measure at 66.65 kHz                                                 |

| ITx and QTx Gain Matching            | $\pm 0.5$<br>$\pm 0.1$  | dB max                                 | Generating 66.65 kHz Sine Waves                                      |

| Differential Group Delay             | 200                     | ns max                                 | Measured Relative to the Absolute Group Delay                        |

| Differential Group Delay             | 200                     | III III III III III III III III III II | at 10 kHz in the Frequency Band 10 kHz-200 kHz                       |

| ITy and OTy Phase Matchine           | +1                      | ° may                                  |                                                                      |

| ITx and QTx Phase Matching           | ±1                      | ° max                                  | Measured at 66.65 kHz                                                |

| AD7001A           | Units                                                                                                                                                                                 | Test Conditions/Comments                                                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

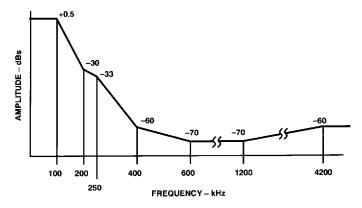

|                   |                                                                                                                                                                                       | Refer to Figure 1                                                              |

| +0.5              | dB min                                                                                                                                                                                |                                                                                |

| -30               | dB min                                                                                                                                                                                |                                                                                |

| -33               | dB min                                                                                                                                                                                |                                                                                |

| -60               | dB min                                                                                                                                                                                |                                                                                |

|                   | dB min                                                                                                                                                                                |                                                                                |

| -70               | dB min                                                                                                                                                                                |                                                                                |

| -60               | dB min                                                                                                                                                                                |                                                                                |

|                   | ° RMS tvp                                                                                                                                                                             |                                                                                |

|                   |                                                                                                                                                                                       |                                                                                |

|                   |                                                                                                                                                                                       |                                                                                |

| -3                | dB tvp                                                                                                                                                                                |                                                                                |

| _                 |                                                                                                                                                                                       |                                                                                |

|                   |                                                                                                                                                                                       |                                                                                |

| 77                | ub typ                                                                                                                                                                                | Producing 66.65 kHz Sine Wave with 2.17 MHz                                    |

| 52                | dR min                                                                                                                                                                                | Updated Rate                                                                   |

|                   | '                                                                                                                                                                                     | o punted Nate                                                                  |

| 1                 | ub typ                                                                                                                                                                                |                                                                                |

| 1 "               |                                                                                                                                                                                       | POWER-UP Tx = 0 V                                                              |

| res               |                                                                                                                                                                                       |                                                                                |

|                   |                                                                                                                                                                                       | $POWER-UP Tx = V_{DD}$                                                         |

| 8                 | Bits                                                                                                                                                                                  |                                                                                |

|                   |                                                                                                                                                                                       |                                                                                |

| ±2                | LSB max                                                                                                                                                                               |                                                                                |

| ±1                | LSB max                                                                                                                                                                               | Guaranteed Monotonic                                                           |

| $1.25 \pm 1$      | LSB max                                                                                                                                                                               |                                                                                |

| ±60               | mV max                                                                                                                                                                                |                                                                                |

| 0 to 2.5          | Volts                                                                                                                                                                                 |                                                                                |

| 2                 | kΩ max                                                                                                                                                                                | $I_{SINK} = 250 \mu A$                                                         |

| 20                | $\Omega$ typ                                                                                                                                                                          | $I_{SOURCE} = 250 \mu A$                                                       |

| 850               |                                                                                                                                                                                       | $I_{SINK} = 250 \mu A$                                                         |

|                   | 31                                                                                                                                                                                    | SHVK .                                                                         |

|                   |                                                                                                                                                                                       | POWER-UP Tx = 0 V                                                              |

|                   |                                                                                                                                                                                       |                                                                                |

| 2.4/2.6           | XX ' /XX                                                                                                                                                                              |                                                                                |

|                   |                                                                                                                                                                                       |                                                                                |

| 25                | mV max                                                                                                                                                                                |                                                                                |

|                   |                                                                                                                                                                                       |                                                                                |

| $V_{\rm DD}$ -0.9 | V min                                                                                                                                                                                 |                                                                                |

| 0.9               | V max                                                                                                                                                                                 |                                                                                |

| 10                | μA max                                                                                                                                                                                |                                                                                |

| 10                |                                                                                                                                                                                       |                                                                                |

|                   | <del>-   ^</del> -                                                                                                                                                                    |                                                                                |

| 4.0               | V min                                                                                                                                                                                 | $ I_{OUT}  \leq 200 \mu A$                                                     |

|                   |                                                                                                                                                                                       | $ I_{\text{OUT}}  \le 200 \mu\text{A}$<br>$ I_{\text{OUT}}  \le 1.6 \text{mA}$ |

| 0.4               | v max                                                                                                                                                                                 | $ I_{\text{OUT}}  \le 1.0 \text{ mA}$                                          |

|                   |                                                                                                                                                                                       |                                                                                |

| 4.65/5.35         | V min/V max                                                                                                                                                                           |                                                                                |

|                   |                                                                                                                                                                                       |                                                                                |

| 62                | mA max                                                                                                                                                                                |                                                                                |

| 1                 | 1 -                                                                                                                                                                                   | DOWED IN TO A II                                                               |

| 40                | mA max                                                                                                                                                                                | POWER-UP Tx = 0 V                                                              |

| 40 22             | mA max<br>mA max                                                                                                                                                                      | POWER-UP Ix = 0 V<br>POWER-UP Rx = 0 V<br>POWER-UP Tx = POWER-UP Rx = 0 V      |

|                   | -30 -33 -60 -70 -70 -70 -60 0.7 1.5  -3 -20 -44  52 -70 Binary Yes  8  ±2 ±1 1.25 ± 1 ±60 0 to 2.5 2 20 850 Binary Yes  2.4/2.6 25  V <sub>DD</sub> -0.9 0.9 10 10 4.0 0.4  4.65/5.35 | -30                                                                            |

-3-REV. A

<sup>&</sup>lt;sup>1</sup>Operating temperature ranges as follows: A Version; -25°C to +85°C.

<sup>2</sup>AUX DAC dc linearity is measured between codes 5 and 255, see terminology.

<sup>3</sup>Variation of the Reference between different POWER-UP Tx and POWER-UP Rx modes.

<sup>&</sup>lt;sup>4</sup>Measured while the digital inputs to the transmit interface are static. <sup>5</sup>Measured while the digital inputs to the receive interface are static. <sup>6</sup>Measured while the digital inputs are equal to 0 V or V<sub>DD</sub>.

Specifications subject to change without notice.

## ABSOLUTE MAXIMUM RATINGS\*

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| V <sub>DD</sub> Tx, V <sub>DD</sub> Rx to AGND | 0.3 V to +7 V                              |

|------------------------------------------------|--------------------------------------------|

|                                                | $-0.3~V$ to $+0.3~V$                       |

| Digital I/O Voltage to DGND.                   | $-0.3$ V to $V_{\mathbf{DD}}$ + $0.3$ V    |

| Analog I/O Voltage to AGND .                   | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Operating Temperature Range                    |                                            |

|                                                | 3500 0500                                  |

## **ORDERING GUIDE**

| Model    | Temperature    | Package               | Package |

|----------|----------------|-----------------------|---------|

|          | Range          | Description           | Option  |

| AD7001AS | -25°C to +85°C | Plastic Quad Flatpack | S-44    |

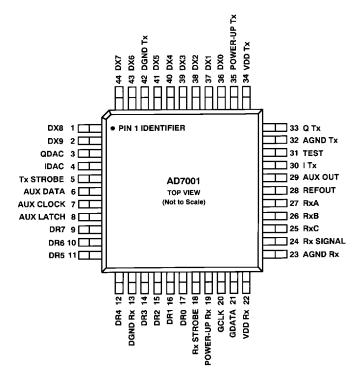

#### PIN CONFIGURATION

## CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 volts, which readily accumulate on the human body and on test equipment, can discharge without detection. Although devices feature proprietary ESD protection circuitry, permanent damage may still occur on these devices if they are subjected to high energy electrostatic discharges. Therefore, proper precautions are recommended to avoid any performance degradation or loss of functionality.

Table I. Truth Table for IDD Control

| POWER-UP Tx | POWER-UP Rx | Operation                                       | I <sub>DD</sub> max |

|-------------|-------------|-------------------------------------------------|---------------------|

| 0           | 0           | All Sections Powered Down                       | 2 mA                |

| 0           | 1           | Tx Section Powered Down, Rx Section Operational | 40 mA               |

| 1           | 0           | Tx Section Operational, Rx Section Powered Down | 22 mA               |

| 1           | 1           | All Sections Operational                        | 62 mA               |

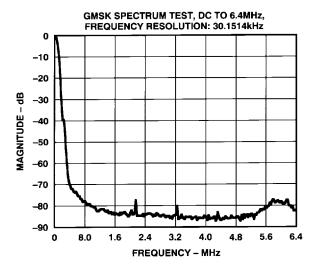

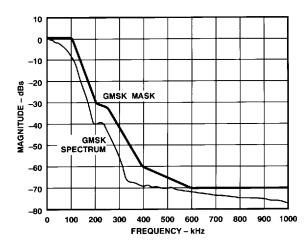

Figure 1. AD7001 Transmit GMSK Spectrum Mask

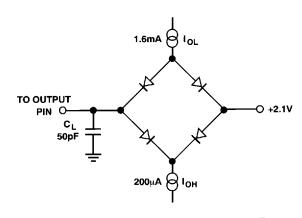

Figure 2. Load Circuit for Access Time Test

REV. A

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### TERMINOLOGY

## Signal Input Range

The input signal range for Rx SIGNAL is biased about  $V_{REF}$ . It can go  $\pm V_{REF}/2$ ,  $\pm V_{REF}/4$  or  $\pm V_{REF}/8$  volts (depending on the PGA setting) about this point.

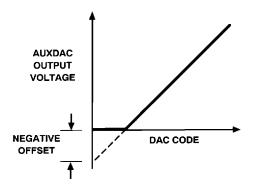

## Auxiliary DAC Linearity

The AUX DAC output amplifier can have an internal negative offset, even though the part operates from a single (5 V) supply. However, because the negative rail is 0 V, the output cannot actually go below ground, resulting in the transfer function shown below. This "Knee" is an offset effect, not a linearity error, and the transfer function would have followed the dotted line if the output voltage could have gone negative.

Normally, linearity is measured between zero (all 0s) and full scale (all 1s) after offset and full scale have been adjusted out, but this is not possible with the AD7001 AUX DAC if the offset is negative. Instead, linearity of the AUX DAC is measured between full scale and the lowest code which is guaranteed to produce a positive output voltage. This code is calculated from the maximum specification for negative offset. For the AD7001 AUX DAC the linearity is measured between codes 5 and 255.

Effect of Negative Offset

## Bias Offset Error

This is the offset error (in LSBs) in the DAC or ADC and is measured with respect to  $V_{REF}$ .

## Signal-to-Noise Ratio

Signal-to-noise ratio (SNR) is the measured signal to noise at the output of the receive channel. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc. SNR is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical SNR for a sine wave is given by:

SNR = (6.02 N + 1.76) dB

## Differential Group Delay

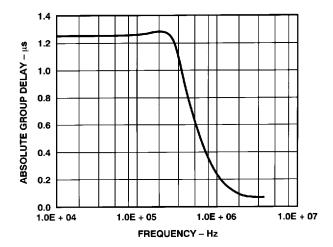

Absolute group delay is the rate of change of phase versus frequency, dφ/df. For the AD7001, differential group delay is the absolute group delay in a specified band relative to the absolute group delay at 10 kHz. The specified band for the AD7001 is 10 kHz-200 kHz.

## Group Delay Between Channels

This is the difference between the group delay of the I and Q channels and is a measure of the phase matching characteristics of the two.

#### **Output Signal Span**

This is the output signal range for the transmit channel section and the auxiliary DAC section. For the transmit channel the span is  $\pm 1.25$  volts centered on  $V_{REF}$  and for the auxiliary DAC section it is 0 to  $+V_{REF}$ .

## **Output Signal Full-Scale Accuracy**

This is the accuracy of the full scale output (all 1s loaded to the DACs) on the transmit channel and is expressed in dBs.

## **DAC Offset Error**

This is the amount of offset in the transmit DACs and the auxiliary DACs and is expressed in mVs for the transmit section and in LSBs for the auxiliary section.

#### **AUXDAC Full-Scale Error**

This is a measure of the output error between an ideal full-scale output of 2.5 V and the measured output when all 1s are loaded.

## **Output Impedance**

This is a measure of the drive capability of the auxiliary DAC output and is expressed in  $k\Omega$ s.

## **GMSK Spectrum Mask**

This is the output spectrum of the I and Q transmit channels when transmitting a random sequence of data bits using GMSK modulation, as specified in the GSM standard, using a bit truncation of  $\pm 6$  bit periods.

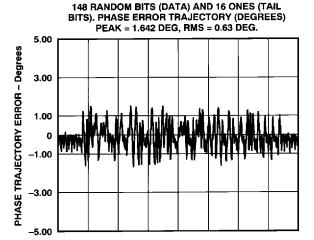

## **GMSK Phase Trajectory Error**

This is a measure of the phase error between the transmitted phase of an ideal GMSK modulator and the actual phase transmitted by the AD7001, when transmitting a random sequence of data bits. It is specified as a peak phase error and also as a rms phase error.

REV. A -5-

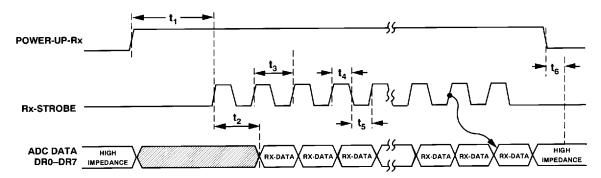

# ADC TIMING (V\_DD Tx = V\_DD Rx = +5 V $\pm$ 7%; Test = AGND Tx = AGND Rx = DGND Tx = DGND Rx = 0 V; unless otherwise noted)

| Parameter         | Limit at $T_A = -25^{\circ}C$ to $+85^{\circ}C$ | Units  | Description                              |

|-------------------|-------------------------------------------------|--------|------------------------------------------|

| t,                | 100                                             | μs min | POWER-UP Rx to Rx STROBE Setup Time      |

|                   | $t_3 + 100$                                     | ns min | Rx STROBE to New Rx DATA                 |

| -                 | $t_3 + 220$                                     | ns max |                                          |

| 3                 | 460                                             | ns min | Rx STROBE Period                         |

| 4                 | 200                                             | ns min | Rx STROBE High Period                    |

| <del>*</del><br>5 | 200                                             | ns min | Rx STROBE Low Period                     |

| 6                 | 0                                               | ns min | POWER-UP Rx Going Low to Rx DATA 3-State |

| · ·               | 40                                              | ns max |                                          |

## NOTES

<sup>2</sup>See Figure 2.

$<sup>^4</sup>$ t<sub>6</sub> is derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 2. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t<sub>6</sub>, quoted in the timing characteristics is the true bus relinquish time of the part and as such is independent of external bus loading capacitances.

Figure 3. ADC Timing Diagram

$<sup>^{1}</sup>$ All input signals are specified with tr= tf= 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

$<sup>^{3}</sup>t_{2}$  is measured with the load circuit of Figure 1 and is defined as the time required for an output to cross 0.8 V or 2.4 V.

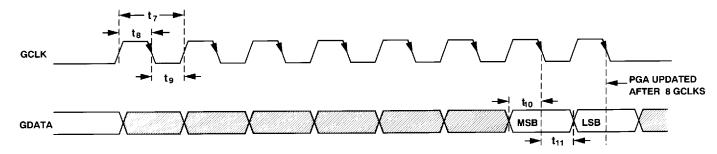

## **PGA TIMING** $(V_{DD} Tx = V_{DD} Rx = +5 V \pm 7\%; Test = AGND Tx = AGND Rx = DGND Tx = DGND Rx = 0 V; unless otherwise noted)$

| Parameter       | Limit at<br>T <sub>A</sub> = +25°C | Limit at $T_A = -25^{\circ}C$ to $+85^{\circ}C$ | Units  | Description              |

|-----------------|------------------------------------|-------------------------------------------------|--------|--------------------------|

| t <sub>7</sub>  | 150                                | 150                                             | ns min | GCLK Period              |

| t <sub>8</sub>  | 75                                 | 75                                              | ns min | GCLK Low Period          |

| t <sub>o</sub>  | 75                                 | 75                                              | ns min | GCLK High Period         |

| t <sub>10</sub> | 40                                 | 40                                              | ns min | GDATA to GCLK Setup Time |

| t <sub>11</sub> | 50                                 | 50                                              | ns min | GDATA to GCLK Hold Time  |

## NOTES

<sup>1</sup>All input signal rise and fall times measured from 10% to 90% of +5 V; tr = tf = 10 ns.

$<sup>^2</sup> Timing$  measurement reference level is (V  $_{IH}$  + V  $_{IL})\!/2$  .

Figure 4. PGA Timing Diagram

# **SIGNAL DAC TIMING** ( $V_{DD}$ Tx = $V_{DD}$ Rx = +5 V ± 7%; Test = AGND Tx = AGND Rx = DGND Tx = DGND Rx = OV; unless otherwise noted)

| Parameter       | Limit at $T_A = -25^{\circ}C \text{ to } +85^{\circ}C$ | Units  | Description                          |

|-----------------|--------------------------------------------------------|--------|--------------------------------------|

|                 | 100                                                    | μs min | POWER-UP Tx to Tx STROBE Setup Time. |

| t <sub>13</sub> | 100                                                    | ns min | IDAC, QDAC Pulse Width               |

| t <sub>14</sub> | 40                                                     | ns min | Tx DATA Setup Time                   |

| t <sub>15</sub> | 10                                                     | ns min | Tx DATA Hold Time                    |

| t <sub>16</sub> | 50                                                     | ns min | IDAC to Tx STROBE Setup Time         |

| t <sub>17</sub> | 50                                                     | ns min | QDAC to Tx STROBE Setup Time         |

| t <sub>18</sub> | 100                                                    | ns min | Tx STROBE Pulse Width                |

| t <sub>19</sub> | 400                                                    | ns min | Tx STROBE Period                     |

## NOTES

<sup>&</sup>lt;sup>2</sup>Timing measurement reference level is  $(V_{IH} + V_{IL})/2$ .

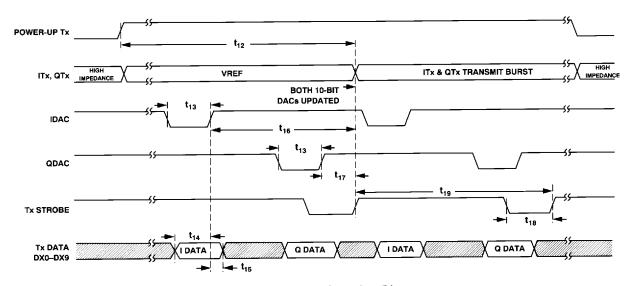

Figure 5. Signal DAC Timing Diagram

$<sup>^{1}</sup>All$  input signal rise and fall times measured from 10% to 90% of +5 V; tr = tf = 20 ns.

# **AUXILIARY DAC TIMING** $(V_{DD} Tx = V_{DD} Rx = +5 V \pm 7\%; Test = AGND Tx = AGND Rx = DGND Tx = DGND Rx = 0 V; unless otherwise noted)$

| Parameter       | Limit at $T_A = -25^{\circ}C \text{ to } +85^{\circ}C$ | Units  | Description                       |

|-----------------|--------------------------------------------------------|--------|-----------------------------------|

| t <sub>20</sub> | 75                                                     | ns min | AUX CLOCK Low Duration            |

| 21              | 75                                                     | ns min | AUX CLOCK High Duration           |

| 22              | 40                                                     | ns min | AUX DATA to AUX CLOCK Setup Time  |

| 23              | 50                                                     | ns min | AUX DATA to AUX CLOCK Hold Time   |

| 24              | 50                                                     | ns min | AUX LATCH to AUX CLOCK Setup Time |

| 25              | 40                                                     | ns min | AUX LATCH to AUX CLOCK Hold Time  |

| 26              | $8(t_{20}+t_{21})$                                     | ns min | AUX LATCH Duration                |

## NOTES

<sup>&</sup>lt;sup>2</sup>Timing measurement reference level is  $(V_{IH} + V_{IL})/2$ .

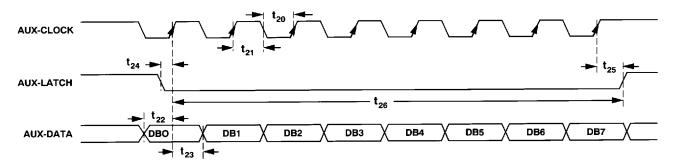

Figure 6. Auxiliary DAC Timing Diagram

<sup>&</sup>lt;sup>1</sup>All input signal rise and fall times measured from 10% to 90% of +5 V; tr = tf = 20 ns.

## TRANSMIT SECTION

The transmit section of the AD7001 performs the baseband conversion of I and Q (In-phase and Quadrature) waveforms for the GSM Pan-European Digital Cellular Communications system. The transmit channel consists of two 10-bit DACs, followed by 4th order Bessel reconstruction filters. Also included in the transmit channel is a single 8-bit auxiliary DAC.

## Transmit DACs

The 10-bit DACs can be used to perform the conversion of I and Q waveforms when implementing GMSK modulation in accordance with the GSM 5.04 standard.

#### Reconstruction Filters

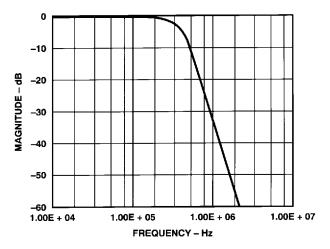

The reconstruction filters smooth the DAC output signals, providing continuous time I and Q waveforms at the output pins. These are 4th order Bessel low-pass filters with a cutoff frequency of approximately 300 kHz. Figure 7 shows a typical transmit filter frequency response, while Figure 8 shows a typical plot of group delay versus frequency. The filters are designed to have a linear phase response in the passband and due to the reconstruction filters being on-chip, the phase mismatch between the I and Q transmit channels is kept to a minimum.

## Transmit DACs Digital Interface

The 10-bit DACs are double buffered, allowing the DACs to be simultaneously updated via a single 10-bit data bus (DX0-DX9). Figure 5 illustrates the Timing interface for the I and Q DACs. The I and Q latches are loaded on the rising edges of IDAC and QDAC, respectively, with data on the DX0-DX9 databus. When both latches have been updated, Tx STROBE is then used to transfer the contents of both I and Q Latches to the 10-bit DACs.

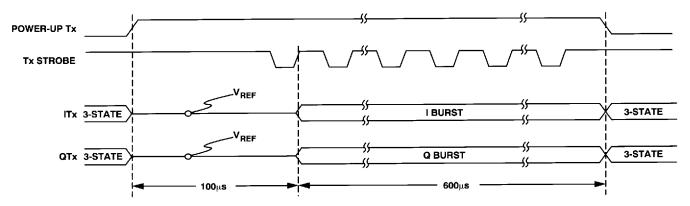

The transmit DACs are put into sleep mode (drawing minimum current) by bringing POWER-UP Tx low. During sleep mode the I Tx and Q Tx outputs go into high impedance. On POWER-UP Tx going high, the I and Q DACs are reset to V<sub>REF</sub>, which prevents any imbalance between the I and Q channels when the I Tx and Q Tx outputs are ac coupled to the IF/RF modulator. Allow time for the transmit section to fully power-up before updating the I and Q latches. Figure 9 shows a typical GSM transmission burst.

Figure 7. Transmit Filter Frequency Response

Figure 8. Transmit Filter Group Delay

Figure 9. Typical GSM Transmission Burst

-10-

Figure 10. Transmit GMSK Composite Spectrum (0–6.4 MHz)

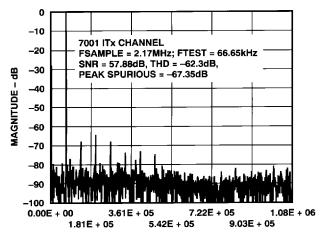

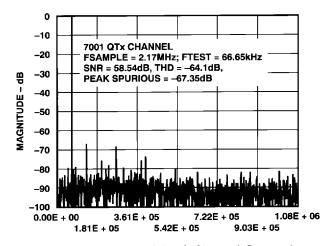

Figure 12. Frequency Plot of the I Channel Generating a Sine Wave at 66.65 kHz

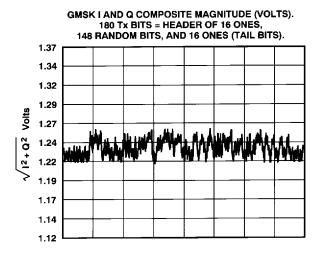

Figure 14. Typical Plot of the GMSK I and Q Composite Magnitude Generated Using the I and Q Transmit Channels

Figure 11. Transmit GMSK Composite Spectrum (0–1 MHz)

Figure 13. Frequency Plot of the Q Channel Generating a Sine Wave at 66.65 kHz

I AND Q WAVEFORMS GENERATED FROM 180 DATA BITS MADE UP OF A HEADER OF 16 ONES,

Figure 15. Typical Plot of the GMSK Phase Error Trajectory Generated Using the AD7001 I and Q Transmit Channels

-11-

## **Auxiliary DAC**

An 8-bit auxiliary serial DAC is also provided for such functions as Automatic Gain Control or for ramping up/down the transmit power amplifiers during the beginning/end of a transmit burst. Interfacing to the auxiliary section is accomplished via a serial interface.

The AD7001 auxiliary DAC is a voltage mode DAC, consisting of R-2R ladder network, constructed from highly stable thin-films resisters and high speed single pole, double throw switches.

The output of the voltage mode auxiliary DAC is buffered by a noninverting CMOS amplifier with a gain of two. This scales the output of the R-2R network from a voltage range of 0 –  $V_{\rm REF}/2$  to a voltage range of 0– $V_{\rm REF}$ . Due to the single supply operation of the buffer it has limited sink capability near ground.

#### **AUX DAC Digital Interface**

The serial interface timing is illustrated in Figure 6. The serial interface is controlled using AUX CLOCK, AUX LATCH and AUX DATA. AUX LATCH must go low prior to the clocking of new serial data, this prevents the AUX DAC output from being corrupted while new serial data is being loaded. The AUX CLOCK must be a gated clock; i.e., it must only be active when loading the auxiliary DAC. AUX DATA is latched on the rising edge of AUX CLOCK. When eight data bits have loaded, where DB0 is the LSB and DB7 is the MSB, AUX LATCH is brought high to update the AUX DAC output.

The auxiliary DAC is also put into sleep mode by bringing POWER-UP Tx low. During sleep mode the AUX DAC output is put into high impedance. The auxiliary DAC does not lose its contents while in sleep mode and will power-up to its previous value and settle within  $100~\mu s$ . The auxiliary DAC can also be loaded with new data while in sleep mode thereby allowing the AUX DAC output to power-up to a different value. However, while exercising the serial interface during sleep mode, the sleep current will increase.

### RECEIVE SECTION

The receive channel consists of a low power, two stage flash 8-bit analog to digital converter (ADC) combined with an on-chip sample and hold amplifier (SHA) and a PGA. The PGA provides programmable gains settings of 1, 2 or 4. Also included in the receive path is a differential amplifier.

## Differential Amplifier

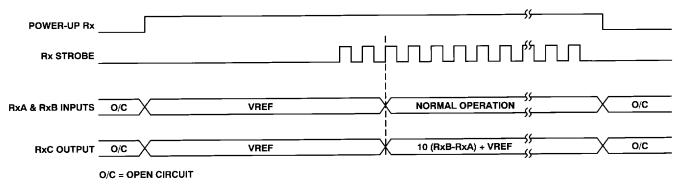

The differential amplifier provides a means for amplifying the IF receive signal before being digitized. The differential inputs can configured either for single-ended or for differential-ended operation. The RxC output can be directly connected to the Rx SIGNAL pin. For optimum performance the inputs (RxA and RxB) should be ac coupled, as this ensures proper internal biasing around  $V_{\rm REF}$ . The output (RxC) of the differential amplifier is given as:

$$RxC = 10 (RxB-RxA) + V_{REF}$$

POWER-UP Rx is used to put the differential amplifier into sleep mode. Figure 16 illustrates the operation of the differential amplifier under the control of POWER-UP Rx and Rx STROBE. While the receive section is in sleep mode (POWER-UP Rx low), the differential inputs (RxA and RxB) are open circuit. On POWER-UP Rx going high, the differential inputs are then connected to  $V_{REF}$  through a nominal impedance of 300  $\Omega$ . The inputs are connected for normal operation after two Rx STROBE cycles, i.e., on the third rising edge of Rx STROBE. If RXC is directly connected to Rx SIGNAL, then the first two ADC conversions, after POWER-UP RX going high, can be used to measure the combined offset of both the differential amplifier and the ADC channel.

## **PGA**

The PGA allows Rx SIGNAL to be amplitude by a factor 1, 2 or 4 depending on the value loaded into the 2-bit PGA register. When power is applied to the part, the 2-bit PGA register will be uninitialized and, therefore, must be initialized as described in the following section.

## **PGA** Digital Interface

The receive channel PGA is programmed via a two pin serial interface (GCLK and GDATA). Figure 4 illustrates the serial interface timing diagram for the PGA. GDATA is latched on the falling edge of GCLK. GCLK must be a gated clock, active only when updating the PGA. Eight clock cycles are required to update the PGA setting, where the first six cycles are dummy cycles and only the last two clock cycles load new data into the 2-bit PGA register. These last two data bits are loaded MSB first. On the last falling edge of GCLK the PGA is set to a gain of 1, 2 or 4, depending on the 2-bit value contain in the PGA register. Table II illustrates the truth table for the PGA setting.

Table II. PGA Truth Table

| MSB | LSB | PGA Gain |

|-----|-----|----------|

| 0   | 0   | 1        |

| 0   | 1   | 2        |

| 1   | 0   | 2        |

| 1   | 1   | 4        |

Figure 16. Operation of the Differential Amplifier

On initial power being applied to the part, the PGA serial logic will be in an undetermined state; however, each time the receive section is brought out of sleep mode (POWER-UP Rx brought high) the serial logic is reset. In order to correctly initialize the 2-bit PGA register, one must first reset the serial logic after power has initially been applied to the part. The PGA can be updated at any time, except when the serial logic is being reset. Hence, one should not attempt to update the PGA register immediately before or after POWER-UP Rx goes high. A guard band of 150 ns before and 300 ns after POWER-UP Rx going high is sufficient for correct operation.

## SHA and ADC

The 8-bit flash pipelined ADC combined with the on-board Sample and Hold Amplifier (SHA) generates 8-bit samples up to a data rate of 2.17 MHz.

## **ADC** Digital Interface

Figure 3 illustrates the receive timing interface, control of the receive interface is effected through the use of the POWER-UP RX and Rx-STROBE pins with the receive data available on a parallel interface (DR0-DR7). Conversions are initiated on the rising edge of Rx-STROBE and the DR0-DR7 pins are updated on the following rising edge of Rx-STROBE, after approximately 130 ns. On POWER-UP RX going high time (t<sub>1</sub>) must be provided to allow the receive circuity to become fully powered up. Rx-STROBE can now be activated to initiate ADC conversions.

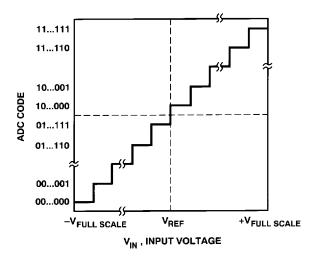

Figure 17. ADC Transfer Function

As described earlier, if the differential amplifier is connected to  $Rx\ SIGNAL$ , the first two conversions can be used to measure the offset contained in the receive path. The user can average the first two conversions to obtain an offset value which can subtracted, by the user, from subsequent ADC conversions. Although the ADC will continue to convert, time must be allowed for the differential amplifier to settle due to the internal switching from  $V_{\rm REF}$  to the RX A and RX B input pins.

## **VOLTAGE REFERENCE**

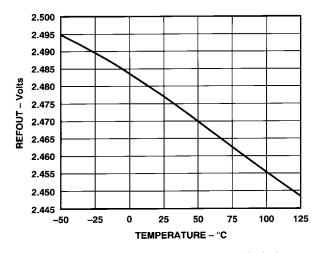

The AD7001 contains an on-chip bandgap reference which provides a low noise, temperature compensated reference to the I/Q transmit DACs and the I/Q receive ADC. The Reference is also make available on the REFOUT pin and can be used to bias other analog circuit in the in the IF section.

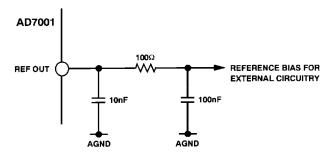

A decoupling scheme as illustrated in Figure 18 should be used to decouple the reference for correct operation. If the reference is required to bias external circuitry, then this should be connected after the  $100~\Omega$  series resistance.

When both the transmit section and the receive section are in sleep mode (POWER-UP TX and POWER-UP RX low), the reference output buffer is also powered down by approximately 80%.

Figure 18. Reference Decoupling for the REF OUT Pin

Figure 19. Typical Plot of Reference Variation vs. Temperature

## PIN FUNCTION DESCRIPTION

| PQFP Pin<br>Number | Mnemonic         | Function                                                                                                                                                                                                                                 |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUP          | PLY              |                                                                                                                                                                                                                                          |

| 34                 | $V_{DD}$ Tx      | Positive Power Supply for transmit section.                                                                                                                                                                                              |

| 22                 | $V_{DD}^{-1}$ Rx | Positive Power Supply for receive section. Both V <sub>DD</sub> pins must be tied together.                                                                                                                                              |

| 32                 | AGND Tx          | Analog Ground for transmit section.                                                                                                                                                                                                      |

| 23                 | AGND Rx          | Analog Ground for receive section. Both AGND pins must be tied together.                                                                                                                                                                 |

| 42                 | DGND Tx          | Digital Ground for transmit section.                                                                                                                                                                                                     |

| 13                 | DGND Rx          | Digital Ground for receive section. Both DGND pins must be tied together.                                                                                                                                                                |

| ANALOG SIG         | GNAL AND REFEREN | NCE                                                                                                                                                                                                                                      |

| 28                 | REF OUT          | Reference Output, this is 2.5 V nominal.                                                                                                                                                                                                 |

| 24                 | Rx SIGNAL        | Analog Input for receive channel.                                                                                                                                                                                                        |

| 30                 | I Tx             | Analog Output Voltage from the I transmit channel. This output comes from a 10-bit DAC and is filtered by a 4th order Bessel low-pass filter.                                                                                            |

| 33                 | Q Tx             | Analog Output Voltage from the Q Transmit channel. This output comes from a 10-bit DAC and is filtered by a 4th order Bessel low-pass filter.                                                                                            |

| 29                 | AUX DAC          | Analog Output Voltage from the 8-bit Auxiliary DAC. This output comes from a buffer amplifier.                                                                                                                                           |

| 27                 | RxA              | Analog Input for the inverting input of the differential amplifier.                                                                                                                                                                      |

| 26                 | RxB              | Analog Input for the noninverting input of the differential amplifier.                                                                                                                                                                   |

| 25                 | RxC              | Analog Output Voltage from the differential amplifier.                                                                                                                                                                                   |

| 23                 | KXC              | maiog output voltage from the differential amplifier.                                                                                                                                                                                    |

| TRANSMIT           | INTERFACE AND CO | NTROL                                                                                                                                                                                                                                    |

| 5                  | Tx STROBE        | Transmit Strobe, Digital Input. Tx STROBE transfers the contents of both the I and Q                                                                                                                                                     |

|                    |                  | Latches, on a rising edge, to the I and Q 10-bit DACs, respectively. This is used to update both 10-bit DACs simultaneously after the I and Q latches have been loaded via a single 10-bit port.                                         |

| 4                  | I DAC            | I Latch Update, Digital Input. I DAC is used to update the I latch via DX9-DX0. This is an edge triggered latch, DX9-DX0 are latched on the rising edge of I DAC.                                                                        |

| 3                  | Q DAC            | Q Latch Update, Digital Input. Q DAC is used to update the Q latch via DX9-DX0. This is an edge triggered latch, DX9-DX0 are latched on the rising edge of Q DAC.                                                                        |

| 2,1                | DX9, DX8         | Transmit Data Bit 9 and Data Bit 8, digital inputs. DX9 is the most significant bit (MSB).                                                                                                                                               |

| 44, 43             | DX7, DX6         | Transmit Data Bit 7 and Data Bit 6, digital inputs.                                                                                                                                                                                      |

| 41–36              | DX5-DX0          | Transmit Data Bits 5 to 0, digital inputs. DX0 is the least significant bit (LSB).                                                                                                                                                       |

| 7                  | AUX CLOCK        | Auxiliary Clock, edge triggered digital input. Serial data bits are latched on the rising edge AUX CLOCK when AUX LATCH is low. AUX CLOCK must be a gated clock, which is only active when data is being loaded into the serial register |

| 6                  | AUX DATA         | Auxiliary Data, digital input. This data input is used in conjunction with AUX CLOCK and AUX LATCH to load the 8-bit Auxiliary DAC register.                                                                                             |

| 8                  | AUX LATCH        | Level triggered Digital Input. AUX LATCH controls the transfer of data between the AUX                                                                                                                                                   |

|                    |                  | DAC serial register and the AUX DAC latch. When high, the AUX DAC latch is                                                                                                                                                               |

| 35                 | POWER-UP Tx      | transparent. Data is latched when AUX LATCH is brought low. Power-Up Transmit, Digital Input. When this goes low the transmit section goes into                                                                                          |

|                    |                  | standby mode, drawing minimum current.                                                                                                                                                                                                   |

|                    | TERFACE AND CON  | TROL                                                                                                                                                                                                                                     |

| 18                 | Rx STROBE        | Receive Strobe, Digital Input. Rx STROBE initiates an ADC conversion, at the end of which DR7-DR0 are updated.                                                                                                                           |

| 9–12               | DR7-DR4          | Receive Data Bits 7 to 4, Digital Outputs. DR7 is the most significant bit (MSB).                                                                                                                                                        |

| 14–17              | DR3-DR0          | Receive Data Bits 3 to 0, Digital Outputs. DR0 is the least significant bit (LSB).                                                                                                                                                       |

| 20                 | GCLK             | PGA Clock, Digital Input. GDATA bits are latched on the falling edge of GCLK. The PGA must be loaded using 8 GCLKs, the last two bits that are loaded are used to set the PGA.                                                           |

| 21                 | GDATA            | Programmable Gain Data, Digital Input. This input is used in conjunction with GCLK to set the gain for the PGA.                                                                                                                          |

| 19                 | POWER-UP Rx      | Power-Up Receive, Digital Input. When this goes low the receive section goes into standby mode, drawing minimal current.                                                                                                                 |

| 31                 | TEST             | Test mode, Digital Input. This pin is used to put the device into a special factory test mode. For normal device operation this pin must be tied to DGND.                                                                                |

-14- REV. A

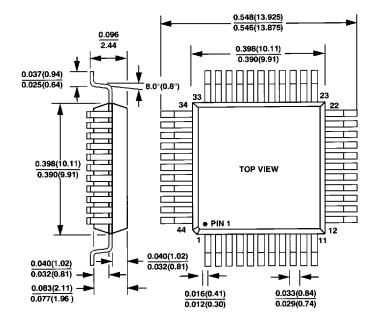

## **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

## Plastic Quad Flatpack (S) Package (S-44)