# **Preliminary Technical Data**

# **Tri-Axis Inertial Sensor**

# ADIS16365

# FEATURES

Tri-axis gyroscope with digital range scaling ±75°/sec, ±150°/sec, ±300°/sec settings 14-bit resolution Tri-axis accelerometer ±17 g measurement range 14-bit resolution 350 Hz bandwidth Factory calibrated sensitivity, bias, and alignment Calibration temperature range: -40°C to +85°C External clock input for sample synchronization **Digitally controlled bias calibration Digitally controlled sample rate Digitally controlled filtering Programmable condition monitoring** Auxiliary digital input/output **Digitally activated self-test** Programmable power management **Embedded temperature sensor** SPI-compatible serial interface Auxiliary 12-bit ADC input and DAC output Single-supply operation: 4.75 V to 5.25 V 2000 g shock survivability Operating temperature range: -40°C to +105°C

# APPLICATIONS

Guidance and control Platform control and stabilization Motion control and analysis Inertial measurement units General navigation Image stabilization Robotics

### **GENERAL DESCRIPTION**

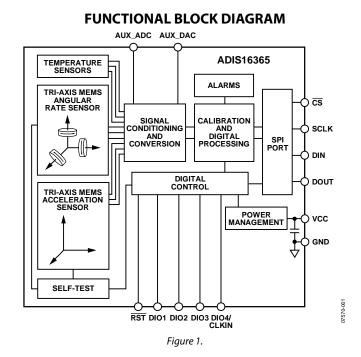

The ADIS16365 *i*Sensor<sup>\*</sup> is a complete triple axis gyroscope and triple axis accelerometer inertial sensing system. This sensor combines the Analog Devices, Inc., *i*MEMS<sup>\*</sup> and mixed signal processing technology to produce a highly integrated solution that provides calibrated, digital inertial sensing. An SPI interface and simple output register structure allow for easy access to data and configuration controls.

The SPI port provides access to the following embedded sensors: X-, Y-, and Z-axis angular rates; X-, Y-, and Z-axis linear acceleration; internal temperature; power supply; and auxiliary analog input. The inertial sensors are precision-aligned across axes and

#### Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

are calibrated for offset and sensitivity over the industrial temperature range of -40 to  $+85^{\circ}$ C. An embedded controller dynamically compensates for all major influences on the sensors, thus maintaining highly accurate sensor outputs without further testing, circuitry, or user intervention.

The following programmable features simplify system integration: in-system autobias calibration, digital filtering and sample rate, self-test, power management, condition monitoring, and auxiliary digital input/output.

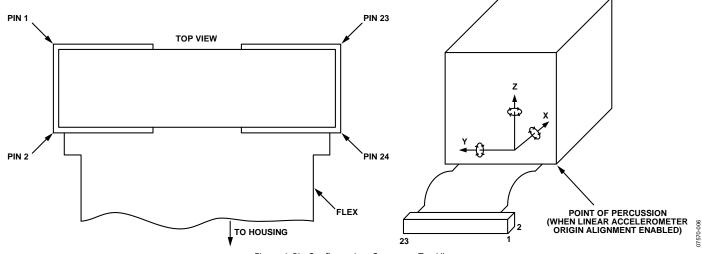

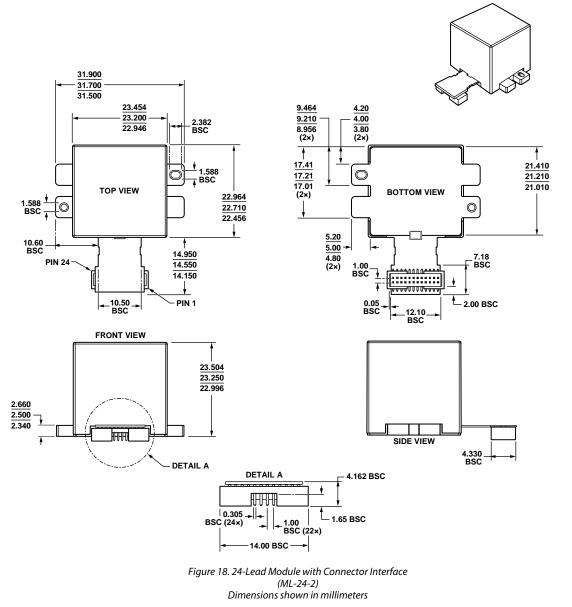

This compact module is approximately 23 mm × 23 mm × 23 mm and provides a convenient flex-based connector system.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2008 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features                                    |

|---------------------------------------------|

| Applications1                               |

| Functional Block Diagram1                   |

| General Description                         |

| Specifications                              |

| Timing Specifications6                      |

| Timing Diagrams6                            |

| Absolute Maximum Ratings7                   |

| ESD Caution7                                |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Basic Operation                             |

| Physical Installation10                     |

| Initial Hook-Up and Configuration | 10 |

|-----------------------------------|----|

| Data Collection                   | 10 |

| Device Configuration              | 11 |

| Burst Mode Data Collection        | 11 |

| Output Data Registers             | 12 |

| Calibration                       | 12 |

| Operation Control Registers       | 13 |

| Input/Output Functions            | 14 |

| Diagnostics                       | 15 |

| Outline Dimensions                | 17 |

| Ordering Guide                    | 17 |

# **SPECIFICATIONS**

$T_A = -40^{\circ}$ C to +85°C,  $V_{CC} = 5.0$  V, angular rate = 0°/sec, dynamic range = 300°/sec, ±1 g, unless otherwise noted.

| Parameter                        | Conditions                                                      | Min    | Тур          | Max    | Unit           |

|----------------------------------|-----------------------------------------------------------------|--------|--------------|--------|----------------|

| GYROSCOPE SENSITIVITY            | Each axis                                                       |        |              |        |                |

| Initial Sensitivity              | $25^{\circ}$ C, dynamic range = $\pm 300^{\circ}$ /sec          | 0.0405 | 0.05         | 0.0505 | °/sec/LSB      |

| ·                                | $25^{\circ}$ C, dynamic range = $\pm 150^{\circ}$ /sec          |        | 0.025        |        | °/sec/LSB      |

|                                  | $25^{\circ}$ C, dynamic range = $\pm 75^{\circ}$ /sec           |        | 0.0125       |        | °/sec/LSB      |

| Temperature Coefficient          |                                                                 |        | 40           |        | ppm/°C         |

| Gyroscope Axis Nonorthogonality  | 25°C, difference from 90° ideal                                 |        | TBD          |        | Degree         |

| Gyroscope Axis Misalignment      | 25°C, relative to base plate and guide pins                     |        | ±0.5         |        | Degree         |

| Nonlinearity                     | Best fit straight line                                          |        | 0.1          |        | % of FS        |

| GYROSCOPE BIAS                   |                                                                 |        | 0.1          |        | 70 011 5       |

| In-Run Bias Stability            | 25°C, 1 σ                                                       |        | 0.007        |        | °/sec          |

| Angular Random Walk              | 25°C                                                            |        | 2.4          |        | °/√hr          |

| Temperature Coefficient          | 25 C                                                            |        | 2.4<br>0.1   |        | °/sec/°C       |

|                                  |                                                                 |        |              |        |                |

| Linear Acceleration Effect       | Any axis, 1 $\sigma$ (MSC_CTRL bit [7] = 1)                     |        | 0.05         |        | °/sec/g        |

| Voltage Sensitivity              | VCC = 4.75 V to 5.25 V                                          |        | 0.25         |        | °/sec/V        |

| GYROSCOPE NOISE PERFORMANCE      |                                                                 |        | -            |        |                |

| Output Noise                     | 25°C, ±300°/sec range, 1-tap filter setting                     |        | TBD          |        | °/sec rms      |

|                                  | 25°C, ±150°/sec range, 4-tap filter setting                     |        | TBD          |        | °/sec rms      |

|                                  | 25°C, ±75°/sec range, 16-tap filter setting                     |        | TBD          |        | °/sec rms      |

| Rate Noise Density               | $25^{\circ}$ C, f = 25 Hz, $\pm 300^{\circ}$ /sec, no filtering |        | TBD          |        | °/sec/√Hz rms  |

| GYROSCOPE FREQUENCY RESPONSE     |                                                                 |        |              |        |                |

| 3 dB Bandwidth                   |                                                                 |        | 350          |        | Hz             |

| Sensor Resonant Frequency        |                                                                 |        | 14           |        | kHz            |

| GYROSCOPE SELF-TEST STATE        |                                                                 |        |              |        |                |

| Change in output bias            | ±300°/sec range setting                                         | ±833   | ±1500        | ±2167  | LSB            |

| Internal Self-Test Cycle Time    |                                                                 |        | 25           |        | ms             |

| ACCELEROMETER SENSITIVITY        | Each axis                                                       |        |              |        |                |

| Dynamic Range                    |                                                                 |        | ±17          |        | g              |

| Initial Sensitivity              | 25°C                                                            | TBD    | 0.33         | TBD    | mg/LSB         |

| Temperature Coefficient          |                                                                 |        | 40           |        | ppm/°C         |

| Axis Nonorthogonality            | 25°C, difference from 90° ideal                                 |        | ±0.25        |        | Degree         |

| Axis Misalignment                | 25°C, relative to base plate and guide pins                     |        | ±0.5         |        | Degree         |

| Nonlinearity                     | Best fit straight line                                          |        | ±0.5<br>±0.2 |        | % of FS        |

| ACCELEROMETER BIAS               |                                                                 |        | ±0.2         |        | /00115         |

| In-Run Bias Stability            | 25°C, 1 σ                                                       |        | TBD          |        | ma             |

|                                  |                                                                 |        |              |        | mg             |

| Velocity Random Walk             | 25°C, 1 σ                                                       |        | TBD          |        | m/sec/√hr      |

|                                  |                                                                 |        | TBD          |        | m <i>g/</i> °C |

| ACCELEROMETER NOISE PERFORMANCE  |                                                                 |        |              |        |                |

| Output Noise                     | 25°C, no filtering                                              |        | TBD          |        | mg rms         |

| Noise Density                    | 25°C, no filtering                                              |        | TBD          |        | mg/√Hz rms     |

| ACCELEROMETER FREQUENCY RESPONSE |                                                                 |        |              |        |                |

| 3 dB Bandwidth                   |                                                                 |        | TBD          |        | Hz             |

| Sensor Resonant Frequency        |                                                                 |        | TBD          |        | kHz            |

| ACCELEROMETER SELF-TEST STATE    |                                                                 |        |              |        |                |

| Output Change When Active        |                                                                 |        | TBD          |        | LSB            |

| TEMPERATURE SENSOR               |                                                                 |        |              |        |                |

| Scale Factor                     | +25°C output = 0x0000                                           |        | 6.88         |        | LSB/°C         |

|                                  | 125 C Output - 0x0000                                           |        | 0.00         |        | LJD/ C         |

**Preliminary Technical Data**

| Parameter                               | Conditions                           | Min    | Тур  | Max   | Unit   |

|-----------------------------------------|--------------------------------------|--------|------|-------|--------|

| ADC INPUT                               |                                      |        |      |       | 1      |

| Resolution                              |                                      |        | 12   |       | Bits   |

| Integral Nonlinearity                   |                                      |        | ±2   |       | LSB    |

| Differential Nonlinearity               |                                      |        | ±1   |       | LSB    |

| Offset Error                            |                                      |        | ±4   |       | LSB    |

| Gain Error                              |                                      |        | ±2   |       | LSB    |

| Input Range                             |                                      | 0      |      | +3.3  | V      |

| Input Capacitance                       | During acquisition                   |        | 20   |       | pF     |

| DAC OUTPUT                              | 5 kΩ/100 pF to GND                   |        |      |       |        |

| Resolution                              |                                      |        | 12   |       | Bits   |

| Relative Accuracy                       | For Code 101 to Code 4095            |        | ±4   |       | LSB    |

| Differential Nonlinearity               |                                      |        | ±1   |       | LSB    |

| Offset Error                            |                                      |        | ±5   |       | mV     |

| Gain Error                              |                                      |        | ±0.5 |       | %      |

| Output Range                            |                                      |        |      | +3.3  | V      |

| Output Impedance                        |                                      |        | 2    |       | Ω      |

| Output Settling Time                    |                                      |        | 10   |       | μs     |

| LOGIC INPUTS <sup>1</sup>               |                                      |        |      |       |        |

| Input High Voltage, V <sub>INH</sub>    |                                      | 2.0    |      |       | V      |

| Input Low Voltage, V <sub>INL</sub>     |                                      |        |      | 0.8   | V      |

|                                         | CS signal to wake up from sleep mode |        |      | 0.55  | V      |

| Logic 1 Input Current, IINH             | $V_{IH} = 3.3 V$                     |        | ±0.2 | ±10   | μA     |

| Logic 0 Input Current, I <sub>INL</sub> | $V_{IL} = 0 V$                       |        |      |       |        |

| All Except RST                          |                                      |        | -40  | -60   | μA     |

| RST                                     |                                      |        | -1   |       | mA     |

| Input Capacitance, C <sub>IN</sub>      |                                      |        | 10   |       | pF     |

| DIGITAL OUTPUTS <sup>1</sup>            |                                      |        |      |       |        |

| Output High Voltage, V <sub>он</sub>    | $I_{SOURCE} = 1.6 \text{ mA}$        | 2.4    |      |       | V      |

| Output Low Voltage, Vo∟                 | $I_{SINK} = 1.6 \text{ mA}$          |        |      | 0.4   | V      |

| SLEEP TIMER                             |                                      |        |      |       |        |

| Timeout Period <sup>2</sup>             |                                      | 0.5    |      | 128   | Sec    |

| FLASH MEMORY                            |                                      |        |      |       |        |

| Endurance <sup>3</sup>                  |                                      | 10,000 |      |       | Cycles |

| Data Retention <sup>4</sup>             | TJ = 85°C                            | 20     |      |       | Years  |

| START-UP TIME <sup>5</sup>              | Time until data is available         |        |      |       |        |

| Power-On                                | Fast mode, SMPL_PRD $\leq$ 0x07      |        | TBD  |       | ms     |

|                                         | Normal mode, SMPL_PRD $\geq$ 0x08    |        | TBD  |       | ms     |

| Reset Recovery                          | Fast mode, SMPL_PRD $\leq$ 0x07      |        | TBD  |       | ms     |

|                                         | Normal mode, SMPL_PRD $\geq$ 0x08    |        | TBD  |       | ms     |

| Sleep Mode Recovery                     |                                      |        | TBD  |       | ms     |

| CONVERSION RATE                         |                                      |        |      |       |        |

| Sample Rate Settings                    | $SMPL_PRD = 0x01 \text{ to } 0xFF$   | 0.413  |      | 819.2 | SPS    |

| Clock Accuracy                          |                                      |        | TBD  |       |        |

| SYNC Input Clock                        |                                      |        |      | 1.2   | kHz    |

| Parameter                    | Conditions             | Min  | Тур | Мах  | Unit |

|------------------------------|------------------------|------|-----|------|------|

| POWER SUPPLY                 |                        |      |     |      |      |

| Operating Voltage Range, VCC |                        | 4.75 | 5.0 | 5.25 | V    |

| Power Supply Current         | Low power mode at 25°C |      | 24  |      | mA   |

|                              | Fast mode at 25°C      |      | 49  |      | mA   |

|                              | Sleep mode at 25°C     |      | 500 |      | μA   |

<sup>1</sup> The digital I/O signals are driven by an internal 3.3 V supply, and the inputs are 5 V tolerant.

<sup>2</sup> Guaranteed by design. <sup>3</sup> Endurance is qualified as per JEDEC Standard 22, Method A117, and measured at -40°C, +25°C, +85°C, and +125°C. <sup>3</sup> Retention lifetime equivalent at junction temperature (T.) 85°C as per JEDEC Standard 22, Method A117. Retention lifetime decreases with junction temperature. <sup>5</sup> The times presented in this section do not include the sensor's transient response time, which is associated with a 50 Hz single-pole system. System accuracy goals should be given consideration when determining the amount of time it takes to start acquiring accurate readings. These times do not include the time it takes to arrive at thermal stability, which can also introduce transient errors.

# TIMING SPECIFICATIONS

$T_A = 25^{\circ}C$ , VDD = +5 V, unless otherwise noted.

#### Table 2.

|                                         |                                        | -                | ast Moe<br>L_PRD <u>&lt;</u> |      |                         | Power M<br>L_PRD <u>&gt;</u> |      | Bu               | rst Mo | de   |      |

|-----------------------------------------|----------------------------------------|------------------|------------------------------|------|-------------------------|------------------------------|------|------------------|--------|------|------|

| Parameter                               | Description                            | Min <sup>1</sup> | Тур                          | Max  | <b>Min</b> <sup>1</sup> | Тур                          | Max  | Min <sup>1</sup> | Тур    | Max  | Unit |

| fsclк                                   |                                        | 0.01             |                              | 2.0  | 0.01                    |                              | 0.3  | 0.01             |        | 1.0  | MHz  |

| <b>t</b> stall                          | Stall period between data              | 9                |                              |      | 75                      |                              |      | 1/fsclk          |        |      | μs   |

| tcs                                     | Chip select to clock edge              | 48.8             |                              |      | 48.8                    |                              |      | 48.8             |        |      | ns   |

| t <sub>DAV</sub>                        | DOUT valid after SCLK edge             |                  |                              | 100  |                         |                              | 100  |                  |        | 100  | ns   |

| tdsu                                    | DIN setup time before SCLK rising edge | 24.4             |                              |      | 24.4                    |                              |      | 24.4             |        |      | ns   |

| <b>t</b> DHD                            | DIN hold time after SCLK rising edge   | 48.8             |                              |      | 48.8                    |                              |      | 48.8             |        |      | ns   |

| t <sub>SCLKR</sub> , t <sub>SCLKF</sub> | SCLK Rise/Fall times                   |                  | 5                            | 12.5 |                         | 5                            | 12.5 |                  | 5      | 12.5 | ns   |

| t <sub>DF</sub> , t <sub>DR</sub>       | DOUT rise/fall times                   |                  | 5                            | 12.5 |                         | 5                            | 12.5 |                  | 5      | 12.5 | ns   |

| t <sub>SFS</sub>                        | CS high after SCLK edge                | 5                |                              |      | 5                       |                              |      | 5                |        |      | ns   |

<sup>1</sup>Guaranteed by design, not tested.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Tuble 5.                            |                                |

|-------------------------------------|--------------------------------|

| Parameter                           | Rating                         |

| Acceleration                        |                                |

| Any Axis, Unpowered                 | 2000 g                         |

| Any Axis, Powered                   | 2000 g                         |

| VCC to GND                          | –0.3 V to +6.0 V               |

| Digital Input/Output Voltage to GND | –0.3 V to +5.3 V               |

| Analog Inputs to GND                | –0.3 V to +3.6 V               |

| Operating Temperature Range         | –40°C to +85°C                 |

| Storage Temperature Range           | -65°C to +125°C <sup>1,2</sup> |

<sup>1</sup>Extended exposure to temperatures outside the specified temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C can adversely affect the accuracy of the factory calibration. For best accuracy, store the parts within the specified operating range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

<sup>2</sup> Although the device is capable of withstanding short-term exposure to 150°C, long-term exposure threatens internal mechanical integrity.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Table 4. Package Characteristics

| Package Type   | θ <sub>JA</sub> | θ <sub>JC</sub> | Device Weight |

|----------------|-----------------|-----------------|---------------|

| 24-Lead Module | 39.8°C/W        | 14.2°C/W        | 16 grams      |

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

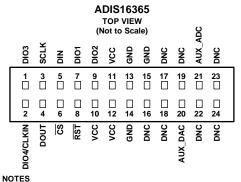

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

1. CONNECTOR PINS ARE NOT VISIBLE FROM THE TOP VIEW. 2. THIS REPRESENTATION DISPLAYS THE TOP VIEW PINOUT

FOR THE MATING SOCKET CONNECTOR. 3. DNC = DO NOT CONNECT.

07570-005

Figure 5. Pin Configuration

### **Table 5. Pin Function Descriptions**

| Pin No.                    | Mnemonic   | Type <sup>1</sup> | Description                                      |

|----------------------------|------------|-------------------|--------------------------------------------------|

| 1                          | DIO3       | I/O               | Configurable Digital Input/Output                |

| 2                          | DIO4/CLKIN | I/O               | Configurable Digital Input/Output or Clock Input |

| 16, 17, 18, 19, 22, 23, 24 | DNC        | N/A               | Do Not Connect                                   |

| 3                          | SCLK       | 1                 | SPI Serial Clock                                 |

| 4                          | DOUT       | 0                 | SPI Data Output                                  |

| 5                          | DIN        | 1                 | SPI Data Input                                   |

| б                          | CS         | 1                 | SPI Chip Select                                  |

| 7                          | DIO1       | I/O               | Configurable Digital Input/Output                |

| 8                          | RST        | 1                 | Reset                                            |

| 9                          | DIO2       | I/O               | Configurable Digital Input/Output                |

| 10, 11, 12                 | VCC        | S                 | Power Supply                                     |

| 13, 14, 15                 | GND        | S                 | Power Ground                                     |

| 20                         | AUX_DAC    | 0                 | Auxiliary, 12-Bit, DAC Output                    |

| 21                         | AUX_ADC    | I                 | Auxiliary, 12-Bit, ADC Input                     |

$^{1}$  S = supply, O = output, I = input.

Figure 6. Pin Configuration, Connector Top View

# **TYPICAL PERFORMANCE CHARACTERISTICS**

ADIS16365

Figure 12.

Figure 9.

# **BASIC OPERATION**

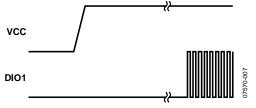

The ADIS16365 runs off an internal clock and requires no external initialization. Once the power supply reaches 4.75 V, the ADIS16365 executes an internal initialization sequence and then starts producing data. At this point, the DIO1 will start pulsing as well, repeating each time new data loads into the output registers. This data-ready signal serves as an interrupt service signal, telling the system processor that the device is awake and producing data.

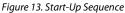

# **PHYSICAL INSTALLATION**

The ADIS16365 provides slots on each side for attachment. These slots accommodate either 2-56 or 2 mm machine screws. Attach the body of the ADIS16365 to the proper surface prior to inserting the electrical connector, which is located at the end of the flex.

Figure 14. Typical Hole Pattern for the ADIS16365 Attachment

# **INITIAL HOOK-UP AND CONFIGURATION**

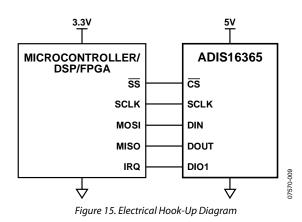

The electrical connection uses a 24-pin header that mates to either the CLM or MLE family of connectors from Samtec. The evaluation system for this product uses Samtec part number: CLM-112-02-LM-D-A. Samtec is the appropriate source for suggested pad layout geometries for this mating connector. Although this device runs off a +5 V power supply, the digital lines are compatible with +3.3 V-digital I/O systems.

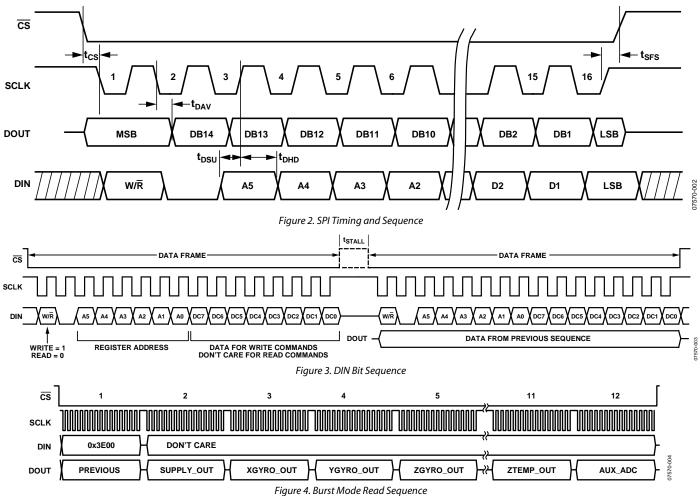

All of the output data and configuration options have 16-bit registers assigned to govern their operation. Each byte has its own unique 6-bit address, which provides user access using the serial peripheral interface (SPI). While SPI is a common digital interface, most digital processor platforms accommodate several configuration options. The parameters listed in Table 6 are configuration options that SPI-compatible digital processor platforms offer in configuration registers. This table is a guide for determining how to configure them for communication with the ADIS16365.

| Table 6. Typica | l Processor S | <b>PI Configuration</b> | Settings |

|-----------------|---------------|-------------------------|----------|

|-----------------|---------------|-------------------------|----------|

| Processor Setting                           | Notes                                                                                                                         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Master                                      | The ADIS16365 operates as a slave.                                                                                            |

| SCLK Rate <u>&lt;</u> 2MHz<br>(See Table 2) | Derived from a master clock, which is divided down to meet this requirement.                                                  |

| CPOL = 1                                    | Clock polarity.                                                                                                               |

| CPHA = 1                                    | Clock phase.                                                                                                                  |

| MSB-first                                   | Bit sequence.                                                                                                                 |

| 16-bit data cycles                          | For an 8-bit processor, this requires two<br>back-to-back 8-bit spi_read commands,<br>while keeping the chip-select line low. |

# DATA COLLECTION

The ADIS16365 produces data outputs in 16-bit segments, based on the previous 16-bit configuration sequence. The bit assignments for the configuration sequence are in Figure 3. For a read command, only the first eight bits require definition. The first two bits are zero, and the next six bits represent the register's lower byte, listed in Table 7. When using 8-bit microcontrollers, use two back-to-back SPI read calls, while keeping the chip select line low. A typical code example for an 8-bit microcontroller may look like the following:

```

Chip_Select = 0;

high_byte = spi_read(0x06);

low_byte = spi_read(0x00);

Chip_Select = 1;

delay 0.01ms (stall time)

```

# **DEVICE CONFIGURATION**

The ADIS16365 SPI provides device configuration control as well, eight bits at a time. Each function has a configurable register, which governs its operation, as listed in Table 7. In Figure 3, the first byte contains the write bit and register address. For example, the first byte of a write to the SMPL\_PRD is 0x80 (write bit high) plus 0x36 (low-byte address), which is 0xB6. The second byte of the DIN sequence contains the data, which loads into the specified location. For the lowest sample rate setting, 0xFF is the code. The entire DIN sequence for setting the slowest sample rate is 0xB6FF.

Many of the configuration registers have also been assigned mirror locations in the flash memory, which effectively provides them with a backup storage function. To assure the backup of these registers, the COMMAND register provides an initiation bit for manual flash updates. The ENDURANCE register provides a running count of these events.

# **BURST MODE DATA COLLECTION**

Burst mode data collection offers a more process-efficient method for collecting data from the ADIS16365. In 12 sequential data cycles, separated by only one SCLK time period, all 11output registers clock out on DOUT. In Figure 4, this sequence starts when the DIN sequence is 0x3E00. After that, the contents of each output register, comes out of DOUT, starting with SUPPLY\_OUT and ending with AUX\_ADC. The addressing sequence determines the order of the outputs in burst mode.

| Name       | R/W | Flash Backup | Address | Size (Bytes) | Function                                 | Reference |

|------------|-----|--------------|---------|--------------|------------------------------------------|-----------|

| ENDURANCE  | R   | Yes          | 0x00    | 2            | Flash memory write count                 |           |

| SUPPLY_OUT | R   | No           | 0x02    | 2            | Power supply measurement                 | Table 8   |

| XGYRO_OUT  | R   | No           | 0x04    | 2            | X-axis gyroscope output                  | Table 8   |

| YGYRO_OUT  | R   | No           | 0x06    | 2            | Y-axis gyroscope output                  | Table 8   |

| ZGYRO_OUT  | R   | No           | 0x08    | 2            | Z-axis gyroscope output                  | Table 8   |

| XACCL_OUT  | R   | No           | 0x0A    | 2            | X-axis accelerometer output              | Table 8   |

| YACCL_OUT  | R   | No           | 0x0C    | 2            | Y-axis accelerometer output              | Table 8   |

| ZACCL_OUT  | R   | No           | 0x0E    | 2            | Z-axis accelerometer output              | Table 8   |

| XTEMP_OUT  | R   | No           | 0x10    | 2            | X-axis gyroscope temperature measurement | Table 8   |

| YTEMP_OUT  | R   | No           | 0x12    | 2            | Y-axis gyroscope temperature measurement | Table 8   |

| ZTEMP_OUT  | R   | No           | 0x14    | 2            | Z-axis gyroscope temperature measurement | Table 8   |

| AUX_ADC    | R   | No           | 0x16    | 2            | Auxiliary ADC output                     | Table 8   |

|            |     |              | 0x18    | 2            | Reserved                                 |           |

| XGYRO_OFF  | R/W | Yes          | 0x1A    | 2            | X-axis gyroscope bias offset factor      | Table 9   |

| YGYRO_OFF  | R/W | Yes          | 0x1C    | 2            | Y-axis gyroscope bias offset factor      | Table 9   |

| ZGYRO_OFF  | R/W | Yes          | 0x1E    | 2            | Z-axis gyroscope bias offset factor      | Table 9   |

| XACCL_OFF  | R/W | Yes          | 0x20    | 2            | X-axis acceleration bias offset factor   | Table 10  |

| YACCL_OFF  | R/W | Yes          | 0x22    | 2            | Y-axis acceleration bias offset factor   | Table 10  |

| ZACCL_OFF  | R/W | Yes          | 0x24    | 2            | Z-axis acceleration bias offset factor   | Table 10  |

| ALM_MAG1   | R/W | Yes          | 0x26    | 2            | Alarm 1 amplitude threshold              | Table 19  |

| ALM_MAG2   | R/W | Yes          | 0x28    | 2            | Alarm 2 amplitude threshold              | Table 19  |

| ALM_SMPL1  | R/W | Yes          | 0x2A    | 2            | Alarm 1 sample size                      | Table 20  |

| ALM_SMPL2  | R/W | Yes          | 0x2C    | 2            | Alarm 2 sample size                      | Table 20  |

| ALM_CTRL   | R/W | Yes          | 0x2E    | 2            | Alarm control                            | Table 21  |

| AUX_DAC    | R/W | No           | 0x30    | 2            | Auxiliary DAC data                       | Table 16  |

| GPIO_CTRL  | R/W | No           | 0x32    | 2            | Auxiliary digital input/output control   | Table 18  |

| MSC_CTRL   | R/W | Yes          | 0x34    | 2            | Miscellaneous control                    | Table 17  |

| SMPL_PRD   | R/W | Yes          | 0x36    | 2            | Internal sample period (rate) control    | Table 13  |

| SENS/AVG   | R/W | Yes          | 0x38    | 2            | Dynamic range/digital filter control     | Table 15  |

| SLP_CNT    | R/W | No           | 0x3A    | 2            | Sleep mode control                       | Table 14  |

| STATUS     | R   | No           | 0x3C    | 2            | System status                            | Table 22  |

| COMMAND    | R/W | N/A          | 0x3E    | 2            | System command                           | Table 12  |

Table 7. User Register Map

# **OUTPUT DATA REGISTERS**

Table 8 provides the data configuration for each output data register in the ADIS16365. Starting with the MSB of the upper byte, each output data register has the following bit sequence: new data (ND) flag, error/alarm (EA) flag, followed by 14 data bits. The data bits are LSB-justified and, in the case of the 12-bit data formats, the remaining two bits are not used. The ND flag indicates that unread data resides in the output data registers. This flag clears and returns to 0 during an output register read sequence. It returns to 1 after the next internal sample update cycle completes. The EA flag indicates an error condition. The STATUS register contains all of the error flags and provides the ability to investigate the root cause.

#### **Table 8. Output Data Register Formats**

| 1 0                     |      |                       |                 |  |

|-------------------------|------|-----------------------|-----------------|--|

| Register                | Bits | Format                | Scale           |  |

| SUPPLY_OUT <sup>1</sup> | 12   | Binary, $+5V = 0x$    | 2.418 mV        |  |

| XGYRO_OUT <sup>2</sup>  | 14   | Twos complement       | 0.05°/sec       |  |

| YGYRO_OUT <sup>2</sup>  | 14   | Twos complement       | 0.05°/sec       |  |

| ZGYRO_OUT <sup>2</sup>  | 14   | Twos complement       | 0.05°/sec       |  |

| XACCL_OUT               | 14   | Twos complement       | 3.33 m <i>g</i> |  |

| YACCL_OUT               | 14   | Twos complement       | 3.33 m <i>g</i> |  |

| ZACCL_OUT               | 14   | Twos complement       | 3.33 m <i>g</i> |  |

| XTEMP_OUT <sup>3</sup>  | 12   | Binary, 25°C = 0x04FE | 0.1453°C        |  |

| YTEMP_OUT <sup>3</sup>  | 12   | Binary, 25°C = 0x04FE | 0.1453°C        |  |

| ZTEMP_OUT <sup>3</sup>  | 12   | Binary, 25°C = 0x04FE | 0.1453°C        |  |

| AUX_ADC                 | 12   | Binary = 0x04FE       | 0.8059 mV       |  |

| 151/ 2720100 (          | · 1) | •                     |                 |  |

<sup>1</sup> 5 V = 2730 LSBs (nominal).

$^2$  Assumes that the scaling is set to 300°/sec. This factor scales with the range.  $^3$  Typical condition, 25°C = 0 LSB.

# CALIBRATION

### **Manual Bias Calibration**

The bias offset registers in Table 9 and Table 10 provide a manual adjustment function for each sensor's output. For example, if an output offset of  $0.125^{\circ}$ /sec is observed in the Z-axis gyroscope, the ZGYRO\_OFF register provides the calibration factor necessary to improve the accuracy. Using the sensitivity of  $0.0125^{\circ}$ /sec, an adjustment of -10 LSBs is required. The twos complement, hexadecimal code of -10 LSBs is 0x1FF6. See Table 11 for the DIN command.

#### Table 9. X,Y,ZGYRO\_OFF Register Bits

| Bits    | Description | (Default = 0x0000)                                                                                              |  |

|---------|-------------|-----------------------------------------------------------------------------------------------------------------|--|

| [15:13] | Not used.   |                                                                                                                 |  |

| [12:0]  |             | Data bits. Twos complement, $0.0125^{\circ}$ /sec per LSB.<br>Typical adjustment range = $\pm 50^{\circ}$ /sec. |  |

#### Table 10. X,Y,ZACCL\_OFF Register Bits

| Bits    | Description                            | (Default = 0x0000) |

|---------|----------------------------------------|--------------------|

| [15:12] | Not used.                              |                    |

| [11:0]  | Data bits, Twos complement 3.3 mg/LSB. |                    |

|         | Typical adjustment range = $\pm 6 g$ . |                    |

### Automatic Bias Null Calibration

This single-command calibration function is in the COMMAND register and measures all three-gyroscope output registers, then loads the three bias correction registers with values that return their outputs to zero (null). See Table 11 for the DIN command.

### Precision Automatic Bias Null Calibration

This single-command calibration function is in the COMMAND register and incorporates a 30-second average of all three gyroscope output registers, then loads the three bias correction registers with values that return their outputs to zero (null). For optimal calibration accuracy, the device should be stable (no motion) for this entire period. Once it has started, a reset is the only way to stop it prematurely, if required. See Table 11 for the DIN command.

### **Restoring Factory Calibration**

This single command is in the COMMAND register and restores the factory calibration by writing 0x0000 into each bias offset register listed in Table 9 and Table 10. This command also flushes all of the data from the digital filter taps. See Table 11 for the DIN command.

#### Linear Acceleration Bias Compensation (Gyroscopes)

This function enables compensation for low-frequency acceleration influences on gyroscope bias behavior, using the MSC\_CTRL register. See Table 11 for the DIN command.

#### **Linear Acceleration Origin Alignment**

This function enables origin alignment for the accelerometers to the point of percussion (see Figure 6), using the MSC\_CTRL register. See Table 11 for the DIN command.

#### Table 11. Calibration Commands

| Tuble II. Cultifution Communes               |             |

|----------------------------------------------|-------------|

| Calibration Function                         | DIN Word(s) |

| Adjust Z-Axis Gyroscope Bias by -0.125°/sec: | 0x9E1F      |

| Write 0x1F to 0x1F                           | 0x9FF6      |

| Write 0xF6 to 0x1E (ZGYRO_OFF)               |             |

| Automatic Bias Null:                         | 0xBE01      |

| Write 0x01 to 0x3E (COMMAND)                 |             |

| Precision Automatic Bias Null:               | 0xBE10      |

| Write 0x10 to 0x3E (COMMAND)                 |             |

| Factory Calibration Restore:                 | 0xBE02      |

| Write 0x02 to 0x3E (COMMAND)                 |             |

| Enable Linear Acceleration Bias              | 0xB486      |

| Compensation for the Gyroscopes:             |             |

| Write 0x86 to 0x34 (MSC_CTRL)                |             |

| Enable Origin Alignment for the              | 0xB446      |

| Accelerometer Sensors:                       |             |

| Write 0x46 to 0x34 (MSC_CTRL)                |             |

The last two entries assume factory default conditions for the MSC\_CTRL register. The contents may vary, depending on the other MSC\_CTRL settings. See Table 17 for further description of each bit in this register.

### **OPERATION CONTROL REGISTERS** *Global Commands*

In addition to the calibration commands, the COMMAND register provides initiation bits for several other common functions. Writing a 1 to the assigned COMMAND bit exercises its function.

#### Table 12. COMMAND Bit Descriptions

| Not used<br>Software reset command<br>Not used |

|------------------------------------------------|

|                                                |

| Not used                                       |

|                                                |

| Precision autonull command                     |

| -lash update command                           |

| Auxiliary DAC data latch                       |

| Factory calibration restore command            |

| Autonull command                               |

| = ;<br>4u<br>=a                                |

The software reset command restarts the internal processor, which loads all registers with the contents in their flash memory locations.

The flash update copies the contents of all flash backup registers into their assigned, nonvolatile, flash memory locations. This process takes approximately 50 ms and requires a power supply that is within the specified operating range. After waiting the appropriate time for the flash update to complete, verify successful completion by reading the STATUS register. If the flash update is successful, the flash update error is 0. If the flash update is not successful, reading this error bit accomplishes two things: (1) alerting the system processor to try again, and (2) clearing the error flag, which is required for flash memory access.

The DAC data latch command loads the contents of AUX\_DAC into the DAC latches. Because the AUX\_DAC contents must be updated one byte at a time, this command ensures a stable DAC output voltage during updates.

Finally, reading the COMMAND register (see

Figure 4) starts the burst mode read sequence.

### Internal Sample Rate

The SMPL\_PRD register controls the ADIS16365 internal sample rate and has two parts: a selectable time base and a multiplier. The following relationship produces the sample rate:

$$t_S = t_B \times N_S + 1$$

| Bit    | Description                              | (Default = 0x0001) |

|--------|------------------------------------------|--------------------|

| [15:8] | Not used                                 |                    |

| [7]    | Time base, 0 = 0.61035 ms, 1 = 18.921 ms |                    |

| [6:0]  | Increment setting (Ns)                   |                    |

An example calculation of the default sample period follows:

$$SMPL_PRD = 0x03, B7 - B0 = 00000011 ->$$

$B7 = 0 \Rightarrow t_B = 0.61035 \text{ ms}, B6...B0 = 000000011 \Rightarrow N_S = 3$

$t_S = t_B \times (N_S + 1) = 0.61035 \text{ ms} \times (3+1) = 2.4414 \text{ ms}$

The contents of this register determine whether the device is in fast mode or low power mode." Fast mode occurs when the contents of SMPL\_PRD are less than 0x0A. Refer to Table 1 and Table 2 for the performance trade-offs associated with each mode. Setting SMPL\_PRD = 0x000 activates the external clock.

#### **Power Management**

In addition to offering two different performance modes for power optimization, the ADIS16365 offers a programmable shutdown period that the SLP\_CNT register controls.

#### Table 14. SLP\_CNT Bit Descriptions

| Bit    | Description                       | (Default = 0x0000)  |

|--------|-----------------------------------|---------------------|

| [15:8] | Not used                          |                     |

| [7:0]  | Data bits, 0.5 seconds/LSB (0x08, | sleep time = 4 sec) |

Once in sleep mode, a reset or power cycle is required to wake up.

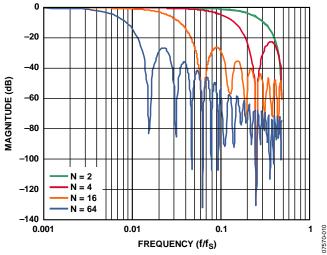

### **Digital Filtering**

The signal conditioning circuit of each sensor has an analog bandwidth of approximately 350 Hz. A programmable-length Bartlett window FIR filter provides opportunity for additional noise reduction on all output data registers. The SENS/AVG register controls the number of taps in power-of-two step sizes, from zero to six.

Filter setup requires one simple step: write the appropriate M factor to the assigned bits in the SENS/AVG register. The bit assignments are listed in Table 15. The frequency response relationship for this filter is

$$H_B(f) = H_A^2(f) \quad H_A(f) = \frac{\sin(\pi \times N \times f \times t_s)}{N \times \sin(\pi \times f \times t_s)}$$

Figure 16. Bartlett Window FIR Frequency Response

# Dynamic Range

There are three dynamic range settings:  $\pm 75^{\circ}/\text{sec}$ ,  $\pm 150^{\circ}/\text{sec}$ , and  $\pm 300^{\circ}/\text{sec}$ . The lower dynamic range settings (75, 150) limit the minimum filter tap sizes to maintain the resolution as the measurement range decreases. The recommended order for programming the SENS/AVG register is upper byte (sensitivity), followed by lower byte (filtering). The contents of the SENS/AVG register are nonvolatile.

### Table 15. SENS/AVG Bit Descriptions

| Value | Description                               | (Default = 0x0000)                                                                                                                  |

|-------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|       | Not used                                  |                                                                                                                                     |

|       | Measurement range (sensitivity) selection |                                                                                                                                     |

| 100   | 300°/sec (default co                      | ndition)                                                                                                                            |

| 010   | 150°/sec, filter taps                     | $\geq$ 4 (Bits[2:0] $\geq$ 0x02)                                                                                                    |

| 001   | 75°/sec, filter taps ≥                    | 16 (Bits[2:0] ≥ 0x04)                                                                                                               |

|       | Not used                                  |                                                                                                                                     |

|       |                                           | imber of taps, N = $2^{M}$ ;<br>= $2^{3}$ = 8 taps                                                                                  |

|       | 100<br>010                                | Not used       100     300°/sec (default co       010     150°/sec, filter taps       001     75°/sec, filter taps ≥       Not used |

# **INPUT/OUTPUT FUNCTIONS**

The ADIS16365 provides several input/output functions, including a 12-bit ADC, a 12-bit DAC, and four general purpose, digital input/output lines that have several configuration options.

### **Auxiliary ADC**

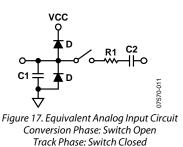

The auxiliary ADC is a standard 12-bit ADC that digitizes other system-level analog signals. The output of the ADC can be monitored through the AUX\_ADC register, as defined in Table 8. The ADC is a 12-bit successive approximation converter. The output data is presented in straight binary format with the fullscale range extending from 0 V to 3.3 V.

Figure 17 shows the equivalent circuit of the analog input structure of the ADC. The input capacitor (C1) is typically 4 pF and can be attributed to parasitic package capacitance. The two diodes provide ESD protection for the analog input. Care must be taken to ensure that the analog input signals are never outside the range of -0.3 V to +3.5 V. Signals outside this range cause the diodes to become forward-biased and to start conducting.

The diodes can handle 10 mA without causing irreversible damage. The resistor is a lumped component that represents the on resistance of the switches. The value of this resistance is typically 100  $\Omega$ . Capacitor C2 represents the ADC sampling capacitor and is typically 16 pF.

For ac applications, it is recommended that high frequency components from the analog input signal be removed by using a low-pass filter on the analog input pin.

In applications where harmonic distortion and signal-to-noise ratios are critical, the analog input must be driven from a low impedance source. Large source impedances significantly affect the ac performance of the ADC. This can necessitate the use of an input buffer amplifier. When no input amplifier is used to drive the analog input, the source impedance should be limited to values lower than 1 k $\Omega$ .

### **Auxiliary DAC**

The auxiliary DAC provides a 12-bit level adjustment function. The AUX\_DAC register controls the operation of the auxiliary DAC function, which is useful for systems that require analog level controls. It offers a rail-to-rail buffered output that has a range of 0 V to 3.3 V. The DAC can drive its output to within 5 mV of the ground reference when it is not sinking current. As the output approaches ground, the linearity begins to degrade (100 LSB beginning point). As the sink current increases, the nonlinear range increases. The DAC output latch function, contained in the COMMAND register, provides continuous operation while writing to each byte of this register. The contents of this register are volatile, which means that the desired output level must be set after every reset and power cycle event.

Table 16. AUX\_DAC Bit Descriptions

| Bit     | Description                                                                     | (Default = 0x0000) |

|---------|---------------------------------------------------------------------------------|--------------------|

| [15:12] | Not used                                                                        |                    |

| [11:0]  | Data bits, scale factor = 0.8059 mV/code<br>Offset binary format, 0 V = 0 codes |                    |

|         | Offset binary format,                                                           | 0 V = 0  codes     |

#### Data-Ready I/O Indicator

The MSC\_CTRL register provides controls for a data-ready function. For example, writing 0x05 to this register enables this function and establishes DIO2 as an active-low, data-ready line. The duty cycle is 25% ( $\pm 10\%$  tolerance).

#### Table 17. MSC\_CTRL Bit Descriptions

| Bits    | Description (Default = 0x0000)                       |

|---------|------------------------------------------------------|

|         | -                                                    |

| [15:12] | Not used                                             |

| [11]    | Flash test                                           |

| [10]    | Internal self-test enable (clears on completion)     |

|         | 1 = enabled, 0 = disabled                            |

| [9]     | Manual self-test, negative stimulus                  |

|         | 1 = enabled, 0 = disabled                            |

| [8]     | Manual self-test, positive stimulus                  |

|         | 1 = enabled, 0 = disabled                            |

| [7]     | Linear acceleration bias compensation for gyroscopes |

|         | 1 = enabled, 0 = disabled                            |

| [6]     | Linear accelerometer origin alignment                |

|         | 1 = enabled, 0 = disabled                            |

| [5:3]   | Not used                                             |

| [2]     | Data-ready enable, 1 = enabled, 0 = disabled         |

| [1]     | Data-ready polarity, 1 = active high, 0 = active low |

| [0]     | Data-ready line select, 1 = DIO2, 0 = DIO1           |

### General Purpose I/O

The GPIO\_CTRL register controls the direction and data of the general-purpose digital lines, DIO1 through DIO4. For example, writing a 0x02 to the GPIO\_CTRL register sets DIO2 as an output line and DIO1, DIO3, and DIO4 as input lines. Reading the data bits in GPIO\_CTRL reveals the logic level of each line.

#### Table 18. GPIO\_CTRL Bit Descriptions

| Bit     | Description (Default = 0x0000)                     |

|---------|----------------------------------------------------|

| [15:12] | Not used                                           |

| [11]    | General-Purpose I/O Line 4 data level              |

| [10]    | General-Purpose I/O Line 3 data level              |

| [9]     | General-Purpose I/O Line 2 data level              |

| [8]     | General-Purpose I/O Line 1 data level              |

| [7:4]   | Not used                                           |

| [3]     | General-Purpose I/O Line 4, data direction control |

|         | 1 = output, 0 = input                              |

| [2]     | General-Purpose I/O Line 3, data direction control |

|         | 1 = output, 0 = input                              |

| [1]     | General-Purpose I/O Line 2, data direction control |

|         | 1 = output, 0 = input                              |

| [0]     | General-Purpose I/O Line 1, data direction control |

|         | 1 = output, 0 = input                              |

# DIAGNOSTICS

#### Self-Test

Self-test exercises the mechanical structure of the sensor and provides a simple method for verifying the operation of the entire sensor signal conditioning circuit. There are two different self-test options: startup and manual. If either of these self-tests results in a failure, the self-test error flag, located in the STATUS register, sets to 1. The manual self-test option results in a repeating pattern, until the bit is set back to 0. While in the manual self-test loop, SMPL\_PRD and AVG\_CNT cannot be changed. See Table 17 for the appropriate MSC\_CTRL bit designations.

### Alarm Registers

The alarm function provides monitoring for two independent conditions. The ALM\_CTRL register provides control inputs for data source, data filtering (prior to comparison), static/ dynamic, and output indicator configurations. The ALM\_MAGx registers establish the trigger threshold and polarity configurations. The ALM\_SMPLx registers provide the numbers of samples to use in the dynamic, rate-of-change configuration. The rate-of-change calculation is

$$Y_C = \frac{1}{N_{DS}} \sum_{n=1}^{N_{DS}} y(n+1) - y(n) \Rightarrow Alarm \Rightarrow \text{is } Y_C > \text{or} < M_C ?$$

where:

$N_{DS}$  is the number of samples in ALM\_SMPLx. y(n) is the sampled output data.  $M_C$  is the magnitude for comparison in ALM\_MAGx. > or < is determined by the MSB in ALM\_MAGx.

#### Table 19. ALM\_MAG1/ALM\_MAG2 Bit Designations

| Bit    | Description             | (Default = 0x0000)             |

|--------|-------------------------|--------------------------------|

| [15]   | Comparison polarity: 1  | = greater than, 0 = less than  |

| [14]   | Not used                |                                |

| [13:0] | Data bits, matches form | at of trigger source selection |

#### Table 20. ALM\_SMPL1/ALM\_SMPL2 Bit Designations

| Bit    | Description            | (Default = 0x0001)                   |

|--------|------------------------|--------------------------------------|

| [15:8] | Not used               |                                      |

| [7:0]  | Data bits: number of s | amples (both $0x00$ and $0x01 = 1$ ) |

### Table 21. ALM\_CTRL Bit Designations

| Bits                   | Value       | Description (Default = 0x0000)                      |

|------------------------|-------------|-----------------------------------------------------|

| [15:12]                |             | Alarm 2 source selection                            |

|                        | 0000        | Disable                                             |

|                        | 0001        | Power supply output                                 |

|                        | 0010        | X-axis gyroscope output                             |

|                        | 0011        | Y-axis gyroscope output                             |

|                        | 0100        | Z-axis gyroscope output                             |

|                        | 0101        | X-axis accelerometer output                         |

|                        | 0110        | Y-axis accelerometer output                         |

|                        | 0111        | Z-axis accelerometer output                         |

|                        | 1000        | X-axis gyroscope temperature output                 |

|                        | 1001        | Y-axis gyroscope temperature output                 |

|                        | 1010        | Z-axis gyroscope temperature output                 |

|                        | 1011        | Auxiliary ADC input                                 |

| [11:8]                 |             | Alarm 1 source selection (same as Alarm 2)          |

| [7]                    |             | Rate of change (ROC) enable for Alarm 2             |

|                        |             | 1 = rate of change, 0 = static level                |

| [6]                    |             | Rate of change (ROC) enable for Alarm 1             |

|                        |             | 1 = rate of change, 0 = static level                |

| [5]                    |             | Not used                                            |

| [4]                    |             | Comparison data filter setting <sup>1</sup>         |

| [3]                    |             | 1 = filtered data, 0 = unfiltered data<br>Not used  |

| [5]                    |             |                                                     |

| [2]                    |             | Alarm output enable<br>1 = enabled, 0 = disabled    |

| [1]                    |             | Alarm output polarity                               |

| [0]                    |             | 1 = active high, $0 = $ active low                  |

| [0]                    |             | Alarm output line select<br>1 = DIO2, 0 = DIO1      |

| <sup>1</sup> Incline a | nd vertical | angles always use filtered data in this comparison. |

## Status

The STATUS register provides a series of error flags that provide indicator functions for common system-level issues. All of the flags clear (set to 0) after each STATUS register read cycle. If an error condition remains, the error flag returns to 1 during the next sample cycle.

## Table 22. STATUS Bit Descriptions

| Bit     | Description                     | (Default = 0x0000) |  |

|---------|---------------------------------|--------------------|--|

| [15:10] | Not used                        |                    |  |

| [9]     | Alarm 2 status                  |                    |  |

|         | 1 = active, 0 = inactive        |                    |  |

| [8]     | Alarm 1 status                  |                    |  |

|         | 1 = active, 0 = inactive        |                    |  |

| [7]     | Not used                        |                    |  |

| [6]     | Flash failure                   |                    |  |

| [5]     | Self-test diagnostic error flag |                    |  |

|         | 1 = error condition, 0 = 1      | normal operation   |  |

| [4]     | Not used                        |                    |  |

| [3]     | SPI communications failure      | e                  |  |

|         | 1 = error condition, 0 = 1      | normal operation   |  |

| [2]     | Flash update failed             |                    |  |

|         | 1 = error condition, 0 = 1      | normal operation   |  |

| [1]     | Power supply above 5.25 V       | 1                  |  |

|         | 1 ≥ 5.25 V, 0 ≤ 5.25 V (no      | ormal)             |  |

| [0]     | Power supply below 4.75 V       | /                  |  |

|         | 1 ≤ 4.75 V, 0 ≥ 4.75 V (no      | ormal)             |  |

<sup>1</sup> Incline and vertical angles always use filtered data in this comparison.

011108-C

# **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model                       | Temperature Range | Package Description                     | Package Option |

|-----------------------------|-------------------|-----------------------------------------|----------------|

| ADIS16365BMLZ <sup>1</sup>  | -40°C to +105°C   | 24-Lead Module with Connector Interface | ML-24-2        |

| ADIS16365/PCBZ <sup>1</sup> |                   | Interface Board                         |                |

$^{1}$  Z = RoHS Compliant Part.

# NOTES

# NOTES

# NOTES

Rev. PrA | Page 20 of 20

www.analog.com

©2008 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. PR07570-0-6/08(PrA)