# **GSM Power Management System**

# ADP3408

#### FEATURES

Handles all GSM Baseband Power Management Six LDOs Optimized for Specific GSM Subsystems Li-lon and NiMH Battery Charge Function Optimized for the AD20msp430 Baseband Chipset

APPLICATIONS GSM/DCS/PCS/CDMA Handsets

#### **GENERAL DESCRIPTION**

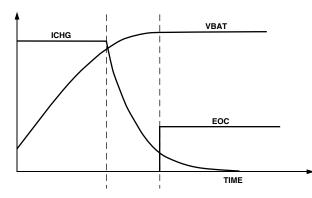

The ADP3408 is a multifunction power system chip optimized for GSM handsets, especially those based on the Analog Devices AD20msp430 system solution. It contains six LDOs, one to power each of the critical GSM sub-blocks. Sophisticated controls are available for power-up during battery charging, keypad interface, and RTC alarm. The charge circuit maintains low current charging during the initial charge phase and provides an end-of-charge signal when a Li-Ion battery is being charged.

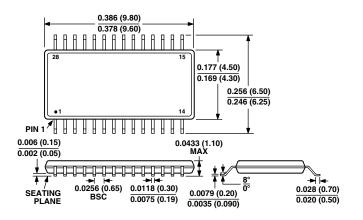

The ADP3408 is specified over the temperature range of  $-20^{\circ}$ C to  $+85^{\circ}$ C and is available in narrow body TSSOP-28 pin package.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2001

$\label{eq:added} \begin{array}{l} \textbf{ADP3408} - \textbf{SPECIFICATIONS}^1 \ (-20^\circ \texttt{C} \leq \texttt{T}_{\texttt{A}} \leq +85^\circ \texttt{C}, \ \texttt{VBAT} = \texttt{VBAT2} = \texttt{3} \ \texttt{V}-\texttt{5.5} \ \texttt{V}, \ \texttt{CVSIM} = \texttt{CVCORE} = \texttt{CVAN} = \texttt{CVMEM} = \texttt{2.2} \ \mu\texttt{F}, \ \texttt{VTCX0} = \texttt{0.22} \ \mu\texttt{F}, \ \texttt{CVRTC} = \texttt{0.1} \ \mu\texttt{F}, \ \texttt{CVBAT} = \texttt{10} \ \mu\texttt{F}, \ \texttt{minimum} \ \texttt{loads} \ \texttt{applied} \ \texttt{on} \ \texttt{all outputs}, \ \texttt{unless otherwise noted}. \end{aligned}$

| Parameter                                                                                                                                 | Symbol                                                      | Condition                                                                                                                                                        | Min            | Тур                    | Max               | Unit                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|-------------------|-----------------------------------------|

| SHUTDOWN SUPPLY CURRENT<br>VBAT ≤ 2.5 V                                                                                                   | ICC                                                         | VBAT = VBAT2 = 2.3 V                                                                                                                                             |                | 7                      | 20                | μΑ                                      |

| (Deep Discharged Lockout Active)<br>2.5 V < VBAT $\leq$ 3.2 V                                                                             |                                                             | VBAT = VBAT2 = 3.0 V                                                                                                                                             |                | 30                     | 55                | μΑ                                      |

| (UVLO Active)<br>VBAT > 3.2 V                                                                                                             |                                                             | VBAT = VBAT2 = 4.0 V                                                                                                                                             |                | 45                     | 80                | μΑ                                      |

| OPERATING GROUND CURRENT<br>VSIM, VCORE, VMEM, VRTC On<br>All LDOs On                                                                     | IGND                                                        | VBAT = 3.6 V<br>Minimum Loads<br>Minimum Loads<br>Maximum Loads                                                                                                  |                | 225<br>345<br>1.0      | 300<br>450<br>3.0 | μΑ<br>μΑ<br>% of max<br>load<br>current |

| UVLO ON THRESHOLD                                                                                                                         | VBAT                                                        |                                                                                                                                                                  |                | 3.2                    | 3.3               | v                                       |

| UVLO HYSTERESIS                                                                                                                           | VBAT                                                        |                                                                                                                                                                  |                | 200                    |                   | mV                                      |

| DEEP DISCHARGED LOCKOUT ON<br>THRESHOLD                                                                                                   | VBAT                                                        |                                                                                                                                                                  |                | 2.4                    | 2.75              | V                                       |

| DEEP DISCHARGED LOCKOUT<br>HYSTERESIS                                                                                                     | VBAT                                                        |                                                                                                                                                                  |                | 100                    |                   | mV                                      |

| INPUT HIGH VOLTAGE<br>(PWRONIN, TCXOEN, SIMEN,<br>CHGEN, GATEIN)                                                                          | V <sub>IH</sub>                                             |                                                                                                                                                                  | 2.0            |                        |                   | V                                       |

| INPUT LOW VOLTAGE<br>(PWRONIN, TCXOEN, SIMEN,<br>CHGEN, GATEIN)                                                                           | V <sub>IL</sub>                                             |                                                                                                                                                                  |                |                        | 0.4               | V                                       |

| INPUT HIGH BIAS CURRENT<br>(PWRONIN, TCXOEN, SIMEN,<br>CHGEN, GATEIN)                                                                     | I <sub>IH</sub>                                             |                                                                                                                                                                  |                |                        | 1.0               | μΑ                                      |

| INPUT LOW BIAS CURRENT<br>(PWRONIN, TCXOEN, SIMEN,<br>CHGEN, GATEIN)                                                                      | I <sub>IL</sub>                                             |                                                                                                                                                                  | -1.0           |                        |                   | μΑ                                      |

| PWRONKEY INPUT HIGH VOLTAGE                                                                                                               | V <sub>IH</sub>                                             |                                                                                                                                                                  | $0.7 \times V$ | BAT                    |                   | V                                       |

| PWRONKEY INPUT LOW VOLTAGE                                                                                                                | V <sub>IL</sub>                                             |                                                                                                                                                                  |                |                        | $0.3 \times VBAT$ | V                                       |

| PWRONKEY INPUT PULL-UP<br>RESISTANCE TO VBAT                                                                                              |                                                             |                                                                                                                                                                  | 70             | 100                    | 130               | kΩ                                      |

| THERMAL SHUTDOWN THRESHOLD <sup>2</sup>                                                                                                   |                                                             |                                                                                                                                                                  |                | 160                    |                   | °C                                      |

| THERMAL SHUTDOWN HYSTERESIS                                                                                                               |                                                             |                                                                                                                                                                  |                | 45                     |                   | °C                                      |

| ROWX CHARACTERISTICS<br>ROWX Output Low Voltage                                                                                           | V <sub>OL</sub>                                             | PWRONKEY = Low                                                                                                                                                   |                |                        | 0.4               | 17                                      |

| ROWX Output High Leakage<br>Current                                                                                                       | I <sub>IH</sub>                                             | $I_{OL} = 200 \ \mu A$<br>PWRONKEY = High<br>V(ROWX) = 5 V                                                                                                       |                |                        | 0.4<br>1          | V<br>μA                                 |

| SIM CARD LDO (VSIM)<br>Output Voltage<br>Line Regulation<br>Load Regulation<br>Output Capacitor Required for Stability<br>Dropout Voltage | VSIM<br>ΔVSIM<br>ΔVSIM<br>C <sub>o</sub><br>V <sub>Do</sub> | Line, Load, Temp<br>Min Load<br>50 $\mu$ A $\leq$ I <sub>LOAD</sub> $\leq$ 20 mA,<br>V <sub>BAT</sub> = 3.6 V<br>V <sub>O</sub> = V <sub>INITIAL</sub> - 100 mV, | 2.80<br>2.2    | 2.85<br>2<br>1         | 2.92              | V<br>mV<br>mV<br>µF                     |

| Dispont toninge                                                                                                                           | י טע                                                        | $I_{\text{LOAD}} = 20 \text{ mA}$                                                                                                                                |                | 35                     | 100               | mV                                      |

| DIGITAL CORE LDO (VCORE)<br>Output Voltage<br>ADP3408ARU-2.5<br>ADP3408ARU-1.8<br>Line Regulation<br>Load Regulation                      | VCORE<br>VCORE<br>ΔVCORE<br>ΔVCORE                          | Line, Load, Temp<br>Line, Load, Temp<br>Min Load<br>$50 \ \mu A \le I_{LOAD} \le 100 \ mA,$                                                                      | 2.40<br>1.75   | 2.45<br>1.80<br>2<br>7 | 2.50<br>1.85      | V<br>V<br>mV<br>mV                      |

| Output Capacitor Required for Stability                                                                                                   | Co                                                          | $V_{BAT} = 3.6 V$                                                                                                                                                | 2.2            |                        |                   | μF                                      |

| Parameter                                                   | Symbol                           | Condition                                                                           | Min                 | Тур          | Max         | Unit   |  |

|-------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------|---------------------|--------------|-------------|--------|--|

| RTC LDO<br>REAL-TIME CLOCK LDO/<br>COIN CELL CHARGER (VRTC) |                                  |                                                                                     |                     |              |             |        |  |

| Maximum Output Voltage                                      | UDTO                             |                                                                                     | 0.20                | 0.45         | 0.51        |        |  |

| ADP3408ARU-2.5<br>ADP3408ARU-1.8                            | VRTC<br>VRTC                     | $1 \ \mu A \leq I_{LOAD} \leq 10 \ \mu A$ $1 \ \mu A \leq I_{LOAD} \leq 10 \ \mu A$ | 2.39<br>1.80        | 2.45<br>1.95 | 2.51<br>2.1 | V<br>V |  |

| Off Reverse Input Current                                   | IL                               | $V_{BAT} = 2.15 \text{ V}, T_A = 25^{\circ}\text{C}$                                | 1.00                | 1.95         | 0.5         | μA     |  |

| Output Capacitor Required for Stability                     | C <sub>o</sub>                   |                                                                                     | 0.1                 |              | 0.5         | μF     |  |

| NALOG LDO (VAN)                                             |                                  |                                                                                     |                     |              |             |        |  |

| Output Voltage                                              | VAN                              | Line, Load, Temp                                                                    | 2.40                | 2.45         | 2.50        | V      |  |

| Line Regulation                                             | ΔVAN                             | Min Load                                                                            |                     | 2            |             | mV     |  |

| Load Regulation                                             | ΔVAN                             | 50 $\mu$ A $\leq$ I <sub>LOAD</sub> $\leq$ 130 mA,<br>V <sub>BAT</sub> = 3.6 V      |                     | 8            |             | mV     |  |

| Output Capacitor Required for Stability                     | Co                               | bitt                                                                                | 2.2                 |              |             | μF     |  |

| Ripple Rejection                                            | $\Delta VBAT/$                   | f = 217 Hz                                                                          | 65                  |              |             | dB     |  |

|                                                             | $\Delta VAN^3$                   | $V_{BAT} = 3.6 V$                                                                   |                     |              |             |        |  |

| Output Noise Voltage                                        | V <sub>NOISE</sub>               | f = 10 Hz to 100 kHz                                                                |                     | 80           |             | μV rms |  |

|                                                             |                                  | $I_{LOAD} = 130 \text{ mA}$ $V_{BAT} = 3.6 \text{ V}$                               |                     |              |             |        |  |

| CXO LDO (VTCXO)                                             |                                  |                                                                                     |                     |              |             |        |  |

| Output Voltage                                              | VTCXO                            | Line, Load, Temp                                                                    | 2.66                | 2.715        | 2.77        | V      |  |

| Line Regulation                                             | ΔΥΤΟΧΟ                           | Min Load                                                                            |                     | 2            |             | mV     |  |

| Load Regulation                                             | ΔVTCXO                           | 50 $\mu$ A $\leq$ I <sub>LOAD</sub> $\leq$ 20 mA,                                   |                     | 1            |             | mV     |  |

|                                                             |                                  | $V_{BAT} = 3.6 V$                                                                   |                     |              |             |        |  |

| Output Capacitor Required for Stability                     | Co                               |                                                                                     | 0.22                |              |             | μF     |  |

| Dropout Voltage                                             | V <sub>DO</sub>                  | $V_0 = V_{INITIAL} - 100 \text{ mV}$                                                |                     | 160          | 310         | mV     |  |

| Ripple Rejection                                            | $\Delta VBAT/$                   | $I_{LOAD} = 20 \text{ mA}$<br>f = 217 Hz                                            | 65                  |              |             | dB     |  |

|                                                             | ΔVTCXO                           | $V_{BAT} = 3.6 V$                                                                   |                     |              |             |        |  |

| Output Noise Voltage                                        | V <sub>NOISE</sub>               | f = 10 Hz to 100 kHz                                                                |                     | 80           |             | μV rms |  |

|                                                             |                                  | $I_{LOAD} = 20 \text{ mA},$<br>$V_{BAT} = 3.6 \text{ V}$                            |                     |              |             |        |  |

| MEMORY LDO (VMEM)                                           |                                  | VBAI 5.0 V                                                                          |                     |              |             |        |  |

| Output Voltage                                              | VMEM                             | Line, Load, Temp                                                                    | 2.744               | 2.80         | 2.856       | V      |  |

| Line Regulation                                             | ΔVMEM                            | Min Load                                                                            |                     | 2            | 2.030       | mV     |  |

| Load Regulation                                             | ΔVMEM                            | $50 \ \mu A < I_{LOAD} < 60 \ mA,$                                                  |                     | 3            |             | mV     |  |

| C .                                                         |                                  | $V_{BAT} = 3.6 V$                                                                   |                     |              |             | mV     |  |

| Output Capacitor Required for Stability                     | Co                               |                                                                                     | 2.2                 |              |             | μF     |  |

| Dropout Voltage                                             |                                  |                                                                                     |                     | 80           | 180         | mV     |  |

| EFOUT<br>Output Voltage                                     | VREFOUT                          | Line, Load, Temp                                                                    | 1.19                | 1.210        | 1.23        | v      |  |

| Line Regulation                                             | AVREFOUT                         | Min Load                                                                            | 1.19                | 0.2          | 1.25        | mV     |  |

| Load Regulation                                             | AVREFOUT                         | $0 \mu\text{A} < \text{I}_{\text{LOAD}} < 50 \mu\text{A}$                           |                     | 0.5          |             | mV     |  |

|                                                             |                                  | $V_{BAT} = 3.6 V$                                                                   |                     |              |             |        |  |

| Ripple Rejection                                            | $\Delta VBAT/$                   | f = 217  Hz                                                                         | 65                  | 75           |             | dB     |  |

|                                                             | ∆VREFOUT                         | $V_{BAT}$ = 3.6 V, $I_{LOAD}$ = 50 $\mu$ A                                          |                     |              |             |        |  |

| Maximum Capacitive Load                                     | Co                               |                                                                                     | 100                 |              |             | pF     |  |

| Output Noise Voltage                                        | V <sub>NOISE</sub>               | f = 10 Hz to 100 kHz,<br>$V_{BAT} = 3.6$ V                                          |                     | 40           |             | μV rms |  |

| ESET GENERATOR (RESET)                                      |                                  | 2.11                                                                                |                     |              |             |        |  |

| Output High Voltage                                         | V <sub>OH</sub>                  | I <sub>OH</sub> = 500 μA                                                            | V <sub>MEM</sub> -0 | ).25         |             | V      |  |

| Output Low Voltage                                          | V <sub>OL</sub>                  | $I_{OL} = -500 \ \mu A$                                                             |                     |              | 0.25        | V      |  |

| Output Current                                              | I <sub>OL</sub> /I <sub>OH</sub> | $V_{OL} = 0.25 V,$                                                                  |                     | 1            |             | mA     |  |

|                                                             | T                                | $V_{OH} = V_{MEM} - 0.25 V$                                                         |                     | 1.0          |             |        |  |

| Delay Time per Unit Capacitance<br>Applied to RESCAP Pin    | T <sub>D</sub>                   |                                                                                     | 0.6                 | 1.2          | 2.4         | ms/nF  |  |

| ATTERY VOLTAGE DIVIDER                                      |                                  |                                                                                     | 1                   |              |             |        |  |

| Divider Ratio                                               | BATSNS/MVBAT                     | TCXOEN = High                                                                       | 2.32                | 2.35         | 2.37        | kΩ     |  |

| Divider Impedance at MVBAT                                  | Zo                               |                                                                                     | 59.5                | 85           | 110         | kΩ     |  |

| Divider Leakage Current                                     |                                  | TCXOEN = Low                                                                        |                     |              | 1           | μΑ     |  |

| Divider Resistance                                          |                                  | TCXOEN = High                                                                       | 215                 | 300          | 385         | kΩ     |  |

| Parameter                           | Symbol                          | Condition                                            | Min   | Тур   | Max   | Unit       |

|-------------------------------------|---------------------------------|------------------------------------------------------|-------|-------|-------|------------|

| BATTERY CHARGER                     |                                 |                                                      |       |       |       |            |

| Charger Output Voltage              | BATSNS                          | $4.35 \text{ V} \le \text{CHRIN} \le 10 \text{ V}^3$ | 4.150 | 4.200 | 4.250 | V          |

|                                     |                                 | CHGEN = Low, No Load                                 |       |       |       |            |

| Load Regulation                     | ∆BATSNS                         | CHRIN = 5 V                                          |       |       | 15    | mV         |

|                                     |                                 | $0 \leq CHRIN - ISENSE$                              |       |       |       |            |

|                                     |                                 | < Current Limit Threshold<br>CHGEN = Low             |       |       |       |            |

| CHRDET On Threshold                 | CHRIN – BATSNS                  | CHGEN - Low                                          | 30    | 90    | 150   | mV         |

| CHRDET Off Threshold                | CHRIN – BATSNS                  |                                                      | 15    | 45    | 100   | mV         |

| CHRDET Off Delay <sup>4</sup>       |                                 | CHRIN < VBAT                                         |       | 6     | 100   | ms/nF      |

| CHRIN Supply Current                |                                 | CHRIN = 5 V                                          |       | 0.6   |       | mA         |

| BATTERY CHARGER                     |                                 |                                                      |       |       |       |            |

| Current Limit Threshold             | CHRIN – ISENSE                  |                                                      |       |       |       |            |

| High Current Limit                  |                                 | CHRIN = 5 V dc                                       | 142   | 160   | 190   | mV         |

| (UVLO Not Active)                   |                                 | VBAT = 3.6 V                                         |       |       |       |            |

|                                     |                                 | CHGEN = Low                                          |       |       |       |            |

| Low Current Limit                   |                                 | VBAT = 2 V                                           |       | 20    | 35    | mV         |

| (UVLO Active)                       |                                 | CHGEN = Low                                          |       |       |       |            |

| ISENSE Bias Current                 |                                 | CHRIN = 5 V                                          |       | 200   |       | μA         |

| ISENSE DIAS CUITEIN                 |                                 |                                                      |       | 200   |       | μA         |

| End-of-Charge Signal Threshold      | CHRIN – ISENSE                  | CHRIN = 5 V                                          |       | 14    | 35    | mV         |

|                                     |                                 | VBAT > 4.0 V                                         |       |       |       |            |

|                                     |                                 | CHGEN = Low                                          |       |       |       |            |

| EOC Reset Threshold                 | VBAT                            | CHGEN = Low                                          | 3.82  | 3.96  | 4.10  | v          |

|                                     |                                 |                                                      |       |       |       |            |

| GATEDR Transition Time              | t <sub>R</sub> , t <sub>F</sub> | CHRIN = 5 V                                          | 0.1   |       | 1     | μs         |

|                                     |                                 | VBAT > 3.6 V                                         |       |       |       |            |

|                                     |                                 | CHGEN = High, $C_L = 2 \text{ nF}$                   |       |       |       |            |

| GATEDR High Voltage                 | V <sub>OH</sub>                 | CHRIN = 5 V                                          | 4.5   |       |       | V          |

|                                     |                                 | VBAT = 3.6 V                                         |       |       |       |            |

|                                     |                                 | CHGEN = High,                                        |       |       |       |            |

|                                     |                                 | GATEIN = High                                        |       |       |       |            |

|                                     |                                 | $I_{OH} = -1 \text{ mA}$                             |       |       | 0.5   | v          |

| GATEDR Low Voltage                  | V <sub>OL</sub>                 | CHRIN = 5 V<br>VBAT = 3.6 V                          |       |       | 0.5   | v          |

|                                     |                                 | CHGEN = High                                         |       |       |       |            |

|                                     |                                 | GATEIN = Low                                         |       |       |       |            |

|                                     |                                 | $I_{OL} = 1 \text{ mA}$                              |       |       |       |            |

| Output High Voltage                 | V <sub>OH</sub>                 | $I_{OH} = -250 \ \mu A$                              | 2.4   |       |       | V          |

| (EOC, CHRDET)                       | 37                              | I = 1250 ··· A                                       |       |       | 0.05  | <b>X</b> 7 |

| Output Low Voltage<br>(EOC, CHRDET) | V <sub>OL</sub>                 | $I_{OL} = +250 \ \mu A$                              |       |       | 0.25  | V          |

| Battery Overvoltage                 | BATSNS                          | CHRIN = 7.5 V                                        | 5.30  | 5.50  | 5.70  | v          |

| Protection Threshold                |                                 | CHGEN = High                                         | 5.50  | 5.50  | 5.10  | •          |

| $(GATEDR \rightarrow High)$         |                                 | GATEIN = Low                                         |       |       |       |            |

| Battery Overvoltage                 | BATSNS                          | CHRIN = 7.5 V                                        |       | 200   |       | mV         |

| Protection Hysteresis               |                                 | CHGEN = High                                         |       |       |       |            |

|                                     |                                 | GATEIN = Low                                         |       |       |       |            |

NOTES <sup>1</sup>All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. <sup>2</sup>This feature is intended to protect against catastophic failure of the device. Maximum allowed operating junction temperature is 125°C. Operation beyond 125°C could cause permanent damage to the device.

<sup>3</sup>No isolation diode present between charger input and battery.

<sup>4</sup>Delay set by external capacitor on the RESCAP pin.

Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin with respect to                                                |

|-----------------------------------------------------------------------------------|

| any GND Pin                                                                       |

| Voltage on any pin may not exceed VBAT, with the following                        |

| exceptions: CHRIN, GATEDR, ISENSE                                                 |

| Storage Temperature Range65°C to +150°C                                           |

| Operating Ambient Temperature Range20°C to +85°C                                  |

| Maximum Junction Temperature 125°C                                                |

| $\theta_{JA}$ , Thermal Impedance (TSSOP-28)                                      |

| 4-Layer PCB 68°C/W                                                                |

| 1-Layer PCB                                                                       |

| Lead Temperature Range (Soldering, 60 sec.) 300°C                                 |

| *This is a stress rating only; operation beyond these limits can cause the device |

| to be permanently damaged.                                                        |

#### **ORDERING GUIDE**

| Model                            | Core LDO<br>Output<br>Voltage | Package<br>Option* |

|----------------------------------|-------------------------------|--------------------|

| ADP3408ARU-2.5<br>ADP3408ARU-1.8 |                               | <br>RU-28<br>RU-28 |

\*RU = Thin Shrink Small Outline

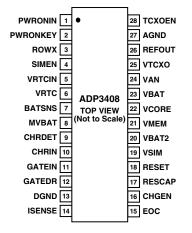

#### PIN CONFIGURATION

| MnemonicFunctionPWRONINPower On/Off Signal from<br>MicroprocessorPWRONKEYPower On/Off KeyROWXPower-On/-Off KeyROWXPower Key Interface OutputSIMENSIM LDO EnableVRTCINRTC LDO Input VoltageVRTCReal-Time Clock Supply/<br>Coin Cell Battery ChargerBATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVCOREDigital Core LDO OutputVEATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and<br>MVBAT Enable                                                                                  | PIN FUNCTION DESCRIPTIONS |                                |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------|--|--|--|--|--|--|--|

| PWRONKEY<br>ROWXMicroprocessor<br>Power-On/-Off Key<br>Power Key Interface Output<br>SIMENSIMENSIM LDO Enable<br>RTC LDO Input Voltage<br>VRTCVRTCReal-Time Clock Supply/<br>Coin Cell Battery Charger<br>Battery Voltage Sense Input<br>Divided Battery Voltage Output<br>Charge Detect Output<br>CHRDETMVBATDivided Battery Voltage Output<br>Charge Detect Output<br>Charge Detect OutputGATEINMicroprocessor Gate Input<br>SignalGATEDRGate Drive Output<br>DGNDDGNDDigital Ground<br>Charge Current Sense Input<br>EOCEOCEnd of Charge Signal<br>Charger Enable for GATEIN,<br>NiMH Pulse Charging<br>RESCAP<br>RESETRESCAPReset Delay Time<br>Main ResetVSIMSIM LDO Output<br>Voltage 2VMEMMemory LDO Output<br>VoltageVCOREDigital Core LDO Output<br>VCOREVSATBattery Input Voltage<br>Analog LDO OutputVEATOutput Reference<br>AGNDAGNDAnalog Ground<br>TCXO LDO Enable and | Mnemonic                  | Function                       |  |  |  |  |  |  |  |

| PWRONKEYPower-On/-Off KeyROWXPower Key Interface OutputSIMENSIM LDO EnableVRTCINRTC LDO Input VoltageVRTCReal-Time Clock Supply/<br>Coin Cell Battery ChargerBATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputSENSECharge Current Sense InputBOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVOREDigital Core LDO OutputVCOREDigital Core LDO OutputVEATBattery Input VoltageVANAnalog LDO OutputVEATOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                            | PWRONIN                   | Power On/Off Signal from       |  |  |  |  |  |  |  |

| ROWXPower Key Interface OutputSIMENSIM LDO EnableVRTCINRTC LDO Input VoltageVRTCReal-Time Clock Supply/<br>Coin Cell Battery ChargerBATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGATEDRGATEDRGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                   |                           | Microprocessor                 |  |  |  |  |  |  |  |

| SIMENSIM LDO EnableVRTCINRTC LDO Input VoltageVRTCReal-Time Clock Supply/<br>Coin Cell Battery ChargerBATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputJOGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVEATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO LDO Enable and                                                                                                                                                                                                                                                     | PWRONKEY                  | Power-On/-Off Key              |  |  |  |  |  |  |  |

| SIMENSIM LDO EnableVRTCINRTC LDO Input VoltageVRTCReal-Time Clock Supply/<br>Coin Cell Battery ChargerBATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputJOGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVEATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO LDO Enable and                                                                                                                                                                                                                                                     | ROWX                      | Power Key Interface Output     |  |  |  |  |  |  |  |

| VRTCReal-Time Clock Supply/<br>Coin Cell Battery ChargerBATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,NiMH Pulse ChargingRESCAPRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                        | SIMEN                     |                                |  |  |  |  |  |  |  |

| Coin Cell Battery ChargerBATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGATEDRGATEDRGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,NiMH Pulse ChargingRESCAPRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                    | VRTCIN                    | RTC LDO Input Voltage          |  |  |  |  |  |  |  |

| BATSNSBattery Voltage Sense InputMVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGATEDRGATEDRGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,NiMH Pulse ChargingRESCAPRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO ENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                          | VRTC                      | Real-Time Clock Supply/        |  |  |  |  |  |  |  |

| MVBATDivided Battery Voltage OutputCHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,NiMH Pulse ChargingRESCAPRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                        |                           | Coin Cell Battery Charger      |  |  |  |  |  |  |  |

| CHRDETCharge Detect OutputCHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,NiMH Pulse ChargingRESCAPRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                           | BATSNS                    | Battery Voltage Sense Input    |  |  |  |  |  |  |  |

| CHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGATEDRGATEDRGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO ENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                    | MVBAT                     | Divided Battery Voltage Output |  |  |  |  |  |  |  |

| CHRINCharger Input VoltageGATEINMicroprocessor Gate InputSignalGATEDRGATEDRGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO ENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                    | CHRDET                    | Charge Detect Output           |  |  |  |  |  |  |  |

| SignalGATEDRGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO ENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CHRIN                     |                                |  |  |  |  |  |  |  |

| GATEDRGate Drive OutputDGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO ENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GATEIN                    | Microprocessor Gate Input      |  |  |  |  |  |  |  |

| DGNDDigital GroundISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXO ENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           | Signal                         |  |  |  |  |  |  |  |

| ISENSECharge Current Sense InputEOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GATEDR                    | Gate Drive Output              |  |  |  |  |  |  |  |

| EOCEnd of Charge SignalCHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DGND                      | Digital Ground                 |  |  |  |  |  |  |  |

| CHGENCharger Enable for GATEIN,<br>NiMH Pulse ChargingRESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ISENSE                    | Charge Current Sense Input     |  |  |  |  |  |  |  |

| RESCAPNiMH Pulse ChargingRESETReset Delay TimeVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EOC                       | End of Charge Signal           |  |  |  |  |  |  |  |

| RESCAPReset Delay TimeRESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHGEN                     | Charger Enable for GATEIN,     |  |  |  |  |  |  |  |

| RESETMain ResetVSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           | NiMH Pulse Charging            |  |  |  |  |  |  |  |

| VSIMSIM LDO OutputVBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RESCAP                    | Reset Delay Time               |  |  |  |  |  |  |  |

| VBAT2Battery Input Voltage 2VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RESET                     | Main Reset                     |  |  |  |  |  |  |  |

| VMEMMemory LDO OutputVCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VSIM                      | SIM LDO Output                 |  |  |  |  |  |  |  |

| VCOREDigital Core LDO OutputVBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VBAT2                     | Battery Input Voltage 2        |  |  |  |  |  |  |  |

| VBATBattery Input VoltageVANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VMEM                      | Memory LDO Output              |  |  |  |  |  |  |  |

| VANAnalog LDO OutputVTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VCORE                     | Digital Core LDO Output        |  |  |  |  |  |  |  |

| VTCXOTCXO LDO OutputREFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VBAT                      | Battery Input Voltage          |  |  |  |  |  |  |  |

| REFOUTOutput ReferenceAGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VAN                       | Analog LDO Output              |  |  |  |  |  |  |  |

| AGNDAnalog GroundTCXOENTCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VTCXO                     | TCXO LDO Output                |  |  |  |  |  |  |  |

| TCXOEN TCXO LDO Enable and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REFOUT                    | Output Reference               |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AGND                      | Analog Ground                  |  |  |  |  |  |  |  |

| MVBAT Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TCXOEN                    | TCXO LDO Enable and            |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           | MVBAT Enable                   |  |  |  |  |  |  |  |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADP3408 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Pin

Table I. LDO Control Logic

| PHONE STATUS                                    | DDLO | nVLO* | CHRDET | PWRONKEY | PWRONIN | TCXOEN | SIMEN | MISV | VCORE | VAN and REFOUT | VTCXO | VMEM | VRTC | MVBAT |

|-------------------------------------------------|------|-------|--------|----------|---------|--------|-------|------|-------|----------------|-------|------|------|-------|

| State #1<br>Battery Deep Discharged             | L    | х     | Х      | Х        | Х       | L      | x     | OFF  | OFF   | OFF            | OFF   | OFF  | OFF  | OFF   |

| State #2<br>Phone Off                           | Н    | L     | X      | X        | X       | L      | X     | OFF  | OFF   | OFF            | OFF   | OFF  | ON   | OFF   |

| State #3<br>Phone Off,<br>Turn-On Allowed       | Н    | Н     | L      | Н        | L       | L      | x     | OFF  | OFF   | OFF            | OFF   | OFF  | ON   | OFF   |

| State #4<br>Charger Applied                     | Н    | Н     | Н      | x        | x       | L      | L     | OFF  | ON    | ON             | ON    | ON   | ON   | OFF   |

| State #5<br>Phone Turned On by<br>User Key      | Н    | Н     | X      | L        | X       | L      | L     | OFF  | ON    | ON             | ON    | ON   | ON   | OFF   |

| State #6<br>Phone Turned On by BB               | Н    | Н     | L      | Н        | Н       | L      | L     | OFF  | ON    | OFF            | OFF   | ON   | ON   | OFF   |

| State #7<br>Enable SIM Card                     | Н    | Н     | L      | Н        | Н       | L      | Н     | ON   | ON    | OFF            | OFF   | ON   | ON   | OFF   |

| State #8<br>Phone and TCXO<br>LDO Kept On by BB | Н    | Н     | L      | Н        | Н       | Н      | Н     | ON   | ON    | ON             | ON    | ON   | ON   | ON    |

\*UVLO is active only when phone is turned off. UVLO is ignored once the phone is turned on.

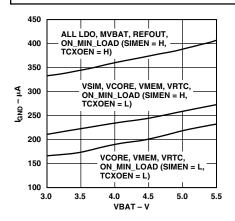

TPC 1. Ground Current vs. Battery Voltage

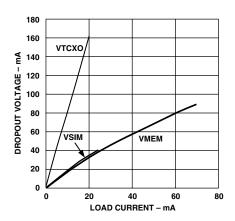

TPC 4. Dropout Voltage vs. Load Current

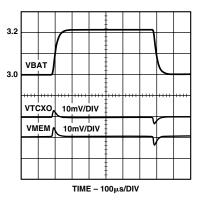

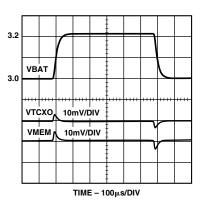

TPC 7. Line Transient Response, Minimum Loads

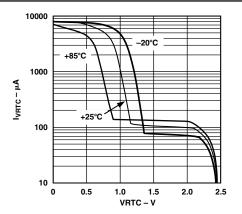

TPC 2. RTC I/V Characteristic

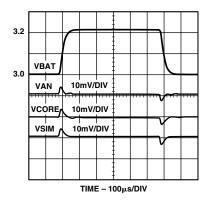

TPC 5. Line Transient Response, Minimum Loads

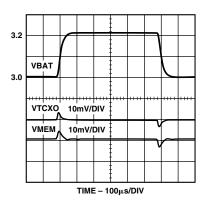

TPC 8. Line Transient Response, Maximum Loads

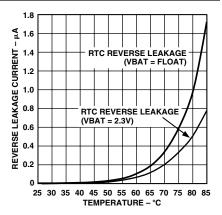

*TPC 3. VRTC Reverse Leakage Current vs. Temperature*

*TPC 6. Line Transient Response, Maximum Loads*

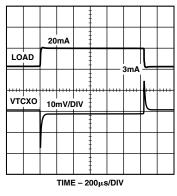

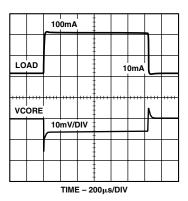

TPC 9. VTCXO Load Step

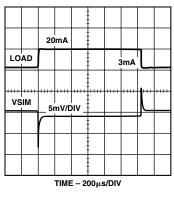

TPC 10. VSIM Load Step

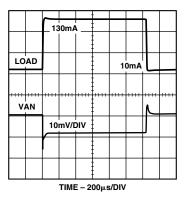

TPC 13. VAN Load Step

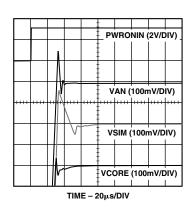

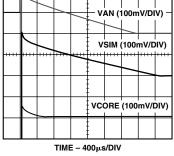

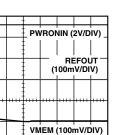

TPC 16. Turn On Transient by PWRONIN, Maximum Load (Part 1)

PWRONIN (2V/DIV) VAN (100mV/DIV)

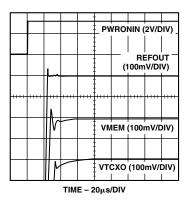

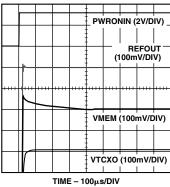

TPC 14. Turn On Transient by PWRONIN, Minimum Load (Part 1)

TPC 17. Turn On Transient by PWRONIN, Maximum Load (Part 2)

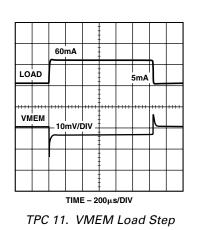

TPC 12. VCORE Load Step

TPC 15. Turn On Transient by PWRONIN, Minimum Load (Part 2)

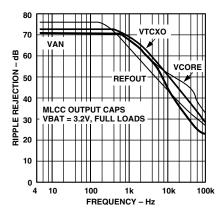

TPC 18. Ripple Rejection vs. Frequency

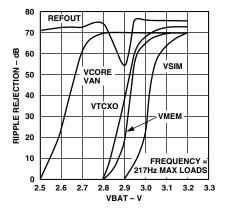

TPC 19. Ripple Rejection vs. Battery Voltage

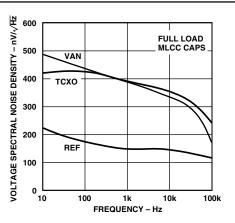

TPC 20. Output Noise Density

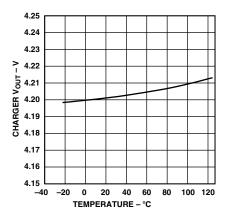

TPC 21. Charger  $V_{OUT}$  vs. Temperature,  $V_{IN} = 5.0$  V,  $I_{LOAD} = 10$  mA

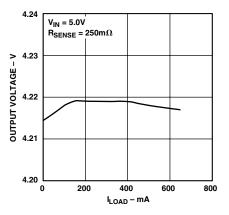

TPC 22. Charger  $V_{OUT}$  vs.  $I_{LOAD}$ ( $V_{IN} = 5.0 V$ )

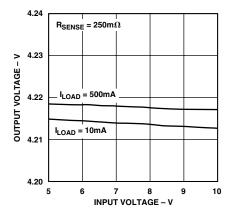

TPC 23. Charger  $V_{OUT}$  vs.  $V_{IN}$

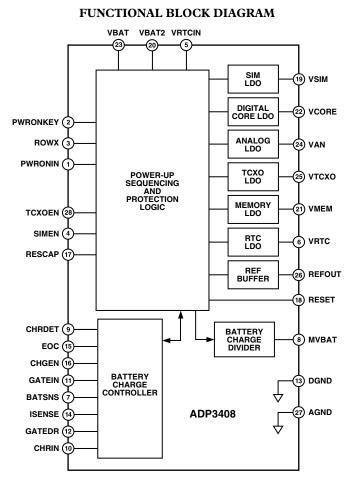

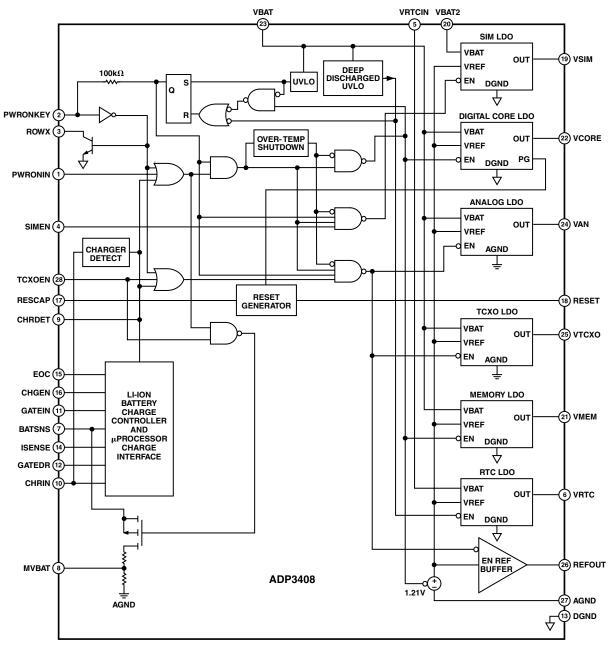

Figure 1. Functional Block Diagram

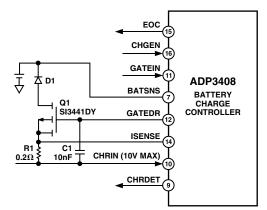

Figure 2. Battery Charger Typical Application

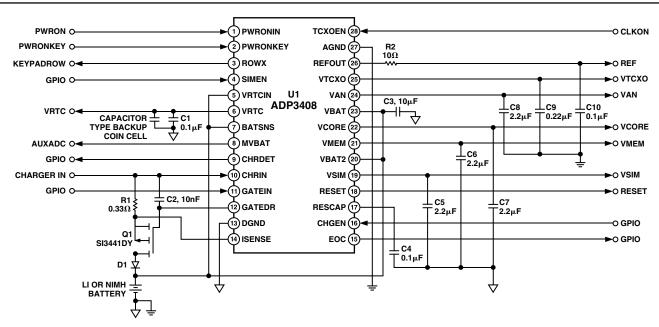

Figure 3. Typical Application Circuit

### THEORY OF OPERATION

The ADP3408 is a power management chip optimized for use with GSM baseband chipsets in handset applications. Figure 1 shows a block diagram of the ADP3408.

The ADP3408 contains several blocks:

- Six Low Dropout Regulators (SIM, Core, Analog, Crystal Oscillator, Memory, Real-Time Clock)

- Reset Generator

- Buffered Precision Reference

- Lithium Ion Charge Controller and Processor Interface

- Power-On/-Off Logic

- Undervoltage Lockout

- Deep Discharge Lockout

These functions have traditionally been done either as a discrete implementation or as a custom ASIC design. The ADP3408 combines the benefits of both worlds by providing an integrated standard product where every block is optimized to operate in a GSM environment while maintaining a cost competitive solution.

Figure 3 shows the external circuitry associated with the ADP3408. Only a minimal number of support components are required.

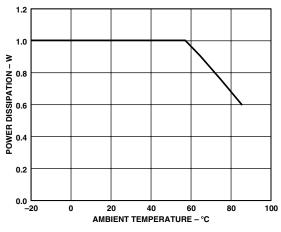

#### Input Voltage

The input voltage range of the ADP3408 is 3 V to 5.5 V and is optimized for a single Li-Ion cell or three NiMH cells. The thermal impedance of the ADP3408 is 68°C/W for four-layer boards. The end-of-charge voltage for high capacity NiMH cells can be as high as 5.5 V. Power dissipation should be calculated at maximum ambient temperatures and battery voltage in order not to exceed the 125°C maximum allowable junction temperature. Figure 4 shows the maximum power dissipation as a function of ambient temperature.

However, high battery voltages normally occur only when the battery is being charged and the handset is not in conversation mode. In this mode there is a relatively light load on the LDOs. A fully charged Li-Ion battery is 4.25 V, where the ADP3408 can deliver the maximum power (0.56W) up to 85°C ambient temperature.

Figure 4. Power Dissipation vs. Temperature

### Low Dropout Regulators (LDOs)

The ADP3408 high-performance LDOs are optimized for their given functions by balancing quiescent current, dropout voltage, regulation, ripple rejection, and output noise. 2.2  $\mu$ F tantalum or MLCC ceramic capacitors are recommended for use with the core, memory, SIM, and analog LDOs. A 0.22  $\mu$ F capacitor is recommended for the TCXO LDO.

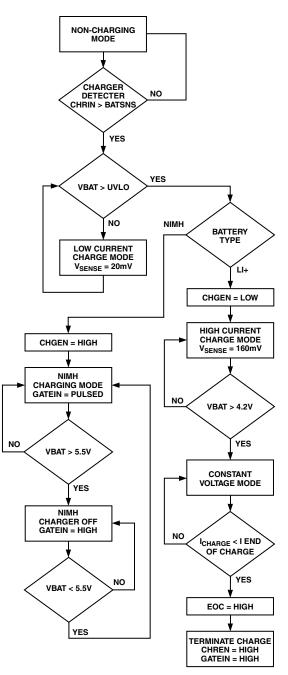

Figure 5. Battery Charger Flow Chart

### Digital Core LDO (VCORE)

The digital core LDO supplies the baseband circuitry in the handset (baseband processor and baseband converter). The LDO has been optimized for very low quiescent current at light loads as this LDO is on at all times.

### Memory LDO (VMEM)

The memory LDO supplies the peripheral subsystems of the baseband processor including GPIO, display, and SIM interfaces as well as memory. The LDO has also been optimized for low quiescent current and will power up at the same time as the core LDO.

#### Analog LDO (VAN)

This LDO has the same features as the core LDO. It has furthermore been optimized for good low frequency ripple rejection for use with the baseband converter sections in order to reject the ripple coming from the RF power amplifier. VAN is rated to 130 mA load, which is sufficient to supply the complete analog section of the baseband converter such as the AD6521.

#### TCXO LDO (VTCXO)

The TCXO LDO is intended as a supply for a temperaturecompensated crystal oscillator, which needs its own ultralow noise supply. VTCXO is rated for 5 mA of output current and is turned on along with the analog LDO when TCXOEN is asserted.

#### **RTC LDO (VRTC)**

The RTC LDO charges up a capacitor-type backup coin cell to run the real-time clock module. It has been designed to charge electric double layer capacitors such as the PAS621 from Kanebo. The PAS621 has a small physical size (6.8 mm diameter) and a nominal capacity of 0.3 F, giving many hours of backup time.

The ADP3408 supplies current both for charging the coin cell and for the RTC module when the digital supply is off. The nominal charging voltage is 2.45 V, which ensures long cell life while obtaining in excess of 90% of the nominal capacity. In addition, it features a very low quiescent current since this LDO is running all the time, even when the handset is switched off. It also has reverse current protection with low leakage, which is needed when the main battery is removed and the coin cell supplies the RTC module.