### = Preliminary =

# AK4710

Low Power Single SCART Driver

### FEATURES

Audio section

□ THD+N: –92dB (@2Vrms)

□ Dynamic Range: 96dB (@2Vrms, A-weighted)

□ Full Differential or Single-ended input for Decoder DAC

□ Stereo Output for TV SCART and CINCH (2Vrms)

□ Ground-Referenced Output Eliminates

**DC-Blocking Capacitor and Mute Circuit**

Video section

□ Integrated LPF: -40dB@27MHz

□ 6dB Gain for Outputs

□ 5ch 75ohm driver

4ch for SCART: CVBS/Y, R/C, G, B

1ch for CINCH: CVBS

□ Y/Pb/Pr Option (to 6MHz)

Low-power Standby

SCART pin#16(Fast Blanking), pin#8(Slow Blanking) Output Control

Power supply

□ 3.3V+/–5% and 12V+/–5%

□ Low Power Dissipation / Low Power Standby Mode

Package

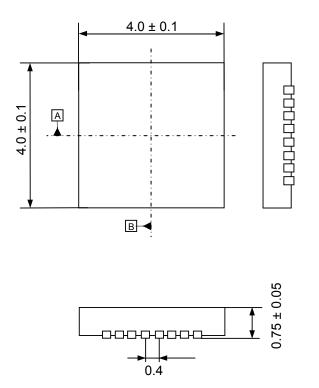

□ 32pin QFN (0.4mm pitch)

### Asahi**KASEI**

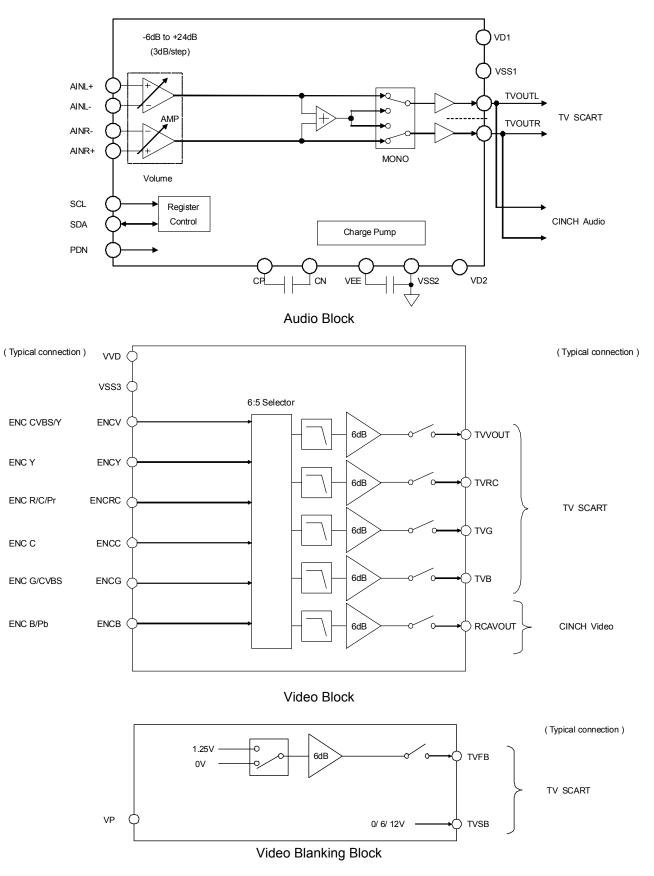

### Block Diagram

### Ordering Guide

| AK4710EN | -10 ~ +70°C             | 32pin QFN (0.4mm pitch) |

|----------|-------------------------|-------------------------|

| AKD4710  | Evaluation board for Ak | \$4710                  |

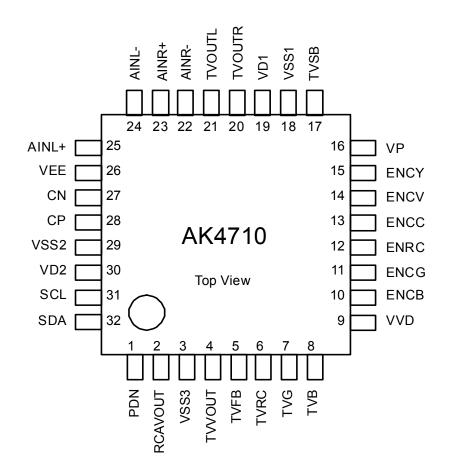

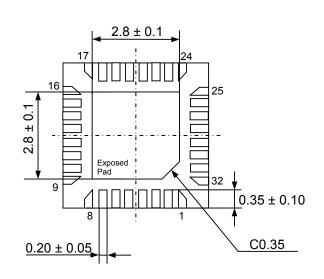

### Pin Layout

32pin QFN (0.4mm pitch)

### **PIN/FUNCTION**

| No. | Pin Name | I/O | Function                                                                                       |

|-----|----------|-----|------------------------------------------------------------------------------------------------|

| 1   |          |     | Power-Down Mode Pin                                                                            |

|     | PDN      | Ι   | When at "L", the AK4710 is in the power-down mode and is held in reset. The                    |

|     |          | _   | AK4710 should always be reset upon power-up.                                                   |

| 2   | RCAVOUT  | 0   | Composite/Luminance Output Pin for RCA                                                         |

| 3   | VSS3     | -   | Video Ground Pin , 0V                                                                          |

| 4   | TVVOUT   | 0   | Composite/Luminance Output Pin for TV                                                          |

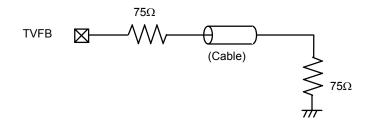

| 5   | TVFB     | 0   | Fast Blanking Output Pin for TV                                                                |

| 6   | TVRC     | 0   | Red/Chrominance Output Pin for TV                                                              |

| 7   | TVG      | 0   | Green Output Pin for TV                                                                        |

| 8   | TVB      | 0   | Blue Output Pin for TV                                                                         |

|     |          |     | Video Power Supply Pin: 3.13V ~ 3.47V                                                          |

| 9   | VVD      | -   | Normally connected to VSS3 with a $0.1 \mu F$ ceramic capacitor in parallel with a $4.7 \mu F$ |

|     |          |     | electrolytic capacitor.                                                                        |

| 10  | ENCB     | Ι   | Blue Input Pin for Encoder                                                                     |

| 11  | ENCG     | Ι   | Green Input Pin for Encoder                                                                    |

| 12  | ENCRC    | Ι   | Red/Chrominance Input Pin #1 for Encoder                                                       |

| 13  | ENCC     | Ι   | Chrominance Input Pin #2 for Encoder                                                           |

| 14  | ENCV     | Ι   | Composite/Luminance Input Pin #1 for Encoder                                                   |

| 15  | ENCY     | Ι   | Composite/Luminance Input Pin #2 for Encoder                                                   |

|     |          |     | Blanking Power Supply Pin, 10.8V ~ 13.2V                                                       |

| 16  | VP       | -   | The VP pin must connect to power supply through 10ohm resistor with 0.1µF                      |

|     |          |     | ceramic capacitor in parallel with a $1\mu$ F electrolytic capacitor to VSS1.                  |

|     |          |     | Slow Blanking Output Pin for TV                                                                |

| 17  | TVSB     | 0   | A 470ohm ±5% resistor must be connected between the TVSB pin and SCART                         |

|     |          |     | connector.                                                                                     |

| 18  | VSS1     | -   | Audio Ground Pin, 0V                                                                           |

|     |          |     | Audio Power Supply Pin: 3.13V ~ 3.47V                                                          |

| 19  | VD1      | -   | Normally connected to VSS1 with a $0.1 \mu F$ ceramic capacitor in parallel with a $4.7 \mu F$ |

|     |          |     | electrolytic capacitor.                                                                        |

| 20  | TVOUTR   | 0   | Rch Analog Output Pin #2                                                                       |

| 21  | TVOUTL   | 0   | Lch Analog Output Pin #2                                                                       |

| 22  | AINRN    | Ι   | Rch Negative Analog Input Pin                                                                  |

| 23  | AINRP    | Ι   | Rch Positive Analog Input Pin                                                                  |

| 24  | AINLN    | Ι   | Lch Negative Analog Input Pin                                                                  |

| 25  | AINLP    | Ι   | Lch Positive Analog Input Pin                                                                  |

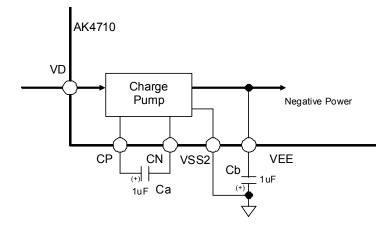

| 26 | VEE  | О   | Negative Voltage Output Pin<br>Connect to VSS2 with a $1.0\mu$ F capacitor that should have the low ESR (Equivalent<br>Series Resistance) over all temperature range. When this capacitor has the polarity,<br>the positive polarity pin should be connected to the VSS2 pin. Non polarity<br>capacitors can also be used.             |

|----|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27 | CN   | Ι   | Negative Charge Pump Capacitor Terminal Pin<br>Connect to CP with a $1.0\mu$ F capacitor that should have the low ESR (Equivalent<br>Series Resistance) over all temperature range. When this capacitor has the polarity,<br>the positive polarity pin should be connected to the CP pin. Non polarity capacitors<br>can also be used. |

| 28 | СР   | I   | Positive Charge Pump Capacitor Terminal Pin<br>Connect to CN with a 1.0µF capacitor that should have the low ESR (Equivalent<br>Series Resistance) over all temperature range. When this capacitor has the polarity,<br>the positive polarity pin should be connected to the CP pin. Non polarity capacitors<br>can also be used.      |

| 29 | VSS2 | -   | Charge Pump Ground Pin, 0V                                                                                                                                                                                                                                                                                                             |

| 30 | VD2  | -   | Charge Pump Power Supply Pin: 3.13V ~ 3.47V<br>Normally connected to VSS2 with a 0.1μF ceramic capacitor in parallel with a 4.7μF<br>electrolytic cap.                                                                                                                                                                                 |

| 31 | SCL  | Ι   | Control Data Clock Pin                                                                                                                                                                                                                                                                                                                 |

| 32 | SDA  | I/O | Control Data Pin                                                                                                                                                                                                                                                                                                                       |

Note: All digital input pins should not be left floating.

| ABSOLU                                       | TE MAXIMUM RATIN | NGS     |         |       |

|----------------------------------------------|------------------|---------|---------|-------|

| (VSS1=VSS2=VSS3= 0V; Note 1)                 |                  |         |         |       |

| Parameter                                    | Symbol           | min     | max     | Units |

| Power Supply (Note 2)                        | VD1              | -0.3    | 4.0     | V     |

|                                              | VD2              | -0.3    | 4.0     | V     |

|                                              | VVD              | -0.3    | 4.0     | V     |

|                                              | VP               | -0.3    | 14      | V     |

| Input Current (any pins except for supplies) | IIN              | -       | ±10     | mA    |

| Digital Input Voltage(PDN pin)               | VIND1            | -0.3    | VVD+0.3 | V     |

| Digital Input Voltage(SCL, SDA pins)         | VIND2            | -0.3    | 4.0     | V     |

| Video Input Voltage                          | VINV             | -0.3    | VVD+0.3 | V     |

| Audio Input Voltage (Note 3)                 | VINA             | VEE-0.3 | VD1+0.3 | V     |

| Ambient Operating Temperature                | Та               | -10     | 70      | °C    |

| Storage Temperature                          | Tstg             | -65     | 150     | °C    |

Note 1. All voltages with respect to ground.

Note 2. VSS1, VSS2 and VSS3 must be connected to the same analog ground plane.

Note 3. VEE: VEE pin voltage.

The internal negative power supply generating circuit provides negative power supply(VEE). The PDN pin, MUTE bit, control operation mode as shown in Table 2 and Table 3.

|   | Mode             | VEE pin Voltage |    |

|---|------------------|-----------------|----|

| 0 | Full Power-down  | 0V              |    |

| 1 | Mute             | 0V              |    |

| 2 | Normal operation | No video input  | 0V |

| Z | Normal operation | -VD2+0.2V       |    |

Table 1. VEE pin voltage

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

| RECOMMENDED OPERATING CONDITIONS |         |      |     |      |       |

|----------------------------------|---------|------|-----|------|-------|

| (VSS1=VSS2=VSS3= 0V              | Note 1) |      |     |      |       |

| Parameter                        | Symbol  | Min  | typ | max  | Units |

| Power Supply (Note               | 4) VD1  | 3.13 | 3.3 | 3.47 | V     |

|                                  | VD2     | 3.13 | 3.3 | 3.47 | V     |

|                                  | VVD     | 3.13 | 3.3 | 3.47 | V     |

|                                  | VP      | 10.8 | 12  | 13.2 | V     |

Note 1. All voltages with respect to ground.

Note 4. VVD must be connected to the same voltage.

\*AKM assumes no responsibility for the usage beyond recommended operating conditions in this datasheet.

| ELECTRICAL CHARACTERISTICS       |          |     |     |     |       |  |

|----------------------------------|----------|-----|-----|-----|-------|--|

| (Ta = 25°C; VP=12V, VD1=VD2=VVD= | 3.3V)    |     |     |     |       |  |

| Power Supplies                   |          | min | typ | max | Units |  |

| Power Supply Current             |          |     |     |     |       |  |

| Normal Operation (PDN = "H")     | (Note 5) |     |     |     |       |  |

| VD1+VD2+VVD                      |          |     | 386 | TBD | μΑ    |  |

| VP                               |          |     | 48  | TBD | μΑ    |  |

| Power-Down Mode (PDN = "L")      | (Note 6) |     |     |     |       |  |

| VD1+VD2                          |          |     | 0   | TBD | μA    |  |

| VVD                              |          |     | 0   | TBD | μA    |  |

| VP                               |          |     | 48  | TBD | μΑ    |  |

Note 5. All video outputs active. No signal, no load for A/V switches, refer to the Table 3.

Note 6. All digital inputs are held at VVD or VSS3. No signal, no load for A/V switches.

|                                                     | DIGITAL CHARA | CTERISTICS |     |         |       |

|-----------------------------------------------------|---------------|------------|-----|---------|-------|

| $(Ta = 25^{\circ}C; VD1 = VD2 = VVD = 3.13 \sim 3)$ | 3.47V)        |            |     |         |       |

| Parameter                                           | Symbol        | min        | typ | max     | Units |

| High-Level Input Voltage                            | VIH           | 70%VVD     | -   | -       | V     |

| Low-Level Input Voltage                             | VIL           | -          | -   | 30% VVD | V     |

| Low-Level Output Voltage                            | VOL           | -          | -   | 0.4     | V     |

| (SDA pin: Iout= 3mA)                                |               |            |     |         |       |

| Input Leakage Current                               | Iin           | -          | -   | ± 10    | μΑ    |

### **ANALOG CHARACTERISTICS (AUDIO)**

(Ta=25°C; VP=12V, VD1=VD2=VVD =3.3V; Signal Frequency=1kHz; Measurement frequency=20Hz ~ 20kHz; R<sub>L</sub>  $\geq$ 4.5k $\Omega$ ; 0dB=2Vrms output; Volume=0dB, unless otherwise specified)

| Parameter                                        | min  | typ | max  | Units  |

|--------------------------------------------------|------|-----|------|--------|

| Analog Input: (AINL+/AINL-/AINR-/AINR+ pins)     |      |     |      |        |

| Analog Input Characteristics                     |      |     |      |        |

| Input Voltage (AIN+) – (AIN–), (Note 7)          |      |     | 2.0  | Vrms   |

| Input Resistance (AINL+, AINR+ pins)             | 85   | 120 |      | kΩ     |

| Input Resistance (AINL-, AINR- pins)             | 85   | 120 | -    | kΩ     |

| Stereo/Mono Output: (TVOUTL/TVOUTR pins) (Note   | 8)   |     |      |        |

| Analog Output Characteristics                    |      |     |      |        |

| Volume Step Width                                | 2.3  | 3.0 | 3.7  | dB     |

| THD+N (at 2Vrms output, Note 10, Note 12)        |      | -92 | -80  | dB     |

| Dynamic Rang (-60dB Output, A-weighted, Note 10) | 92   | 96  |      | dB     |

| S/N (A-weighted, Note 10, Note 14)               | 92   | 96  |      | dB     |

| Interchannel Isolation (Note 10, Note 11)        | 80   | 90  |      | dB     |

| Interchannel Gain Mismatch (Note 10, Note 11)    | -0.5 | 0   | +0.5 | dB     |

| DC offset (Note 13)                              | -5   | 0   | +5   | mV     |

| Gain Drift                                       | -    | 200 | -    | ppm/°C |

| Load Resistance                                  |      |     |      |        |

| TVOUTL/R                                         | 4.5  |     |      | kΩ     |

| Load Capacitance<br>TVOUTL/R                     |      |     | 20   | pF     |

| Output Voltage (Note 9)                          | 1.8  | 2   | 2.2  | Vrms   |

| Power Supply Rejection (PSR) (Note 15)           | _    | 50  |      | dB     |

Note 7. f = 1kHz, THD+N < -80dB, gain = 0dB(Volume=0dB)

Note 8. Measured by Audio Precision System Two Cascade.

Note 9. The output level of the internal AMP with volume should be less than 2Vrms.

Note 10. Analog In to TVOUT. Path : AINL+/- → TVOUTL, AINR+/- → TVOUTR, Volume0dB. At 2Vrms single input, TDH+N is -91dB (typ), on path AINL+ → TVOUTL, AINR+ → TVOUTR, Volume=0dB

Note 11. Between TVOUTL and TVOUTR with analog inputs AINL+/-, AINL/R+/-, 1kHz/0dB. Inter-channel crosstalk is -80dB (typ), at 20Hz~20kHz other than 1kHz.

Note 12. -79dB (typ) referred to 0.5Vrms output level at Volume=+24dB

: path = AIN+/-  $\rightarrow$  TVOUT.

Note 13. Analog In to TVOUT. Volume=0dB

- Path : AINL+/-  $\rightarrow$  TVOUTL, AINR+/-  $\rightarrow$  TVOUTR

- Note 14. 82dB (typ) referred to 0.5Vrms output level at Volume=+24dB

: path = AIN+/-  $\rightarrow$  TVOUT.

84dB (typ), referred to 0.5Vrm output level at Volume = +21dB.

Note 15. The PSR is applied to VD1 and VD2 with 1kHz, 100mV.

|                                      | ANALOG CHARACTERISTICS (VIDEO)                    |      |      |      |        |

|--------------------------------------|---------------------------------------------------|------|------|------|--------|

| $(Ta = 25^{\circ}C; VP = 12V, VD1 =$ | VD2=VVD=3.3V; unless otherwise specified.)        |      |      |      |        |

| Parameter                            | Conditions                                        | min  | typ  | max  | Units  |

| Sync Tip Clamp Voltage               | at output pin.                                    |      | 0.20 |      | V      |

| R/G/B Clamp Voltage                  | at output pin.                                    |      | 0.20 |      | V      |

| Pb/Pr Clamp Voltage                  | at output pin.                                    |      | 1.44 |      | V      |

| Chrominance Bias Voltage             | at output pin.                                    |      | 1.44 |      | V      |

| Gain                                 | Input = 0.3Vp-p, 100kHz                           | 5.5  | 6    | 6.5  | dB     |

| Interchannel Gain Mismatch           | TVRC, TVG, TVB. Input = 0.3Vp-p, 100kHz.          | -0.5 | -    | 0.5  | dB     |

| Frequency Response                   | Input=0.3Vp-p, C1=C2=0pF. 100kHz to 6MHz.         | -1.0 |      | 0.5  | dB     |

|                                      | at 10MHz.                                         |      | -3   |      | dB     |

|                                      | at 27MHz.                                         |      | -40  | -20  | dB     |

| Group Delay Distortion               | At 4.43MHz with respect to 1MHz.                  |      |      | 20   | ns     |

| Input Impedance                      | Chrominance input (internally biased)             | 80   | 100  | -    | kΩ     |

| Input Signal                         | f = 100 kHz, maximum with distortion $< 1.0%$ ,   |      |      | 1.25 | Van    |

|                                      | gain = 6 dB.                                      | -    | -    | 1.23 | Vpp    |

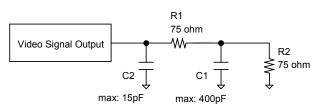

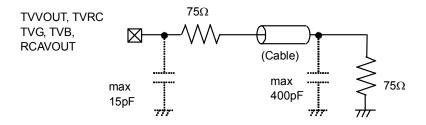

| Load Resistance                      | (Figure 1)                                        | 150  | -    | -    | Ω      |

| Load Capacitance                     | C1 (Figure 1)                                     |      |      | 400  | pF     |

|                                      | C2 (Figure 1)                                     |      |      | 15   | pF     |

| Dynamic Output Signal                | f = 100 kHz, maximum with distortion $< 1.0%$     | -    | -    | 2.5  | Vpp    |

| Y/C Crosstalk                        | f = 4.43MHz, 1Vp-p input. Among TVVOUT,           | -    | -50  |      | dB     |

|                                      | TVRC and RCAVOUT outputs.                         | _    | -30  | _    | uD     |

| S/N                                  | Reference Level = $0.7$ Vp-p, CCIR 567 weighting. |      | 74   | _    | dB     |

|                                      | BW = 15kHz to $5MHz$ .                            | _    | /4   | _    | uD     |

| Differential Gain                    | 0.7Vpp 5steps modulated staircase.                | -    | 0.6  | _    | %      |

|                                      | chrominance &burst are 280mVpp, 4.43MHz.          | -    | 0.0  | _    | 70     |

| Differential Phase                   | 0.7Vpp 5steps modulated staircase.                | _    | 1.4  | _    | Degree |

|                                      | chrominance &burst are 280mVpp, 4.43MHz.          | _    | 1.7  | -    | Degree |

Figure 1. Load Resistance R1+R2 and Load Capacitance C1/C2.

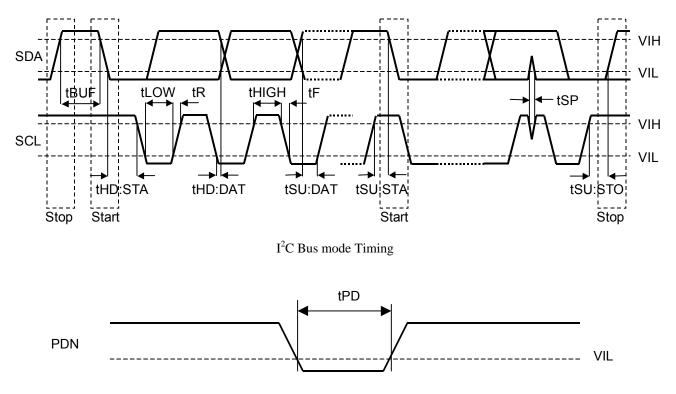

| SWITCHING CHARACTERISTICS                                                    |         |     |     |     |       |

|------------------------------------------------------------------------------|---------|-----|-----|-----|-------|

| $Ta = 25^{\circ}C; VP = 10.8 \sim 13.2V, VD1 = VD2 = VVD = 3.13 \sim 3.47V)$ |         |     |     |     |       |

| Parameter                                                                    | Symbol  | min | typ | max | Units |

| Control Interface Timing (I <sup>2</sup> C Bus):                             |         |     |     |     |       |

| SCL Clock Frequency                                                          | fSCL    | -   |     | 400 | kHz   |

| Bus Free Time Between Transmissions                                          | tBUF    | 1.3 |     | -   | μs    |

| Start Condition Hold Time                                                    | tHD:STA | 0.6 |     | -   | μs    |

| (prior to first clock pulse)                                                 |         |     |     |     |       |

| Clock Low Time                                                               | tLOW    | 1.3 |     | -   | μs    |

| Clock High Time                                                              | tHIGH   | 0.6 |     | -   | μs    |

| Setup Time for Repeated Start Condition                                      | tSU:STA | 0.6 |     | -   | μs    |

| SDA Hold Time from SCL Falling (Note 16)                                     | tHD:DAT | 0   |     | -   | μs    |

| SDA Setup Time from SCL Rising                                               | tSU:DAT | 0.1 |     | -   | μs    |

| Rise Time of Both SDA and SCL Lines                                          | tR      | -   |     | 0.3 | μs    |

| Fall Time of Both SDA and SCL Lines                                          | tF      | -   |     | 0.3 | μs    |

| Setup Time for Stop Condition                                                | tSU:STO | 0.6 |     | -   | μs    |

| Pulse Width of Spike Noise                                                   | tSP     | 0   |     | 50  | ns    |

| Suppressed by Input Filter                                                   |         |     |     |     |       |

| Capacitive load on bus                                                       | Cb      |     |     | 400 | pF    |

| Reset Timing                                                                 |         |     |     |     |       |

| PDN Pulse Width (Note 17)                                                    | tPD     | 150 |     |     | ns    |

Note 16. Data must be held for sufficient time to bridge the 300 ns transition time of SCL.

Note 17. The AK4710 should be reset once by bringing the PDN pin = "L" after all power supplies are supplied. Note 18.  $I^2$ C-bus is a trademark of NXP B.V.

### Timing Diagram

Power-down Timing

### **OPERATION OVERVIEW**

### 1. System Reset and Power-down Options

The AK4710 should be reset once by bringing the PDN pin = "L" after all power supplies are supplied. The AK4710 has several operation modes. The PDN pin and MUTE bit, control operation mode as shown in Table 2and Table 3.

#### System Reset and Full Power-down Mode

The AK4710 should be reset once by bringing the PDN pin = "L" after all power supplies are supplied.

PDN pin: Power down pin

L: Full Power-down Mode. Power-down, reset and initializes control registers.

H: Device active.

#### Mute Mode

When the MUTE bit = "1", the audio outputs settle to VSS (0V, typ) and the charge pump circuit is in power down mode.

MUTE bit (00H D1): Audio output control

- 0: Normal operation.

- 1: All audio outputs to GND (default)

| 0 |   |   | Mode                                |

|---|---|---|-------------------------------------|

| 0 | L | Х | Full Power-down                     |

| 1 | Н | 1 | Mute (Note 19)<br>(AMP power down)  |

| 2 | Н | 0 | Normal operation<br>(AMP operation) |

Note 19. TVOUTL/R are muted by Mute bit in the default state.

|   | Mode                       |                   | Register<br>Control | Audio<br>Charge pump | Video<br>Output | TVFB      | TVSB                       | Power<br>Consumption<br>(typ.) (Note 20) |   |           |      |   |                 |   |        |

|---|----------------------------|-------------------|---------------------|----------------------|-----------------|-----------|----------------------------|------------------------------------------|---|-----------|------|---|-----------------|---|--------|

| 0 | ) Full Power-down          |                   | NOT<br>available    |                      | Hi-Z            | Hi-Z      | Pull<br>-down<br>(Note 21) | 0.6mW                                    |   |           |      |   |                 |   |        |

| 1 | 1 Mute<br>(AMP power down) | No Video<br>Input |                     | Power down           |                 |           |                            | 1.86mW                                   |   |           |      |   |                 |   |        |

|   |                            | Video<br>Input    | A                   | Assoilable           | Available       | Available | Augilahla                  | Available                                | t | Available | nnut | + | Hi-Z/<br>Active | A | Active |

| 2 | Normal operation           | No video<br>input | Available           |                      | Hi-Z            | Active    | Active                     | 1.86mW                                   |   |           |      |   |                 |   |        |

| 2 | (AMP operation)            | Video<br>input    |                     | Active               | Hi-Z/<br>Active |           |                            | 250mW                                    |   |           |      |   |                 |   |        |

Note 20. 1kHz 2Vrms output with  $4.5k\Omega$  load at all audio output pins.

47.46 IRE at all video inputs corresponding to all video output pins with  $150\Omega$  load.

Note 21. Internally pulled down by  $120k\Omega$  (typ) resistor.

Table 3. Status of Each Operation Modes

### Asahi**KASEI**

#### ■ Normal Operation Mode

To change analog switches, set the MUTE bit to "0". The AK4710/11 is in power-down mode until the PDN pin = "H". The Figure X shows an example of the system timing at the power-down and power-up by the PDN pin.

### Typical Operation Sequence

Figure 2 shows an example of the system timing at normal operation mode.

| PDN pin      |               | "Normal"  | "Mute"    | "Normal"  |           |

|--------------|---------------|-----------|-----------|-----------|-----------|

|              |               |           |           |           |           |

| MUTE bit     | "1" (default) | "0"       | "1"       | "0"       | "1"       |

|              |               |           |           |           |           |

| Video Signal | No Signal     |           | Signal In |           | No Signal |

| Video Detect | 175ms(MAX)    | <b>-</b>  |           |           |           |

| Video Output | Hi-z          |           | Active    |           | Hi-z      |

|              |               |           |           |           |           |

| TVOUT -      | (GND)         | Analog in |           | Analog in |           |

|              | -             | 50ms(MAX) | 50ms(MAX) | <b>-</b>  |           |

| Charge pump  |               | (Note21)  |           | (Note21)  |           |

Note 22. Mute the analog outputs externally if click noise affects the system.

Figure 2. Typical Operating Sequence

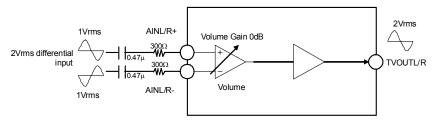

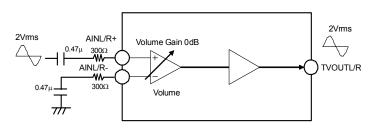

### 2. Audio Block

### ■ Volume Control (11-Level Volume)

The AK4710 has an 11-level volume control as shown in Table 4. The volume reflects the change of register value immediately.

Figure 3. Volume (Volume Gain=0dB: default), Full Differential Stereo Input

| VOL3 | VOL2 | VOL1 | VOL0 | Volume Gain | Output Level (Typ)                             |

|------|------|------|------|-------------|------------------------------------------------|

| 1    | 1    | Х    | Х    |             | Reserved                                       |

| 1    | 0    | 1    | 1    | +24dB       | 2Vrms (with 0.13Vrms differential input)       |

| 1    | 0    | 1    | 0    | +21dB       | -                                              |

| 1    | 0    | 0    | 1    | +18dB       | 2Vrms (with 0.25Vrms differential input)       |

| 1    | 0    | 0    | 0    | +15dB       | -                                              |

| 0    | 1    | 1    | 1    | +12dB       | 2Vrms (with 0.5Vrms differential input)        |

| 0    | 1    | 1    | 0    | +9dB        | -                                              |

| 0    | 1    | 0    | 1    | +6dB        | 2Vrms (with 1Vrms differential input)          |

| 0    | 1    | 0    | 0    | +3dB        | -                                              |

| 0    | 0    | 1    | 1    | 0dB         | 2Vrms (with 2Vrms differential input: default) |

| 0    | 0    | 1    | 0    | -3dB        | -                                              |

| 0    | 0    | 0    | 1    | -6dB        | 1Vrms (with 2Vrms differential input)          |

| 0    | 0    | 0    | 0    | Mute        | -                                              |

Table 4. Volume, Full Differential Stereo Input

Figure 4. Volume (Volume Gain=0dB:default), Single-ended Input

#### (0DH: D6-D3)

| VOL3 | VOL2 | VOL1 | VOL0 | Volume Gain | Output Level (Typ)                |

|------|------|------|------|-------------|-----------------------------------|

| 1    | 1    | Х    | Х    |             | Reserved                          |

| 1    | 0    | 1    | 1    | +24dB       | 2Vrms (with 0.13Vrms input)       |

| 1    | 0    | 1    | 0    | +21dB       | -                                 |

| 1    | 0    | 0    | 1    | +18dB       | 2Vrms (with 0.25Vrms input)       |

| 1    | 0    | 0    | 0    | +15dB       | -                                 |

| 0    | 1    | 1    | 1    | +12dB       | 2Vrms (with 0.5Vrms input)        |

| 0    | 1    | 1    | 0    | +9dB        | -                                 |

| 0    | 1    | 0    | 1    | +6dB        | 2Vrms (with 1Vrms input)          |

| 0    | 1    | 0    | 0    | +3dB        | -                                 |

| 0    | 0    | 1    | 1    | 0dB         | 2Vrms (with 2Vrms input: default) |

| 0    | 0    | 1    | 0    | -3dB        | -                                 |

| 0    | 0    | 0    | 1    | -6dB        | 1Vrms (with 2Vrms input)          |

| 0    | 0    | 0    | 0    | Mute        | -                                 |

Table 5. Volume, Single-ended Input

(x: Don't care)

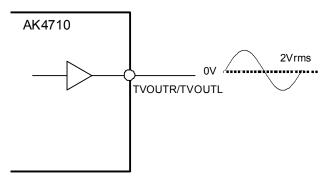

### Analog output block

The AK4710 has a charge pump circuit generating negative power supply rail from a 3.3V(typ) power supply. (Figure 5) It allows the AK4710 to output audio signal centered at VSS (0V, typ) as shown in Figure 6. The negative power generating circuit (Figure 5) needs 1.0uF capacitors (Ca, Cb) with low ESR (Equivalent Series Resistance). When using capacitors with a polarity, the positive side should be connected to CP and VSS2 for capacitor Ca and Cb, respectively. When the MUTE bit = "1", the charge pump circuit is in power down mode and its analog outputs become VSS (0V, typ).

Figure 5. Negative Power Generate Circuit

Figure 6. Audio Signal Output

### 3. Video Block

### ■ Video Switch Control

The AK4710 has switches for TV. Each switch can be controlled via the registers independently.

(04H: D1-D0)

| Mode               | VTV1-0 bit | Source of<br>TVVOUT pin | Source of TVRC pin | Source of<br>TVG pin | Source of TVB pin |

|--------------------|------------|-------------------------|--------------------|----------------------|-------------------|

| Shutdown (default) | 00         | (Hi-Z)                  | (Hi-Z)             | (Hi-Z)               | (Hi-Z)            |

| Encoder            |            | ENCV pin                | ENCRC pin          | ENCG pin             | ENCB pin          |

| CVBS+RGB           | 01         | (Encoder CVBS           | (Encoder Red,C     | (Encoder Green       | (Encoder Blue     |

| or Encoder YPbPr   |            | or Y)                   | or Pb)             | or Y)                | or Pr)            |

| Encoder Y/C 1      | 10         | ENCV pin                | ENCRC pin          | (Hi-Z)               | (Hi-Z)            |

| Elicodel 1/C I     | 10         | (Encoder Y)             | (Encoder C)        | (m-z)                | (пі-2)            |

| Encoder Y/C 2      | 11         | ENCY pin                | ENCC pin           | (Hi-Z)               | ( <b>U; 7</b> )   |

| Elicouer 1/C 2     | 11         | (Encoder Y)             | (Encoder C)        | (пі-Д)               | (Hi-Z)            |

Table 6. TV Video Output (Note 23)

| (0411) | D4-D3) |

|--------|--------|

| (04H:  | D4-D3) |

| Mode               | RCA1-0 bit | Source of RCAVOUT pin |  |

|--------------------|------------|-----------------------|--|

| Shutdown (default) | 00         | (Hi-Z)                |  |

| Encoder CVBS       | 01         | ENCV pin              |  |

| Encoder CVBS       | 10         | ENCY pin              |  |

| (Reserved)         | 11         | -                     |  |

Table 7. RCA Video Output (Note 23)

Note 23. When input the video signals via the ENCRC pin, set CLAMP1-0 bits respectively.

### ■ Video Output Control (05H: D6-D0,)

Each video output can be set to Hi-Z individually via the control registers.

TVV: TVVOUT output control

TVR: TVRCOUT output control

TVG: TVGOUT output control

TVB: TVBOUT output control

RCAV: RCAVOUT output control

RCAV: TVFB output control

0: Hi-Z. (default)

1: Active.

### ■ Clamp and DC-restore Circuit Control (06H: D7-D3)

Each CVBS and Y input has a sync tip clamp circuit. The DC-restore circuit has two clamp voltages; 0.20V(typ) and 1.44V(typ) to support both RGB and YPbPr signal. They correspond to 0.10V(typ) and 0.72V(typ) at the SCART connector when matched by 75 $\Omega$  resistors. CLAMP1 and CLAMPB bits select the input circuit for both the ENCRC pin (Encoder Red/Chroma) and the ENCB pin (Encoder Blue), and CLAMP2 bit selects the input circuit for the ENCG pin. VCLP1-0 bits select the sync source of DC- restore circuit.

| CLAMPB | CLAMP1 | ENCRC Input Circuit               | ENCB Input Circuit                | note        |           |

|--------|--------|-----------------------------------|-----------------------------------|-------------|-----------|

| 0 0    |        | DC restore clamp active           | DC restore clamp active for RGB   |             | (default) |

|        | -      | (0.20V at sync timing/output pin) | (0.20V at sync timing/output pin) |             | ` '       |

| 0      | 1      | Biased                            | DC restore clamp active           | for Y/C     |           |

| 0      | 1      | (1.44V at sync timing/output pin) | (0.20V at sync timing output pin) | 101 1/C     |           |

| 1      | 0      | DC restore clamp active           | DC restore clamp active           | for Y/Pb/Pr |           |

| 1 0    |        | (1.44V at sync timing/output pin) | (1.44V at sync timing/output pin) | IOF I/PD/PF |           |

| 1      | 1      | (reserved)                        | (reserved)                        |             |           |

| CLAMP2 | ENCG Input Circuit                                           | note        |           |

|--------|--------------------------------------------------------------|-------------|-----------|

| 0      | DC restore clamp active<br>(0.20V at sync timing/output pin) | for RGB     | (default) |

| 1      | Sync tip clamp active<br>(0.20V at sync timing/output pin)   | for Y/Pb/Pr |           |

Table 8. DC-restore Control for Encoder Input

Note: When the VTV1-0 bits = "01" (source for TV = Encoder CVBS /RGB), TVG bit = "1" (TVG = active) and VCLP1-0 bits = "11" (DC restore source = ENCG), the sync tip is selected even if the CLAMP2 bit = "0".

Table 9. DC-restore Control for Encoder Green/Y Input

| VCLP1 | VCLP0 | Sync Source of DC Restore | ]         |

|-------|-------|---------------------------|-----------|

| 0     | 0     | ENCV                      | (default) |

| 0     | 1     | ENCY                      | ]         |

| 1     | 0     | (Reserved)                | ]         |

| 1     | 1     | ENCG                      |           |

Table 10. DC-restore Source Control

### 4. Blanking Control

The AK4710 supports Fast Blanking signals and Slow Blanking (Function Switching) signals for TV SCART.

### ■ Input/Output Control for Fast/Slow Blanking

FB: TV Fast Blanking output control (07H: D1-D0)

| Inj     | out     | Output                                  |

|---------|---------|-----------------------------------------|

| FB1 bit | FB0 bit | TVFB pin Output Level                   |

| 0       | 0       | 0V (default)                            |

| 0       | 1       | $2V$ <, $2.5V(typ)$ at $150\Omega$ load |

| 1       | 0       | (Reserved)                              |

| 1       | 1       | (Reserved)                              |

Table 11. TV Fast Blanking Output (Note: minimum load is 150Ω)

SBT1-0: TV Slow Blanking output control (07H: D3-D2)

| Inj         | out         | Output                |

|-------------|-------------|-----------------------|

| SBT1<br>bit | SBT0<br>bit | TVSB pin Output Level |

| 0           | 0           | <2V (default)         |

| 0           | 1           | 4.73V <, < 7V         |

| 1           | 0           | (Reserved)            |

| 1           | 1           | 10V<                  |

Table 12. TV Slow Blanking Output (Note: minimum load is  $10k\Omega$ )

### 5. Control Interface (I<sup>2</sup>C-bus Control)

#### 1. WRITE Operations

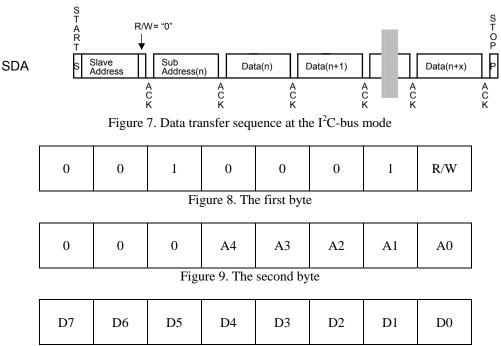

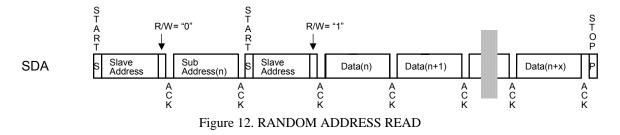

Figure 7 shows the data transfer sequence in I<sup>2</sup>C-bus mode. All commands are preceded by a START condition. A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition (Figure 13). After the START condition, a slave address is sent. This address is 7bits long followed by the eighth bit that is a data direction bit (R/W). The most significant seven bits of the slave address are fixed as "0010001". If the slave address match that of the AK4710, the AK4710 generates the acknowledge and the operation is executed. The master must generate the acknowledge-related clock pulse and release the SDA line (HIGH) during the acknowledge clock pulse (Figure 15). A "1" for R/W bit indicates that the read operation is to be executed. A "0" indicates that the write operation is to be executed. The second byte consists of the address for control registers of the AK4710. The format is MSB first, and those most significant 3-bits are fixed to zeros (Figure 9). The data after the second byte contain control data. The format is MSB first, 8bits (Figure 10). The AK4710 generates an acknowledge after each byte has been received. A data transfer is always terminated by a STOP condition generated by the master. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition (Figure 13).

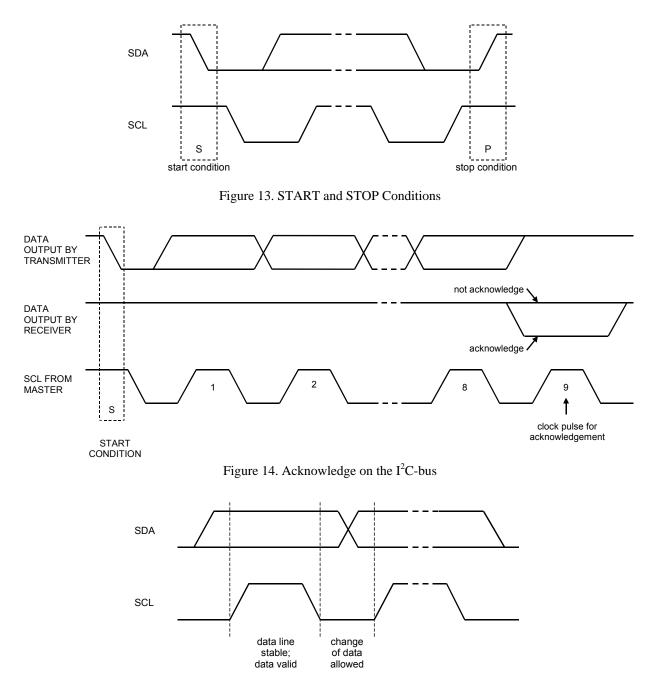

The AK4710 can execute multiple one byte write operations in a sequence. After receipt of the third byte, the AK4710 generates an acknowledge, and awaits the next data again. The master can transmit more than one byte instead of terminating the write cycle after the first data byte is transferred. After the receipt of each data, the internal address counter is incremented by one, and the next data is taken into next address automatically. If the address exceeds 0DH prior to generating the stop condition, the address counter will "roll over" to 00H and the previous data will be overwritten. The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (Figure 15) except for the START and the STOP condition.

Figure 10. Byte structure after the second byte

#### 2. READ Operations

Set R/W bit = "1" for READ operations. After transmission of data, the master can read the next address's data by generating an acknowledge instead of terminating the write cycle after the receipt the first data word. After the receipt of each data, the internal address counter is incremented by one, and the next data is taken into next address automatically. If the address exceeds 09H prior to generating the stop condition, the address counter will "roll over" to 00H and the previous data will be overwritten.

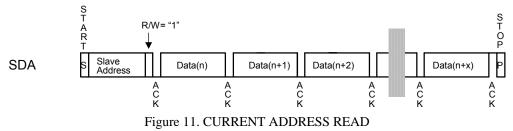

The AK4710 supports two basic read operations: CURRENT ADDRESS READ and RANDOM READ.

#### 2-1. CURRENT ADDRESS READ

The AK4710 contains an internal address counter that maintains the address of the last word accessed, incremented by one. Therefore, if the last access (either a read or write) was to address n, the next CURRENT READ operation would access data from the address n+1. After receipt of the slave address with R/W bit set to "1", the AK4710 generates an acknowledge, transmits 1byte data which address is set by the internal address counter and increments the internal address counter by 1. If the master does not generate an acknowledge to the data but generate the stop condition, the AK4710 discontinues transmission.

#### 2-2. RANDOM READ

Random read operation allows the master to access any memory location at random. Prior to issuing the slave address with the R/W bit set to "1", the master must first perform a "dummy" write operation. The master issues a start condition, slave address (R/W bit = "0") and then the register address to read. After the register address is acknowledge, the master immediately reissues the start condition and the slave address with the R/W bit set to "1". Then the AK4710 generates an acknowledge, 1-byte data and increments the internal address counter by 1. If the master does not generate an acknowledge to the data but generate the stop condition, the AK4710 discontinues transmission.

Figure 15. Bit transfer on the  $I^2C$ -bus

### Register Map

| Addr | Register Name        | D7     | D6    | D5    | D4     | D3     | D2   | D1   | D0   |

|------|----------------------|--------|-------|-------|--------|--------|------|------|------|

| 00H  | Control              | 0      | 0     | 0     | 0      | 1      | 0    | MUTE | 1    |

| 01H  | Switch               | 1      | 0     | 0     | 1      | MONO   | 1    | 0    | 1    |

| 02H  | Reserve              | 0      | 0     | 0     | 0      | 0      | 0    | 0    | 0    |

| 03H  | Zerocross            | 0      | 0     | CAL   | 0      | 0      | 1    | 1    | 1    |

| 04H  | Video switch         | 0      | 0     | 0     | RCA1   | RCA0   | 1    | VTV1 | VTV0 |

| 05H  | Video output enable  | 0      | TVFB  | 0     | RCAV   | TVB    | TVG  | TVR  | TVV  |

| 06H  | Video volume/clamp   | CLAMPB | VCLP1 | VCLP0 | CLAMP2 | CLAMP1 | 1    | 0    | 0    |

| 07H  | S/F Blanking control | 0      | 0     | 0     | 0      | SBT1   | SBT0 | FB1  | FB0  |

| 08H  | Reserve              | 0      | 0     | 0     | 0      | 0      | 0    | 0    | 0    |

| 09H  | Reserve              | 0      | 0     | 0     | 0      | 0      | 0    | 0    | 0    |

| 0AH  | Reserve              | 0      | 0     | 0     | 0      | 0      | 0    | 1    | 1    |

| 0BH  | Reserve              | 0      | 0     | 0     | 0      | 0      | 0    | 0    | 0    |

| 0CH  | Reserve              | 0      | 0     | 0     | 0      | 0      | 0    | 0    | 0    |

| 0DH  | Volume               | 0      | VOL3  | VOL2  | VOL1   | VOL0   | 1    | 1    | 1    |

When the PDN pin goes "L", the registers are initialized to their default values. While the PDN pin = "H", all registers can be accessed.

Do not write any data to the register over 0DH.

### Register Definitions

| Addr | Register Name | D7 | D6 | D5 | D4  | D3 | D2 | D1   | D0 |

|------|---------------|----|----|----|-----|----|----|------|----|

| 00H  | Control       | 0  | 0  | 0  | 0   | 1  | 0  | MUTE | 1  |

|      | R/W           |    |    |    | R/V | W  |    |      |    |

|      | Default       | 0  | 0  | 0  | 0   | 1  | 0  | 1    | 1  |

MUTE: Audio output control

0: Normal operation

1: ALL Audio outputs to GND (default)

| Addr | Register Name | D7 | D   | 5 | D5 | : | D4 |     | D3   |   | D2 |   | D1 | : | D0 |

|------|---------------|----|-----|---|----|---|----|-----|------|---|----|---|----|---|----|

| 01H  | Switch        | 1  | : 0 |   | 0  | : | 1  |     | MONO | : | 1  | : | 0  | : | 1  |

|      | R/W           |    |     |   |    |   |    | R/V | V    |   |    |   |    |   |    |

|      | Default       | 1  | 0   |   | 0  |   | 1  |     | 0    |   | 1  |   | 0  |   | 1  |

MONO: Mono select for TVOUTL/R pins

0: Stereo. (default)

1: Mono. (L+R)/2

| Addr | Register Name  | D7 | D6 | : | D5  | 1 | D4 | :   | D3 |   | D2 | : | D1 | : | D0 |

|------|----------------|----|----|---|-----|---|----|-----|----|---|----|---|----|---|----|

| 03H  | Volume Control | 0  | 0  | : | CAL |   | 0  |     | 0  | : | 1  | : | 1  | : | 1  |

|      | R/W            |    |    |   |     |   |    | R/W |    |   |    |   |    |   |    |

|      | Default        | 0  | 0  |   | 1   |   | 0  |     | 0  |   | 1  |   | 1  |   | 1  |

CAL: Offset calibration Enable

0: Offset calibration disable.

1: Offset calibration enable (default)

| Addr | Register Name | D7 |   | D6 | : | D5 |   | D4   | :   | D3   | : | D2 |   | D1   | : | D0   |

|------|---------------|----|---|----|---|----|---|------|-----|------|---|----|---|------|---|------|

| 04H  | Video switch  | 0  | : | 0  | : | 0  | : | RCA1 | :   | RCA0 | : | 1  | : | VTV1 | : | VTV0 |

|      | R/W           |    |   |    |   |    |   |      | R/W | Ι    |   |    |   |      |   |      |

|      | Default       | 0  | - | 0  |   | 0  | - | 1    | -   | 1    |   | 1  |   | 0    |   | 0    |

VTV1-0: Selector for TV video output Refer to Table 6.

RCA1-0: Selector for RCA video output Refer to Table 7.

| Addr | Register Name | D7 | : | D6   | : | D5 | D4         | : | D3  | - : | D2  | - | D1  | D0  |

|------|---------------|----|---|------|---|----|------------|---|-----|-----|-----|---|-----|-----|

| 05H  | Output Enable | 0  | : | TVFB | : | 0  | RCAV       | : | TVB | :   | TVG | : | TVR | TVV |

|      | R/W           |    |   |      |   |    | <b>R</b> / | W |     |     |     |   |     |     |

|      | Default       | 0  |   | 0    | ł | 0  | 0          | ł | 0   |     | 0   |   | 0   | 0   |

TVV: TVVOUT output control TVR: TVRCOUT output control TVG: TVGOUT output control TVB: TVBOUT output control RCAV: RCAVOUT output control TVFB: TVFB output control 0: Hi-Z (default) 1: Active.

| Addr | Register Name | D7     | D6    | D5    | D4     | D3     | D2 | D1 | D0 |

|------|---------------|--------|-------|-------|--------|--------|----|----|----|

| 06H  | Video volume  | CLAMPB | VCLP1 | VCLP0 | CLAMP2 | CLAMP1 | 1  | 0  | 0  |

|      | R/W           |        |       |       | R/V    | N      |    |    |    |

|      | Default       | 0      | 0     | 0     | 0      | 0      | 1  | 0  | 0  |

CLAMPB, CLAMP2-1: Clamp control. Refer to Table 8 and Table 9.

VCLP1-0: DC restore source control

00: ENCV pin (default)

01: ENCY pin

10: (Reserved)

11: ENCG pin

| Addr | Register Name | D7 | : | D6 | : | D5 |   | D4 | :   | D3   | : | D2   | : | D1  | : | D0  |

|------|---------------|----|---|----|---|----|---|----|-----|------|---|------|---|-----|---|-----|

| 07H  | S/F Blanking  | 0  | : | 0  | : | 0  |   | 0  | :   | SBT1 | : | SBT0 | : | FB1 | : | FB0 |

|      | R/W           |    |   |    |   |    |   |    | R/W |      |   |      |   |     |   |     |

|      | Default       | 0  |   | 0  |   | 0  | - | 0  |     | 0    |   | 0    |   | 0   |   | 0   |

FB1-0: TV Fast Blanking output control (for TVFB pin)

00: 0V (default)

01: 2V<, 2.5V(typ) at 150 $\Omega$  load

10: (Reserved)

11: (Reserved)

SBT1-0: TV Slow Blanking output control (for TVSB pin. minimum load is 10kΩ.)

$00: < 2V \; (default)$

01: 4.73V <, < 7V

10: (Reserved)

11: 10V <

| Addr | Register Name | D7 | <br>D6 | - | D5   | D2 |     | D3   |   | D2 | • | D1 | D0    |

|------|---------------|----|--------|---|------|----|-----|------|---|----|---|----|-------|

| 0DH  | Main volume   | 0  | VOL3   | ÷ | VOL2 | VO | .1  | VOL0 | - | 1  |   | 1  | <br>1 |

|      | R/W           |    |        |   |      |    | R/V | V    |   |    |   |    |       |

|      | Default       | 0  | 0      | 1 | 0    | 1  | :   | 1    | 1 | 1  |   | 1  | 1     |

VOL3-0: Volume control

Those registers control both Lch and Rch of Volume.

1011: Volume gain = +24dB

1010: Volume gain = +21dB

1001: Volume gain = +18dB

1000: Volume gain = +15dB

- 0111: Volume gain = +12dB

- 0110: Volume gain = +9dB

0101: Volume gain = +6dB

0100: Volume gain = +3dB

0011: Volume gain = +0dB (default)

0010: Volume gain = -3dB

- 0001: Volume gain = -6dB

- 0000: MUTE

### SYSTEM DESIGN

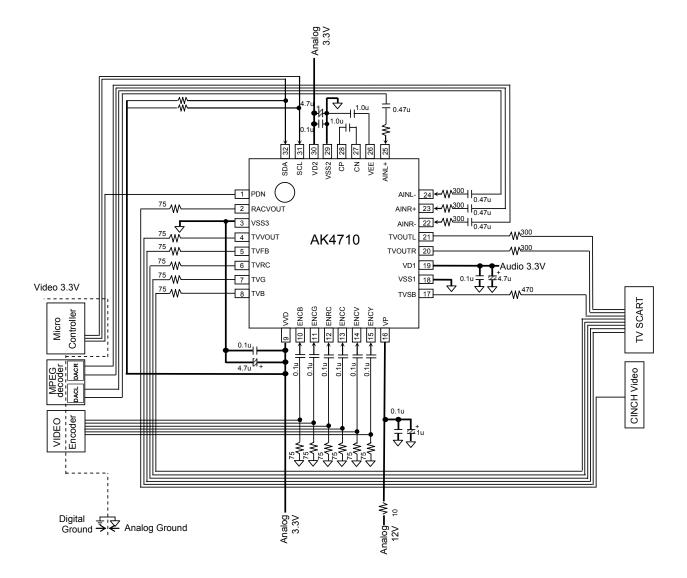

Figure 16 shows the system connection diagram example. An evaluation board (AKD4710) demonstrates application circuits, the optimum layout, power supply arrangements and measurement results.

Figure 16. Typical Connection Diagram

### ■ Grounding and Power Supply Decoupling

VD1, VD2, VP, VVD, VSS1, VSS2 and VSS3 should be supplied from analog supply unit with low impedance and be separated from system digital supply. An electrolytic capacitor  $4.7\mu$ F parallel with a  $0.1\mu$ F ceramic capacitor should be attached to VD1, VD2, VVD, VSS1, VSS2 and VSS3 pin to eliminate the effects of high frequency noise. The  $0.1\mu$ F ceramic capacitor should be placed as near to VD1 (VD2, VVD) as possible.

The VP pin must be connected to the Analogue 12V power supply via a 10ohm resistor and with a  $0.1\mu$ F ceramic capacitor in parallel with a  $1\mu$ F electrolytic capacitor to VSS1, as shown in Figure 16.

### Analog Audio Outputs

The analog outputs are also single-ended and centered on 0V(typ.). The output signal range is typically 2Vrms .

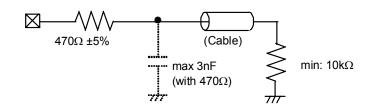

#### ■ Slow Blanking pins

The Slow Blanking Pin must have a 4700hm  $\pm 5\%$  series resistor.

### Asahi **KASEI**

### External Circuit Example

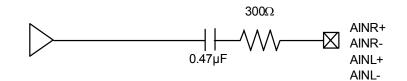

The analog audio input pin must have 300ohm series resistor and 0.47uF capacitor.

Analog Audio Input pin

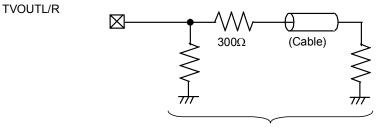

Analog Audio Output pin

Total > 4.5k $\Omega$

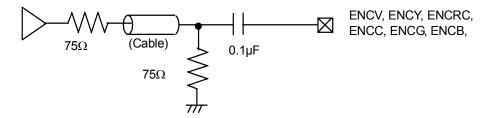

Analog Video Input pin

Analog Video Output pin

### Asahi**KASEI**

Slow Blanking pin

TVSB

Fast Blanking Output pin

### PACKAGE

## 32pin QFN (Unit: mm)

### Package & Lead frame material

Package molding compound:EpoxyLead frame material:CuLead frame surface treatment:Solder (Pb free) plate

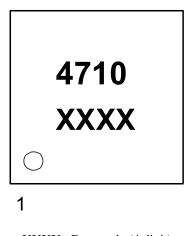

### MARKING

XXXX : Date code (4 digit) Pin #1 indication

#### **IMPORTANT NOTICE**

- These products and their specifications are subject to change without notice. When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei Microdevices Corporation (AKM) or authorized distributors as to current status of the products.

- Descriptions of external circuits, application circuits, software and other related information contained in this document are provided only to illustrate the operation and application examples of the semiconductor products. You are fully responsible for the incorporation of these external circuits, application circuits, software and other related information in the design of your equipments. AKM assumes no responsibility for any losses incurred by you or third parties arising from the use of these information herein. AKM assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of such information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components<sub>Note1</sub> in any safety, life support, or other hazard related device or system<sub>Note2</sub>, and AKM assumes no responsibility for such use, except for the use approved with the express written consent by Representative Director of AKM. As used here:

Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

• It is the responsibility of the buyer or distributor of AKM products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.