#### austriamicrosystems AG

is now

## ams AG

The technical content of this austriamicrosystems datasheet is still valid.

#### **Contact information:**

Headquarters: ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten, Austria Tel: +43 (0) 3136 500 0 e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

#### Datasheet

#### AS1713 Difference Amplifier, 10MHz, 10V/µs, Rail-to-Rail I/O with Shutdown

#### **1** General Description

The AS1713 is a low cost cmos difference amplifier providing extended common mode voltage range for a single rail 5V supply. Resistor trimming during final test ensures a typical common mode rejection of 60dB. Low input bias currents, 10MHz gain bandwidth, low total harmonic distortion (THD) and a rail-to-rail output drive capability of typically 200mA (@ 5V supply) provide support for a number of signal processing applications such as audio line receivers, ground loop breakers and current sensing. Linearity is suitable for 12bit ADC measurement.

A classical single amplifier approach ensures that the differential gain is determined by a simple ratio of two internal resistors. A fixed gain of x1 is available.

Single ended input resistance is equalised (10k $\Omega$  ±20%) at each input terminal. This feature provides additional common mode rejection when long balanced input cables connect at the input.

A EN pin reduces the quiescent current of the device.

#### 2 Key Features

- Constant Output Drive Capability: 50mA

- Rail-to-Rail Input and Output

- Supply Current: 1.6mA

- Single-Supply Operation: 2.7 to 5.5V

- Voltage Gain: 1

- Gain-Bandwidth Product: 10MHz

- High Slew Rate: 10V/µs

- Power-Supply Rejection Ratio: 70dB

- Common Mode Rejection Ratio: 60dB

- No Phase Reversal for Overdriven Inputs

- Unity-Gain Stable for Capacitive Loads: Up to 100pF

- Shutdown Mode Current: 1nA

- MLPD (2x2mm) 8-pin package

#### 3 Applications

The device is ideal for headphone amplifiers with ground interference rejection, infotainment high drive audio line buffers with ground interference rejection, audio differential-to-single-ended conversion and instrumentation amplifier back-end.

#### VDD INN R1 INN R1 INN R2 I

#### Figure 1. AS1713 - Block Diagram

#### 4 Pinout

#### **Pin Assignments**

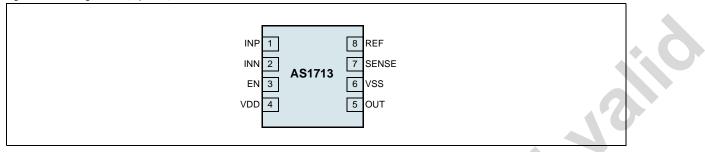

Figure 2. Pin Assignments (Top View)

#### **Pin Descriptions**

Table 1. Pin Descriptions

| 1   2   3   4   5   6   7   8           | INP<br>INN<br>EN<br>VDD<br>OUT | Non-inverting Input.     Inverting Input.     Active-Low Enable Input. A logic low on this pin shuts down the device.     Vss: device in shutdown.     VDD: normal operation.     Positive Supply Input. |

|-----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>4<br>5<br>6<br>7<br>8              | EN<br>VDD                      | Active-Low Enable Input. A logic low on this pin shuts down the device.<br>Vss: device in shutdown.<br>VDD: normal operation.                                                                            |

| 4<br>5<br>6<br>7<br>8                   | VDD                            | Vss: device in shutdown.<br>VDD: normal operation.                                                                                                                                                       |

| 4<br>5<br>6<br>7<br>8                   | VDD                            | VDD: normal operation.                                                                                                                                                                                   |

| 5 6<br>7 8                              |                                |                                                                                                                                                                                                          |

| 5 6<br>7 8                              |                                | Depitive Supply Input                                                                                                                                                                                    |

| 6 / / / / / / / / / / / / / / / / / / / | OUT                            | Positive Supply input.                                                                                                                                                                                   |

| 7 8                                     |                                | Amplifier Output.                                                                                                                                                                                        |

| 8                                       | VSS                            | Negative Supply Input. This pin must be connected to ground in single-supply applications.                                                                                                               |

|                                         | SENSE                          | Sense Input. Ground this pin when external inverting gain control is required.                                                                                                                           |

|                                         | REF                            | Reference Input. Reference to non-inverting input resistor network.                                                                                                                                      |

|                                         |                                |                                                                                                                                                                                                          |

|                                         |                                |                                                                                                                                                                                                          |

#### 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 2. Absolute Maximum Ratings Parameter Min Max Units Comments **Electrical Parameters** Supply Voltage (VDD to Vss) -0.3 +7 V Vss Vdd Supply Voltage (All Other Pins) V - 0.3 + 0.3Output Short-Circuit Duration to VDD or VSS 1 S Electrostatic Discharge Electrostatic Discharge HBM 1 kV Norm: MIL 883 E method 3015 **Temperature Ranges and Storage Conditions** Thermal Resistance OJA 33 °C/W on PCB Storage Temperature Range °С -65 +150 Junction Temperature +150 °C The reflow peak soldering temperature (body temperature) specified is in accordance with *IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity* Package Body Temperature ٥C Classification for Non-Hermetic Solid State Surface +260 Mount Devices". The lead finish for Pb-free leaded packages is matte tin (100% Sn). Humidity non-condensing 5 85 % Moisture Sensitive Level Represents a max. floor life time of unlimited 1

### 6 Electrical Characteristics

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

#### **DC Electrical Characteristics**

VDD = 2.7V, VSS = 0V, VCM = VDD/2, VOUT = VDD/2, RLOAD = Infinite, VEN = VDD, Typical values at TAMB = 25°C (unless otherwise specified).

Table 3. DC Electrical Characteristics

| Symbol     | Parameter                       | Condition                                              |                             | Min  | Тур          | Max               | Unit |

|------------|---------------------------------|--------------------------------------------------------|-----------------------------|------|--------------|-------------------|------|

| Тамв       | Operating Temperature Range     |                                                        |                             | -40  |              | +85               | °C   |

| Vdd        | Supply Voltage Range            | Inferred from Power Supply Rejection Ratio Test        |                             | 2.7  |              | 5.5               | V    |

| Voffset    | Input Offset Voltage            |                                                        |                             | -1.5 |              | +1.5              | mV   |

| Rsein      | Single-Ended Input Resistance   |                                                        |                             | 8    | 10           | 12                | kΩ   |

| Vсм        | Common Mode Input Voltage Range | Inferred from Common Mode Rejection Ratio <sup>1</sup> |                             | Vss  |              | Vdd               | V    |

| CMRR       | Common Mode Rejection Ratio     | VSS < VCM < VDD                                        |                             | 45   | 60           |                   | dB   |

| PSRR       | Power Supply Rejection Ratio    | VDD = 2.7 to 5.5V                                      |                             | 60   | 70           |                   | dB   |

| Rout       | Shutdown Output Impedance       | VEN = 0V                                               |                             |      | 130          |                   | Ω    |

| Vout-shdnn | Shutdown Output Voltage         | Ven = 0V, Rload = $2k\Omega$ to VDD                    |                             |      | 170          | 400               | mV   |

|            | Output Voltage Swing            | VDD - VOH OF<br>VOL - VSS                              | RLOAD = $32\Omega$          |      | 350          | 650               |      |

|            |                                 |                                                        | $RLOAD = 200\Omega$         |      | 70           | 120               | mV   |

|            |                                 |                                                        | $RLOAD = 2k\Omega$          |      | 9            | 20                |      |

| Vout       | Output Voltage                  | VDD - VOH or<br>VOL - VSS                              | ILOAD = 10mA,<br>VDD = 2.7V |      | 55           | 100               | mV   |

|            |                                 |                                                        | Iload = 50mA,<br>Vdd = 5V   |      | 100          | 200               | IIIV |

| lout       |                                 | VDD = 2.7V,<br>V- = VCM, V+ = VCM±100mV                |                             |      | 100          |                   | mA   |

|            | Output Source/Sink Current      | VDD = 5.0V,<br>V- = VCM, V+ = VCM±100mV                |                             |      | 200          |                   |      |

| IDD        | Quieseent Supply Current        | Vdd = 2.7V, Vcm = Vdd/2                                |                             |      | 1.6          | 3.2               | mA   |

|            | Quiescent Supply Current        | VDD = 5.0V, VCM = VDD/2                                |                             |      | 2.3          | 4.6               |      |

| IDD-SHDNN  | Shutdown Supply Current         | Ven = 0V, Vdd = 2.7V                                   |                             |      | 1            | 2000 <sup>1</sup> | nA   |

|            | EN Logic Threshold              | Shutdown Mode                                          |                             |      | Vss +<br>0.3 |                   | V    |

|            | LN Logic Theshold               | Normal Operation                                       |                             |      | VDD -<br>0.3 |                   |      |

|            | EN Input Bias Current           | VSS < VEN < VDD                                        |                             |      | 50           |                   | pА   |

# 1. Guaranteed by design.

#### **AC Electrical Characteristics**

VDD = 2.7V, VSS = 0V, VCM = VDD/2, VOUT = VDD/2, RLOAD = Infinite, VEN = VDD, TAMB = -40 to +85°C. Typical values at TAMB = 25°C. Table 4. AC Electrical Characteristics

| Symbol         | Parameter Conditions                    |                                        | Min | Тур      | Max | Units  |

|----------------|-----------------------------------------|----------------------------------------|-----|----------|-----|--------|

| GBWP           | Gain-Bandwidth Product                  | Gain-Bandwidth Product VCM = VDD/2     |     | 4        |     | MHz    |

| f <sub>C</sub> | Cut-off Frequency                       |                                        |     | 8.5      |     | MHz    |

| SR             | Slew Rate                               |                                        |     | 5        |     | V/µs   |

| PM             | Phase Margin                            | Phase Margin                           |     | 60       |     | deg    |

| GM             | Gain Margin <sup>1</sup>                |                                        |     | 10       |     | dB     |

| THD+N          | Total Harmonic Distortion<br>Plus Noise | f = 10kHz, Vout = 2Vp-p, Avcl = 1V/V   |     | 60       |     | dBc    |

| Cin            | Input Capacitance                       |                                        |     | 2        |     | pF     |

| en             | Voltage-Noise Density <sup>1</sup>      | f = 1kHz<br>f = 10kHz                  |     | 40<br>30 |     | nV/√Hz |

|                | Capacitive-Load Stability               | AvcL = 1V/V, no sustained oscillations |     | 100      |     | pF     |

| tSHDN          | Shutdown Time                           |                                        |     | 1        |     | μs     |

| <b>TENABLE</b> | Enable Time from Shutdown               |                                        |     | 7        |     | μs     |

| ton            | Power-Up Time                           |                                        |     | 20       |     | ns     |

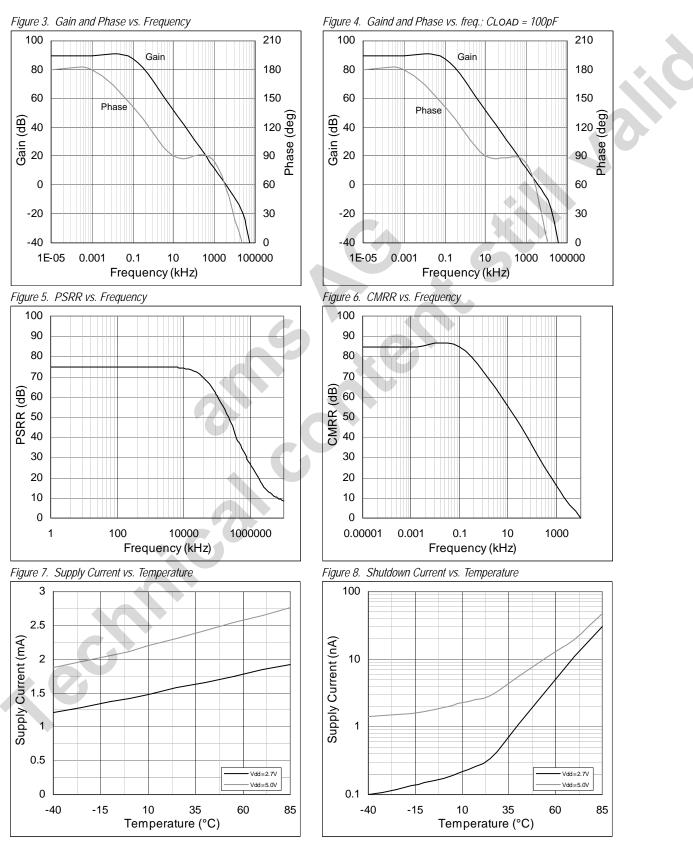

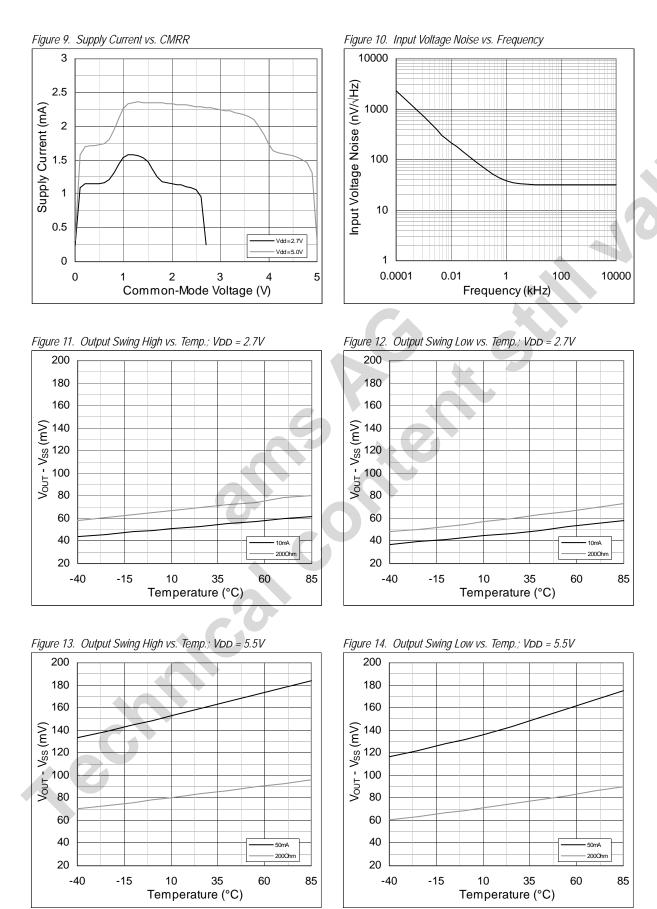

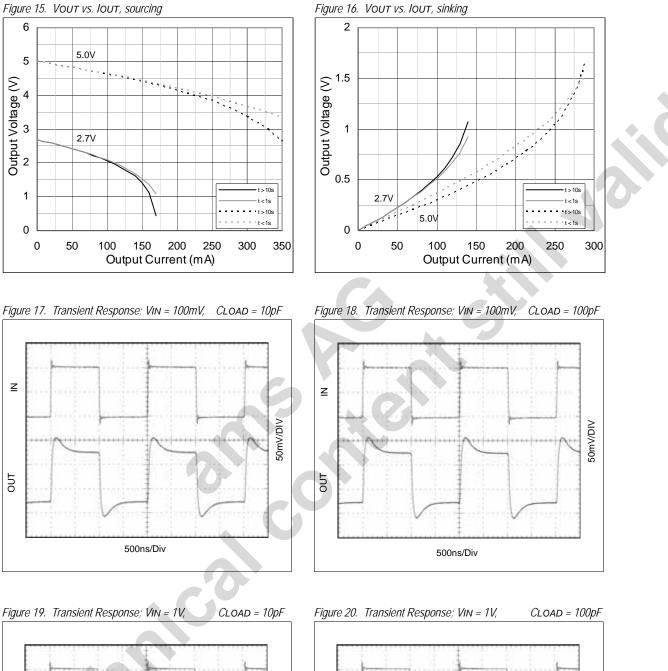

#### 7 Typical Operating Characteristics

VDD = 2.7V; VSS = 0V, VCM = VDD/2, VOUT = VDD/2, RLOAD = ∞, VEN = VDD TAMB = +25°C (unless otherwise specified).

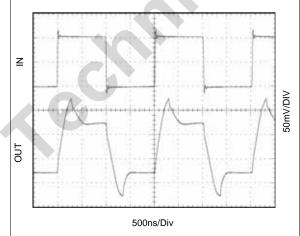

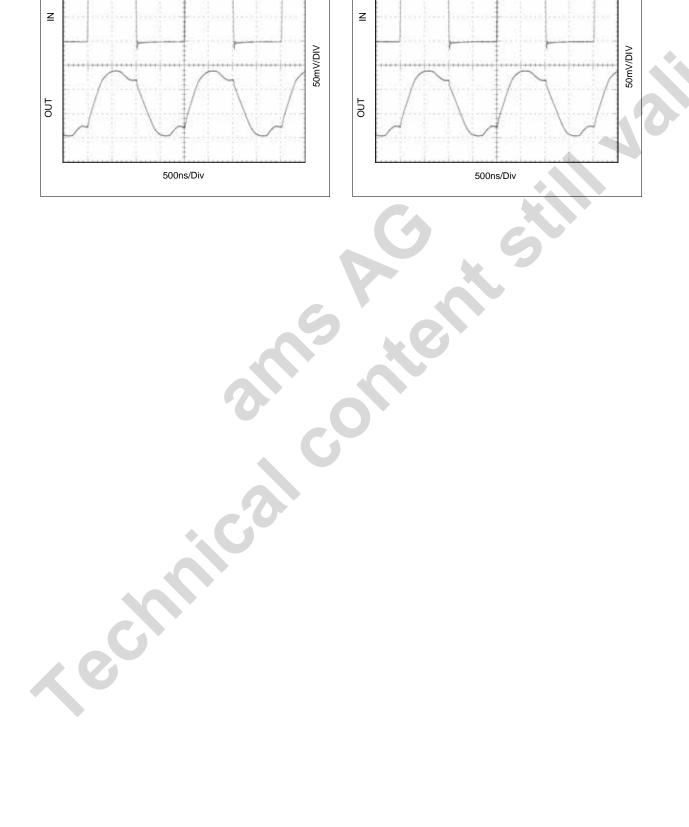

Figure 22. Transient Response; VIN = 2V,

*austriamicro*systems

CLOAD = 100pF

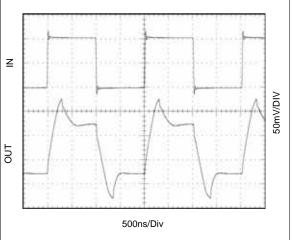

Figure 21. Transient Response; VIN = 2V,

CLOAD = 10pF

(EQ 1

#### 8 Application Information

#### Ground Loop Interference Suppression:

In real life situations the signal source and the amplifier are often located a distance apart, but still share the same ground arrangement with a number of other circuits. The ground system is never perfect as it has a small distributed resistance, capacitance and inductance. Thus, the ground appears as a distributed impedance.

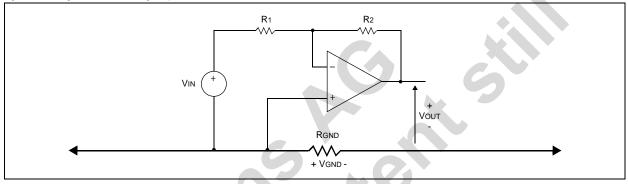

As a various current flow into and out of the ground system exists, a small voltage drop will inevitably occur, causing different voltages within the ground. In Figure 23 and Figure 24, RGND denotes the ground resistance between the input signal ground and the output signal ground. The voltage drop across RGND should ideally have no effect on individual circuit performance.

In the single ended inverting amplifier shown in Figure 23, the amplifier sees VIN and VGND in series, so the amplifier output is:

$$VOUT = - [R_2/R_1] [VIN+VGND]$$

VGND is part of the output expression and is known as ground loop interference, ground bounce or even common impedance crosstalk. In some situations this interference signal can be close to or the same value as the wanted input signal such as in sensor applications.

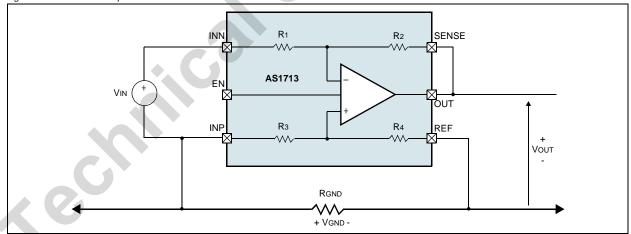

A difference amplifier is a simple method used to reduce the effect of ground interference. VIN is regarded as a differential input signal, and VGND a common mode signal. From Figure 24, the amplifier output is:

$$VOUT = - [R_2/R_1] VIN$$

(EQ 2)

Figure 24. Difference Amplifier

The additional cost of extra matched resistors is offset by the rejection of the unwanted common mode ground interference.

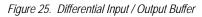

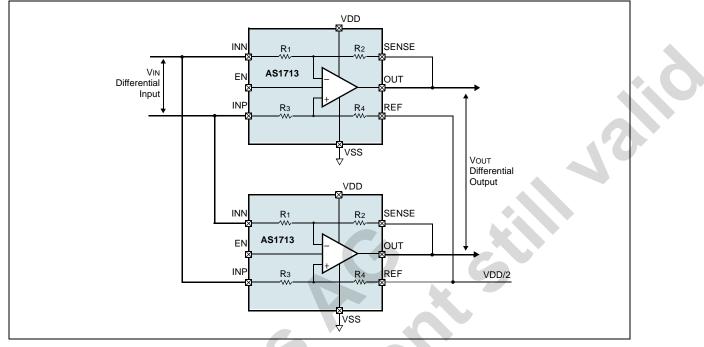

#### Differential Input / Output Buffer

#### Rail-to-Rail Input Stage

The AS1713 CMOS op amps have parallel connected n- and p-channel differential input stages that combine to accept a common-mode range extending to both supply rails. The n-channel stage is active for common-mode input voltages typically greater than (VSS + 1.2V), and the p-channel stage is active for common-mode input voltages typically less than (VDD - 1.2V).

#### Rail-to-Rail Output Stage

< ecnn\*

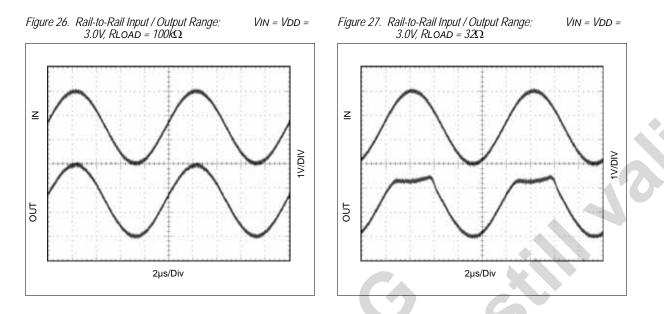

The minimum output is within millivolts of ground for single- supply operation, where the load is referenced to ground (Vss). Figure 26 shows the input voltage range and the output voltage swing of an AS1713 connected as a voltage follower. The maximum output voltage swing is load dependent although it is guaranteed to be within 500mV of the positive rail (VDD = 2.7V) even with maximum load ( $32\Omega$  to ground) as shown in Figure 27.

Note: The absolute maximum ratings (see page 3) for power dissipation and output short-circuit duration (10s, max) must be adhered since the output current can exceed 200mA (see Typical Operating Characteristics on page 6).

#### Shutdown

When EN is pulled to low, the supply current drops to 0.5µA, the amplifier is disabled and the output is driven to Vss. Pulling EN to high enables the amplifier. When exiting shutdown, there is a 6µs delay before the amplifier output becomes active.

Note: Because the output is actively driven to Vss in shutdown, any pullup resistor on the output causes a current drain from the supply.

#### Power-Up

The AS1713 typically settle within 5µs after power-up.

#### Power Supplies and Layout

The AS1713 can operate from a single 2.7V to 5.5V supply or from dual  $\pm$ 1.35V to  $\pm$ 2.5V supplies. Good design improves device performance by decreasing the amount of stray capacitance at the op amp inputs/outputs.

- For single-supply operation, bypass the power supply with a 0.1µF ceramic capacitor.

- For dual-supply operation, bypass each supply to ground.

- Decrease stray capacitance by placing external components close to the op amp pins, minimizing trace and lead lengths.

#### 9 Package Drawings and Markings

Figure 28. MLPD (2x2mm) 8-pin Marking

AS1713 Datasheet - Package Drawings and Markings

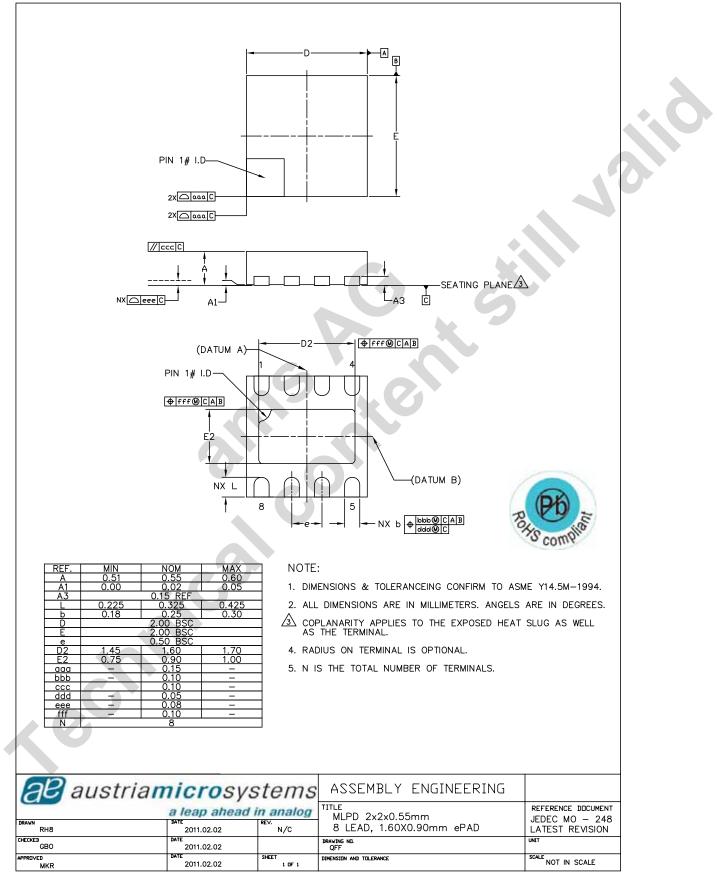

Figure 29. MLPD (2x2mm) 8-pin Package

Revision 1.03

#### 10 Ordering Information

The device is available as the standard products shown in Table 5.

Table 5. Ordering Information

| Ordering Code | Marking | Description                                                            | Delivery Form | Package            |

|---------------|---------|------------------------------------------------------------------------|---------------|--------------------|

| AS1713-BTDT   | ABB     | Difference Amplifier, 10MHz, 10V/µs,<br>Rail-to-Rail I/O with Shutdown | Tape and Reel | MLPD (2x2mm) 8-pin |

**Note:** All products are RoHS compliant.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

For further information and requests, please contact us mailto:sales@austriamicrosystems.com or find your local distributor at http://www.austriamicrosystems.com/distributor

#### Copyrights

Copyright © 1997-2011, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

#### Headquarters

austriamicrosystems AG Tobelbaderstrasse 30 A-8141 Unterpremstaetten, Austria Tel: +43 (0) 3136 500 0

Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit: http://www.austriamicrosystems.com/contact