### 4M×4 CMOS DRAM (Fast Page) 3.3V Family

#### **Features**

- Organization: 4,194,304 words × 4 bits

- High speed

- 50/60 ns  $\overline{RAS}$  access time

- 25/30 ns column address access time

- 12/15 ns  $\overline{\text{CAS}}$  access time

- Low power consumption

- Active: 500 mW max

- Standby: 3.6 mW max, CMOS I/O

- Fast page mode

- Refresh

- 2048 refresh cycles, 32 ms refresh interval

- RAS-only or CAS-before-RAS refresh or self-refresh

- TTL-compatible, three-state I/O

- JEDEC standard package

- 300 mil, 24/26-pin SOJ

- 3.3V power supply

- Latch-up current ≥ 200 mA

- ESD protection  $\geq$  2000 volts

- Industrial and commercial temperature available

#### Pin arrangement

| SOJ             |            |                                      | TSOP*                                                                      |            |    |  |  |  |

|-----------------|------------|--------------------------------------|----------------------------------------------------------------------------|------------|----|--|--|--|

| V <sub>CC</sub> | AS4LC4M4F1 | 26                                   | V <sub>CC</sub>                                                            | AS4LC4M4F1 | 19 |  |  |  |

| A10             | AS4LC      | 19 A8 18 A7 17 A6 16 A5 15 A4 14 GND | A10 = 8<br>A0 = 9<br>A1 = 10<br>A2 = 11<br>A3 = 12<br>V <sub>CC</sub> = 13 | AS4LC      | 26 |  |  |  |

\*TSOP availability to be determined

#### Pin designation

| in designation |                       |  |  |  |  |

|----------------|-----------------------|--|--|--|--|

| Pin(s)         | Description           |  |  |  |  |

| A0 to A10      | Address inputs        |  |  |  |  |

| RAS            | Row address strobe    |  |  |  |  |

| CAS            | Column address strobe |  |  |  |  |

| WE             | Write enable          |  |  |  |  |

| I/O0 to I/O3   | Input/output          |  |  |  |  |

| ŌĒ             | Output enable         |  |  |  |  |

| $v_{cc}$       | Power                 |  |  |  |  |

| GND            | Ground                |  |  |  |  |

#### Selection guide

|                                                     | Symbol           | AS4LC4M4F1-50 | AS4LC4M4F1-60 | Unit |

|-----------------------------------------------------|------------------|---------------|---------------|------|

| Maximum RAS access time                             | t <sub>RAC</sub> | 50            | 60            | ns   |

| Maximum column address access time                  | t <sub>CAA</sub> | 25            | 30            | ns   |

| Maximum CAS access time                             | t <sub>CAC</sub> | 12            | 15            | ns   |

| Maximum output enable $(\overline{OE})$ access time | t <sub>OEA</sub> | 13            | 15            | ns   |

| Minimum read or write cycle time                    | t <sub>RC</sub>  | 80            | 100           | ns   |

| Minimum fast page mode cycle time                   | t <sub>PC</sub>  | 25            | 30            | ns   |

| Maximum operating current                           | I <sub>CC1</sub> | 120           | 110           | mA   |

| Maximum CMOS standby current                        | I <sub>CC5</sub> | 1.0           | 1.0           | mA   |

#### Functional description

The AS4LC4M4F1 is a high performance 16-megabit CMOS Dynamic Random Access Memory (DRAM) device organized as 4,194,304 words × 4 bits. The device is fabricated using advanced CMOS technology and innovative design techniques resulting in high speed, extremely low power and wide operating margins at component and system levels. The Alliance 16Mb DRAM family is optimized for use as main memory in PC, workstation, router and switch applications.

This device features a high speed page-mode operation where read and write operations within a single row (or page) can be executed at very high speed by toggling column addresses within that row. Row and column addresses are alternately latched into input buffers using the falling edge of RAS and CAS inputs respectively. Also, RAS is used to make the column address latch transparent, enabling application of column addresses prior to CAS assertion.

Refresh on the 2048 address combinations of A0 to A10 must be performed every 32 ms using:

- RAS-only refresh: RAS is asserted while CAS is held high. Each of the 2048 rows must be strobed. Outputs remain high impedence.

- Hidden refresh:  $\overline{CAS}$  is held low while  $\overline{RAS}$  is toggled. Refresh address is generated internally. Outputs remain low impedence with previous valid data.

- CAS-before-RAS refresh (CBR): CAS is asserted prior to RAS. Refresh address is generated internally. Outputs are high-impedence (OE and WE are don't care).

- Normal read or write cycles refresh the row being accessed.

- Self-refresh cycles

The AS4LC4M4F1 is available in the standard 24/26-pin plastic SOJ. TSOP 24/26-pin availability is to be determined. The AS4LC4M4F1 operates with a single power supply of  $3.3V \pm 0.3V$  and provides TTL compatible inputs and outputs.

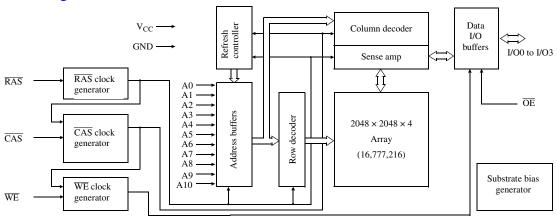

#### Logic block diagram for 2K refresh

#### Recommended operating conditions

| recommended operating conditions |            |                   |       |         |                      |      |  |  |  |  |

|----------------------------------|------------|-------------------|-------|---------|----------------------|------|--|--|--|--|

| Parameter                        |            | Symbol            | Min   | Nominal | Max                  | Unit |  |  |  |  |

| C                                |            | V <sub>CC</sub>   | 3.0   | 3.3     | 3.6                  | V    |  |  |  |  |

| Supply voltage                   |            | GND               | 0.0   | 0.0     | 0.0                  | V    |  |  |  |  |

| T 1.                             |            | V <sub>IH</sub>   | 2.0   | -       | V <sub>CC+0.5V</sub> | V    |  |  |  |  |

| Input voltage                    |            | $V_{\mathrm{IL}}$ | -0.5† | -       | 0.8                  | V    |  |  |  |  |

| A 11                             | Commercial | т                 | 0     | -       | 70                   | °C   |  |  |  |  |

| Ambient operating temperature    | Industrial | $T_A$             | -40   | -       | 85                   | °C   |  |  |  |  |

$<sup>^{\</sup>dagger}V_{II}$  min -3.0V for pulse widths less than 5 ns. Recommended operating conditions apply throughout this document unlesss otherwise specified.

# Absolute maximum ratings

| Parameter                     | Symbol              | Min  | Max      | Unit     |

|-------------------------------|---------------------|------|----------|----------|

| Input voltage                 | V <sub>in</sub>     | -1.0 | 4.6      | V        |

| Input voltage (DQs)           | $V_{DQ}$            | -1.0 | 4.6      | V        |

| Power supply voltage          | V <sub>CC</sub>     | -1.0 | 4.6      | V        |

| Storage temperature (plastic) | T <sub>STG</sub>    | -55  | 150      | °C       |

| Soldering temperature × time  | T <sub>SOLDER</sub> | _    | 260 × 10 | °C × sec |

| Power dissipation             | $P_{\mathrm{D}}$    | _    | 0.432    | W        |

| Short circuit output current  | I <sub>out</sub>    | _    | 50       | mA       |

# DC electrical characteristics

|                                                       |                  |                                                                                                                                                   |     | 50  | -6  | 50  |      |       |

|-------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|------|-------|

| Parameter                                             | Symbol           | Test conditions                                                                                                                                   | Min | Max | Min | Max | Unit | Notes |

| Input leakage current                                 | ${ m I}_{ m IL}$ | $0V \le V_{in} \le +V_{cc}(max)$<br>Pins not under test = $0V$                                                                                    | -5  | +5  | -5  | +5  | μΑ   |       |

| Output leakage current                                | $I_{OL}$         | $D_{OUT}$ disabled, $0V \le V_{out} \le + V_{cc}(max)$                                                                                            | -5  | +5  | -5  | +5  | μΑ   |       |

| Operating power supply current                        | I <sub>CC1</sub> | CAS, Address cycling; t <sub>RC</sub> =min                                                                                                        | -   | 120 | -   | 110 | mA   | 1,2   |

| TTL standby power supply current                      | $I_{CC2}$        | $\overline{RAS} = \overline{CAS} \ge V_{IH}$                                                                                                      | I   | 2.0 | I   | 2.0 | mA   |       |

| Average power supply current, RAS refresh mode or CBR | $I_{CC3}$        | $\overline{RAS}$ cycling, $\overline{CAS} \ge V_{IH}$ , $t_{RC} = \min \text{ of } \overline{RAS} \text{ low after } \overline{CAS} \text{ low.}$ | _   | 120 | _   | 110 | mA   | 1     |

| Fast page mode average power supply current           | $I_{CC4}$        | $\overline{RAS} = V_{IL}$ , $\overline{CAS}$ , address cycling: $t_{HPC} = min$                                                                   | _   | 90  | _   | 80  | mA   | 1, 2  |

| CMOS standby power supply current                     | I <sub>CC5</sub> | $\overline{RAS} = \overline{CAS} = V_{CC} - 0.2V$                                                                                                 | ı   | 2.0 | 1   | 2.0 | mA   |       |

| Output voltage                                        | $V_{OH}$         | $I_{OUT} = -2.0 \text{ mA}$                                                                                                                       | 2.4 | ı   | 2.4 | _   | V    |       |

| Output voltage                                        | $V_{OL}$         | $I_{OUT} = 2.0 \text{ mA}$                                                                                                                        | _   | 0.4 | _   | 0.4 | V    |       |

| CAS   before   RAS   refresh     current              | $I_{CC6}$        | $\overline{RAS}$ , $\overline{CAS}$ cycling, $t_{RC} = \min$                                                                                      | I   | 120 | I   | 110 | mA   |       |

| Self refresh current                                  | I <sub>CC7</sub> | $\overline{RAS} = \overline{CAS} \le 0.2v,$ $\overline{WE} - \overline{OE} \ge V_{CC} - 0.2V,$ all other inputs at 0.2V or $V_{CC}$ - 0.2V        | -   | 0.6 | -   | 0.6 | mA   |       |

# AC parameters common to all waveforms

|                  |                                  |     | -50 -60 |     |     |      |       |

|------------------|----------------------------------|-----|---------|-----|-----|------|-------|

| Symbol           | Parameter                        | Min | Max     | Min | Max | Unit | Notes |

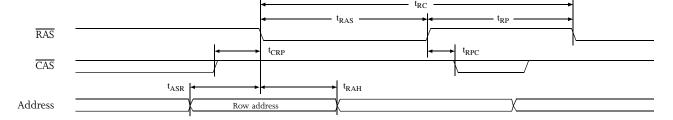

| t <sub>RC</sub>  | Random read or write cycle time  | 80  | _       | 100 | _   | ns   |       |

| t <sub>RP</sub>  | RAS precharge time               | 30  | _       | 40  | _   | ns   |       |

| t <sub>RAS</sub> | RAS pulse width                  | 50  | 10K     | 60  | 10K | ns   |       |

| t <sub>CAS</sub> | CAS pulse width                  | 8   | 10K     | 10  | 10K | ns   |       |

| $t_{RCD}$        | RAS to CAS delay time            | 15  | 35      | 15  | 43  | ns   | 6     |

| t <sub>RAD</sub> | RAS to column address delay time | 12  | 25      | 12  | 30  | ns   | 7     |

| t <sub>RSH</sub> | CAS to RAS hold time             | 10  | _       | 10  | _   | ns   |       |

| t <sub>CSH</sub> | RAS to CAS hold time             | 40  | _       | 50  | _   | ns   |       |

| t <sub>CRP</sub> | CAS to RAS precharge time        | 5   | _       | 5   | _   | ns   |       |

| t <sub>ASR</sub> | Row address setup time           | 0   | _       | 0   | _   | ns   |       |

| t <sub>RAH</sub> | Row address hold time            | 8   | _       | 10  | _   | ns   |       |

| $t_{\mathrm{T}}$ | Transition time (rise and fall)  | 1   | 50      | 1   | 50  | ns   | 4,5   |

| t <sub>REF</sub> | Refresh period                   | _   | 64      | -   | 64  | ms   | 3     |

| t <sub>CP</sub>  | CAS precharge time               | 8   | _       | 10  | _   | ns   |       |

| t <sub>RAL</sub> | Column address to RAS lead time  | 25  | _       | 30  | _   | ns   |       |

| t <sub>ASC</sub> | Column address setup time        | 0   | _       | 0   | _   | ns   |       |

| t <sub>CAH</sub> | Column address hold time         | 8   |         | 10  |     | ns   |       |

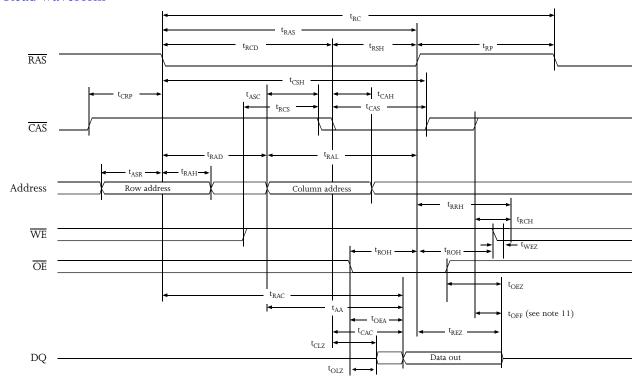

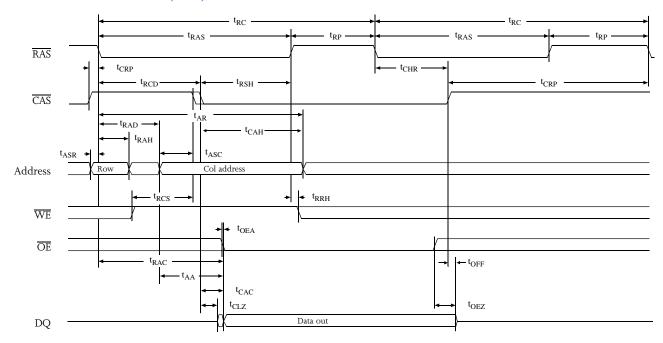

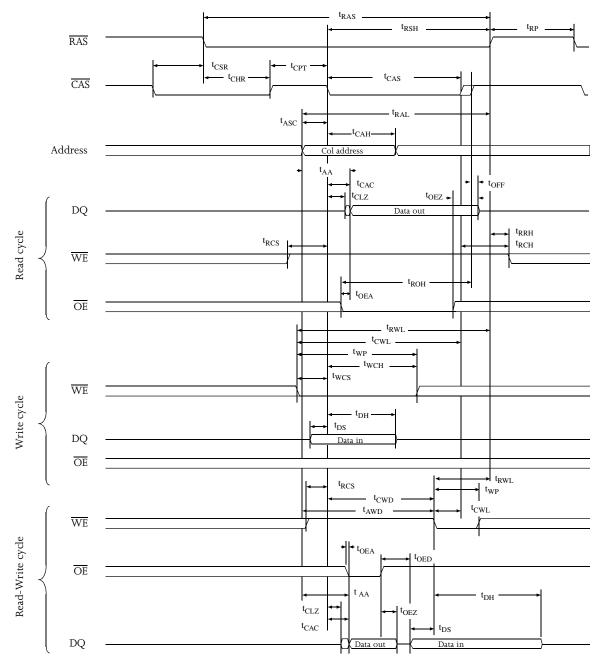

# Read cycle

|                  |                                                   | -50 |     | -60 |     |      |       |

|------------------|---------------------------------------------------|-----|-----|-----|-----|------|-------|

| Symbol           | Parameter                                         | Min | Max | Min | Max | Unit | Notes |

| t <sub>RAC</sub> | Access time from RAS                              | -   | 50  | _   | 60  | ns   | 6     |

| t <sub>CAC</sub> | Access time from CAS                              | -   | 12  | _   | 15  | ns   | 6,13  |

| t <sub>AA</sub>  | Access time from address                          | -   | 25  | _   | 30  | ns   | 7,13  |

| t <sub>RCS</sub> | Read command setup time                           | 0   | -   | 0   | -   | ns   |       |

| t <sub>RCH</sub> | Read command hold time to $\overline{\text{CAS}}$ | 0   | _   | 0   | _   | ns   | 9     |

| t <sub>RRH</sub> | Read command hold time to RAS                     | 0   | _   | 0   | _   | ns   | 9     |

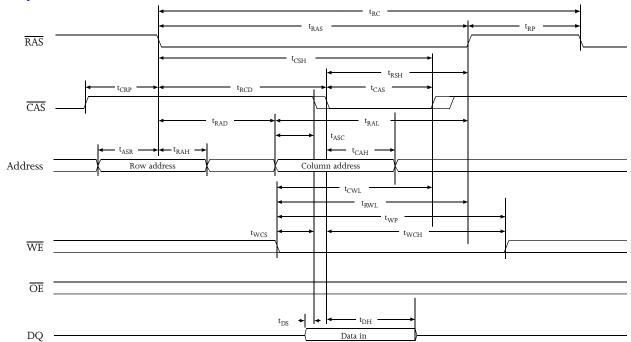

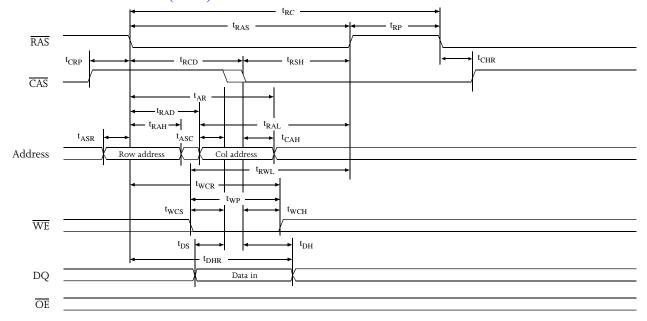

# Write cycle

|                   |                                | -50 |     | -60 |     |      |       |

|-------------------|--------------------------------|-----|-----|-----|-----|------|-------|

| Symbol            | Parameter                      | Min | Max | Min | Max | Unit | Notes |

| t <sub>WCS</sub>  | Write command setup time       | 0   | -   | 0   | _   | ns   | 11    |

| t <sub>WCH</sub>  | Write command hold time        | 10  | -   | 10  | _   | ns   | 11    |

| t <sub>WP</sub>   | Write command pulse width      | 10  | -   | 10  | _   | ns   |       |

| t <sub>RWL</sub>  | Write command to RAS lead time | 10  | -   | 10  |     | ns   |       |

| $t_{CWL}$         | Write command to CAS lead time | 8   | -   | 10  | _   | ns   |       |

| $t_{DS}$          | Data-in setup time             | 0   | -   | 0   | _   | ns   | 12    |

| $t_{\mathrm{DH}}$ | Data-in hold time              | 8   | -   | 10  | _   | ns   | 12    |

# Read-modify-write cycle

|                  |                                 | -50 -60 |     |     |     |      |       |

|------------------|---------------------------------|---------|-----|-----|-----|------|-------|

| Symbol           | Parameter                       | Min     | Max | Min | Max | Unit | Notes |

| t <sub>RWC</sub> | Read-write cycle time           | 113     | -   | 135 | _   | ns   |       |

| t <sub>RWD</sub> | RAS to WE delay time            | 67      | -   | 77  |     | ns   | 11    |

| $t_{\rm CWD}$    | CAS to WE delay time            | 32      | -   | 35  | _   | ns   | 11    |

| t <sub>AWD</sub> | Column address to WE delay time | 42      | -   | 47  | _   | ns   | 11    |

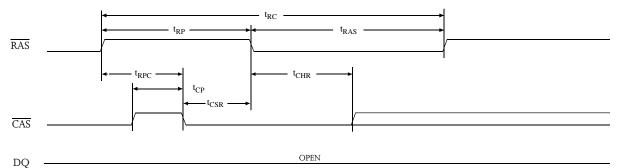

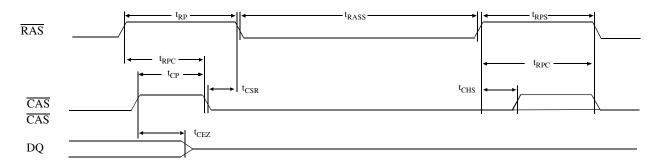

# Refresh cycle

|                  |                                                                                                 | -50 |     | -60 |     |      |       |

|------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|-----|------|-------|

| Symbol           | Parameter                                                                                       | Min | Max | Min | Max | Unit | Notes |

| t <sub>CSR</sub> | $\overline{\text{CAS}}$ setup time ( $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$ ) | 5   | -   | 5   | _   | ns   | 3     |

| t <sub>CHR</sub> | $\overline{\text{CAS}}$ hold time ( $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$ )  | 8   | -   | 10  | _   | ns   | 3     |

| t <sub>RPC</sub> | RAS precharge to CAS hold time                                                                  | 0   | -   | 0   | _   | ns   |       |

| t <sub>CPT</sub> | CAS precharge time (CBR counter test)                                                           | 10  |     | 10  | -   | ns   |       |

Fast page mode cycle

|                   |                                 | -50 |      | -60 |      |      |       |

|-------------------|---------------------------------|-----|------|-----|------|------|-------|

| Symbol            | Parameter                       | Min | Max  | Min | Max  | Unit | Notes |

| t <sub>CPA</sub>  | Access time from CAS precharge  | _   | 28   | _   | 35   |      | 13    |

| t <sub>RASP</sub> | RAS pulse width                 | 50  | 100K | 60  | 100K |      |       |

| t <sub>PC</sub>   | Read-write cycle time           | 30  | _    | 35  | _    |      |       |

| t <sub>CP</sub>   | CAS precharge time (fast page)  | 10  | _    | 10  | _    |      |       |

| t <sub>PCM</sub>  | Fast page mode RMW cycle        | 80  | _    | 85  | _    |      |       |

| t <sub>CRW</sub>  | Page mode CAS pulse width (RMW) | 12  | _    | 15  | _    |      |       |

Output enable

|                  |                                                          | -50 |     | -60 |     |      |       |

|------------------|----------------------------------------------------------|-----|-----|-----|-----|------|-------|

| Symbol           | Parameter                                                | Min | Max | Min | Max | Unit | Notes |

| t <sub>CLZ</sub> | CAS to output in Low Z                                   | 0   | _   | 0   | -   | ns   | 8     |

| t <sub>ROH</sub> | $\overline{RAS}$ hold time referenced to $\overline{OE}$ | 8   | _   | 10  | -   | ns   |       |

| t <sub>OEA</sub> | OE access time                                           | _   | 13  | -   | 15  | ns   |       |

| t <sub>OED</sub> | OE to data delay                                         | 13  | _   | 15  | -   | ns   |       |

| t <sub>OEZ</sub> | Output buffer turnoff delay from $\overline{\text{OE}}$  | 0   | 13  | 0   | 15  | ns   | 8     |

| t <sub>OEH</sub> | OE command hold time                                     | 10  | _   | 10  | -   | ns   |       |

| t <sub>OLZ</sub> | OE to output in Low Z                                    | 0   | _   | 0   | -   | ns   |       |

| t <sub>OFF</sub> | Output buffer turn-off time                              | 0   | 13  | 0   | 15  | ns   | 8,10  |

Self-refresh cycle

|                                                   |                                       | -50 |     | -60 |     |      |       |

|---------------------------------------------------|---------------------------------------|-----|-----|-----|-----|------|-------|

| Std Symbol                                        | Parameter                             | Min | Max | Min | Max | Unit | Notes |

| t <sub>RASS</sub>                                 | RAS pulse width (CBR self refresh)    | 100 | -   | 100 | -   | μs   | 15    |

| t <sub>RPS</sub>                                  | RAS precharge time (CBR self refresh) | 90  | -   | 105 | -   | ns   |       |

| t <sub>CHS</sub> CAS hold time (CBR self refresh) |                                       | 8   | -   | 10  | -   | nx   |       |

#### Notes

- 1  $I_{CC1}$ ,  $I_{CC3}$ ,  $I_{CC4}$ , and  $I_{CC6}$  are dependent on frequency.

- 2 I<sub>CC1</sub> and I<sub>CC4</sub> depend on output loading. Specified values are obtained with the output open.

- 3 An initial pause of 200 µs is required after power-up followed by any 8 RAS cycles before proper device operation is achieved. In the case of an internal refresh counter, a minimum of 8 CAS-before-RAS initialization cycles instead of 8 RAS cycles are required. 8 initialization cycles are required after extended periods of bias without clocks (greater than 8 ms).

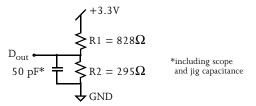

- 4 AC Characteristics assume  $t_T = 2$  ns. All AC parameters are measured with a load equivalent to two TTL loads and 100 pF,  $V_{IL}$  (min)  $\geq$  GND and  $V_{IH}$  (max)  $\leq$   $V_{CC}$ .

- 5  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals. Transition times are measured between  $V_{IH}$  and  $V_{IL}$

- 6 Operation within the  $t_{RCD}$  (max) limit insures that  $t_{RAC}$  (max) can be met.  $t_{RCD}$  (max) is specified as a reference point only. If  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (max) limit, then access time is controlled exclusively by  $t_{CAC}$ .

- 7 Operation within the  $t_{RAD}$  (max) limit insures that  $t_{RAC}$  (max) can be met.  $t_{RAD}$  (max) is specified as a reference point only. If  $t_{RAD}$  is greater than the specified  $t_{RAD}$  (max) limit, then access time is controlled exclusively by  $t_{AA}$ .

- 8 Assumes three state test load (5 pF and a 380  $\Omega$  Thevenin equivalent).

- 9 Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- 10 t<sub>OFF</sub> (max) defines the time at which the output achieves the open circuit condition; it is not referenced to output voltage levels. t<sub>OFF</sub> is referenced from rising edge of RAS or CAS, whichever occurs last.

- 11  $t_{WCS}$ ,  $t_{WCH}$ ,  $t_{RWD}$   $t_{CWD}$  and  $t_{AWD}$  are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If  $t_{WS} \ge t_{WS}$  (min) and  $t_{WH} \ge t_{WH}$  (min), the cycle is an early write cycle and data out pins will remain open circuit, high impedance, throughout the cycle. If  $t_{RWD} \ge t_{RWD}$  (min),  $t_{CWD} \ge t_{CWD}$  (min) and  $t_{AWD} \ge t_{AWD}$  (min), the cycle is a read-write cycle and the data out will contain data read from the selected cell. If neither of the above conditions is satisfied, the condition of the data out at access time is indeterminate.

- 12 These parameters are referenced to CAS leading edge in early write cycles and to WE leading edge in read-write cycles.

- 13 Access time is determined by the longest of  $t_{CAA}$  or  $t_{CAC}$  or  $t_{CPA}$

- 14  $t_{ASC} \ge t_{CP}$  to achieve  $t_{PC}$  (min) and  $t_{CPA}$  (max) values.

- 15 These parameters are sampled and not 100% tested.

#### AC test conditions

- Access times are measured with output reference levels of  $V_{OH}=2.4V$  and  $V_{OL}=0.4V, \\V_{IH}=2.0V$  and  $V_{II}=0.8V$

- Input rise and fall times: 2 ns

Figure A: Equivalent output load (AS4LC4M4F1)

### Key to switching waveforms

| Rising input | Falling input | Undefined output/don't care |

|--------------|---------------|-----------------------------|

|--------------|---------------|-----------------------------|

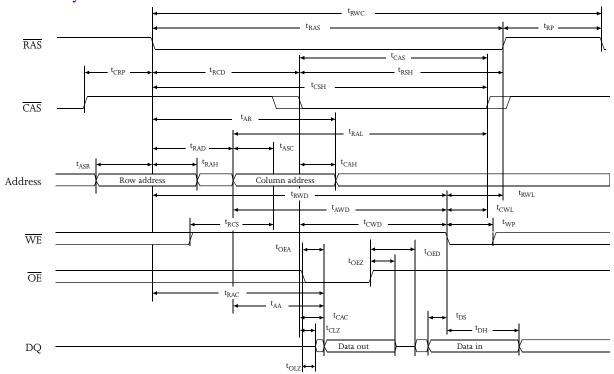

### Read waveform

# Early write waveform

#### Write waveform $\overline{\text{OE}}$ controlled $t_{RC}$ $t_{\rm RAS}$ $t_{RP}$ RAS $t_{CSH}$ - t<sub>RSH</sub> $t_{RCD}$ $t_{CAS}$ CAS t<sub>RAL</sub> $t_{RAD}$ $t_{\text{RAH}}$ Address Row address Column address t<sub>RWL</sub> -WE $t_{\text{OEH}}$ OE $t_{\rm OED}$

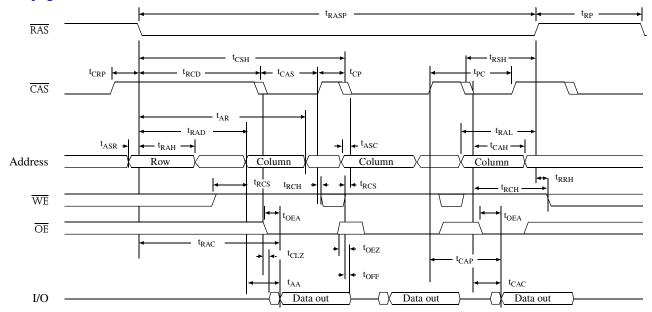

# Read-modify-write waveform

DQ

# Fast page mode read waveform

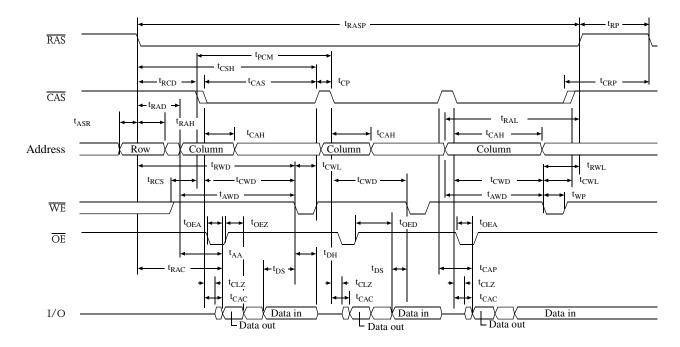

# Fast page mode byte write waveform

# Fast page mode early write waveform

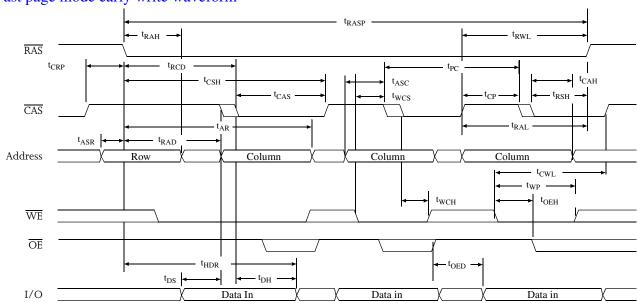

# $\overline{CAS}$ before $\overline{RAS}$ refresh waveform

$\overline{\text{WE}} = V_{\text{IH}}$

# $\overline{RAS}$ only refresh waveform

$\overline{\text{WE}} = \overline{\text{OE}} = V_{\text{IH}} \text{ or } V_{\text{IL}}$

# Hidden refresh waveform (read)

### Hidden refresh waveform (write)

# CAS before RAS refresh counter test waveform

# <del>CAS</del>-before-<del>RAS</del> self refresh cycle

#### Capacitance 15

f = 1 MHz,  $T_a =$ Room temperature

|                   |                  |                  | ,                               | a i |      |

|-------------------|------------------|------------------|---------------------------------|-----|------|

| Parameter         | Symbol           | Signals          | Test conditions                 | Max | Unit |

| I                 | $C_{IN1}$        | A0 to A10        | $V_{in} = 0V$                   | 5   | pF   |

| Input capacitance | C <sub>IN2</sub> | RAS, CAS, WE, OE | $V_{in} = 0V$                   | 7   | pF   |

| DQ capacitance    | $C_{DQ}$         | DQ0 to DQ03      | $V_{\rm in} = V_{\rm out} = 0V$ | 7   | pF   |

#### AS4LC4M4F1 ordering information

| Package \ \( \overline{RAS} \) access time | 50 ns | 60 ns                              |                                    |

|--------------------------------------------|-------|------------------------------------|------------------------------------|

| Plastic SOJ, 300 mil, 24/26-pin            | 3.3V  | AS4LC4M4F1-50JC<br>AS4LC4M4F1-50JI | AS4LC4M4F1-60JC<br>AS4LC4M4F1-60JI |

| Plastic TSOP, 300 mil, 24/26-pin*          | 3.3V  | AS4LC4M4F1-50TC<br>AS4LC4M4F1-50TI | AS4LC4M4F1-60TC<br>AS4LC4M4F1-60TI |

<sup>\*</sup> Shading indicates availability is TBD.

#### AS4LC4M4F1 family part numbering system

| AS4            | LC                | 4M4  | F1            | –XX             | X   | X                                                                              |

|----------------|-------------------|------|---------------|-----------------|-----|--------------------------------------------------------------------------------|

| DRAM<br>prefix | LC = 3.3V<br>CMOS | 4M×4 | F1=2K refresh | RAS access time | , c | Temperature range<br>C=Commercial, 0°C to 70 °C<br>I=Industrial, -40°C to 85°C |

#### 5/16/01; v.1.0 Restored

#### **Alliance Semiconductor**

P. 14 of 14

© Copyright Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Horage or correct this data at any time, without notice. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchanbility, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights, mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products from sale critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assu