### AT25XE081D

8-Mbit, 1.65 V - 3.6 V Range SPI Serial Flash Memory with Multi-I/O Support

#### **Features**

- Voltage Range: 1.65 V 3.6 V

- 8-Mbit Flash Memory

- Flexible 256-byte page erase architecture

- Serial Peripheral Interface (SPI) compatible

- · Supports SPI modes 0 and 3

- Supports SPI single mode operation (1-1-1)

- Supports dual output operation (1-1-2)

- Supports quad output operation (1-1-4)

- Supports quad XiP operation (1-4-4 and 0-4-4)

- 133 MHz maximum operating frequency: Clock-tooutput of 8 ns

- Flexible, optimized erase architecture for code and data storage applications

- Uniform 256-Byte page erase

- Uniform 4-kByte block erase

- Uniform 32-kByte block erase

- · Uniform 64-kByte block erase

- · Full chip erase

- Flexible non-volatile block protection

- 1 x 128-byte factory-programmed unique identifier

- 3 x 128-byte, One Time Programmable (OTP) security registers

- Flexible programming

- Byte/Page program (1 to 256 Bytes)

- Single command page buffer direct Read-Modify-Write (page write with inclusive erase)

- Flexible 256-byte SRAM page buffer operation

- · Sequential program mode capability

- Software controlled Reset and Terminate commands

- Erase program suspend resume

- Hardware reset option (through the HOLD pin)

- JEDEC hardware reset

- Low battery detect circuit

- Active interrupt device status capability

- Non-volatile status register configuration option

- JEDEC standard manufacturer and device ID read methodology

- Serial Flash Discoverable Parameters (SFDP) version 1.6

- Low power dissipation:

- 30 µA standby current (typical)

- 8.5 µA Deep Power-Down (DPD) current (typical)

- 7 nA Ultra Deep Power Down (UDPD) current (typical)

- 8.5 mA active read current (1-1-1 104 MHz)

- · 8.5 mA program current

- 9.6 mA erase current

- User-configurable and auto I/O pin drive levels

- Endurance: 100,000 program/erase cycles

- Data Retention: 20 years

- -40 °C to +85 °C operation

- Industry standard green (Pb/Halide-free/RoHS Compliant) Package Options

- 8-lead SOIC (150-mil)

- 8-lead SOIC (208-mil)

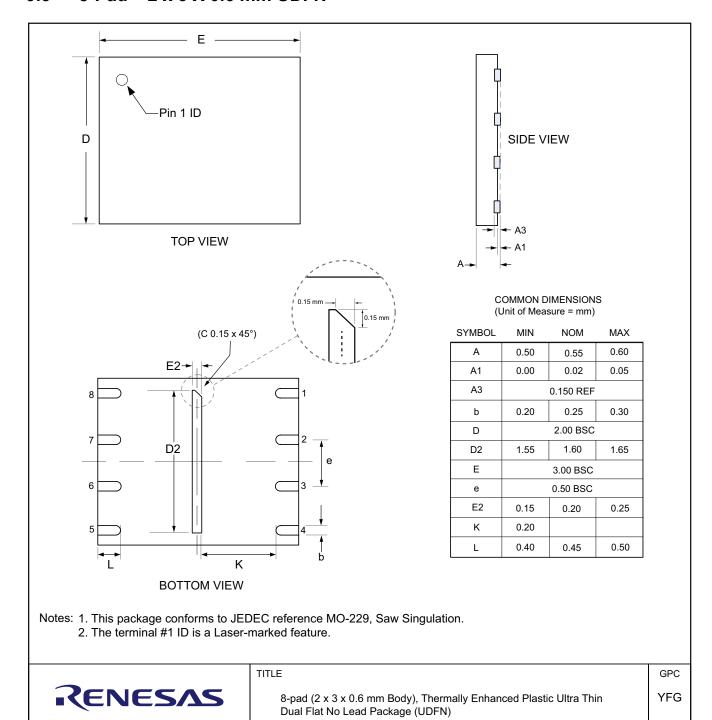

- 8-pad Ultra-thin DFN (2 x 3 x 0.6 mm)

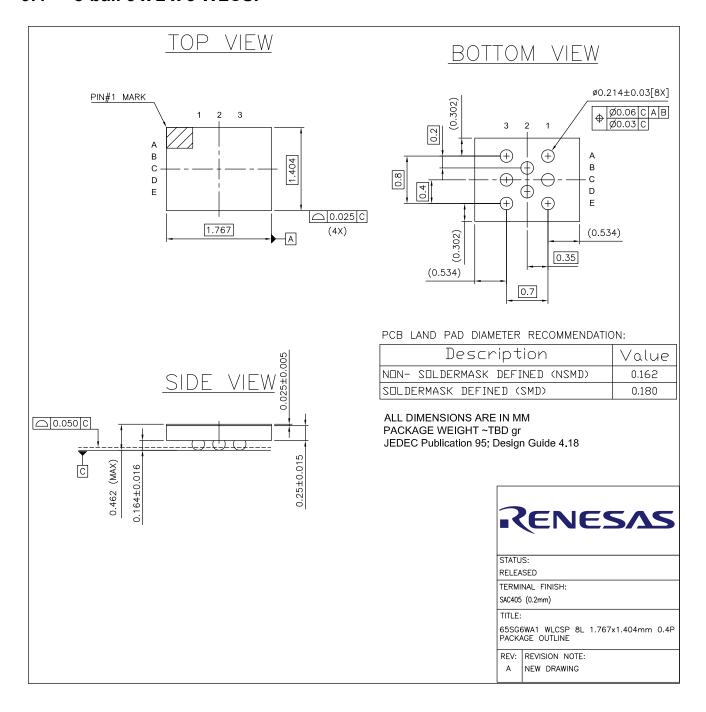

- 8-ball WLCSP (3 x 2 x 3 ball matrix)

- Die/Wafer Contact Renesas Electronics for more information

# **Contents**

| Features                                                                      |    |

|-------------------------------------------------------------------------------|----|

| Figures                                                                       |    |

| Tables                                                                        | 5  |

| 1. Product Overview                                                           | 6  |

| 2. Block Diagram                                                              |    |

| 3. Package Pinouts                                                            |    |

| 4. Device Operation                                                           |    |

| 4.1 Data Transfer Modes                                                       |    |

| 4.2 Standard SPI Operation                                                    |    |

| 4.3 Dual Output Operation (1-1-2)                                             |    |

| 4.4 Quad Output Operation (1-1-4)                                             |    |

| 4.5 Quad I/O Operation (1-4-4)                                                |    |

| 4.6 XiP Mode Operation                                                        |    |

| 4.7 Memory Architecture                                                       | 20 |

| 4.8 Memory Protection                                                         |    |

| 4.9 Power-Down Considerations                                                 | 27 |

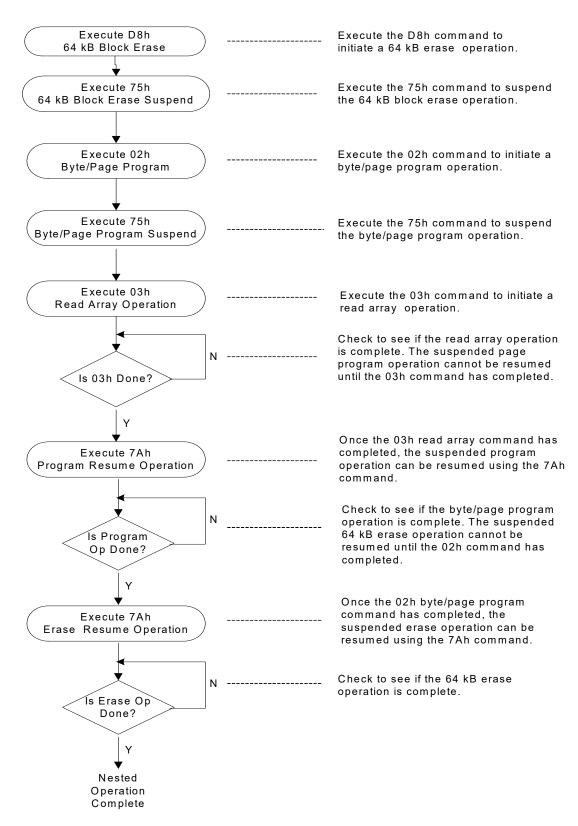

| 4.10 Erase/Program Suspend Considerations and Nested Operations               | 29 |

| 4.11 OTP Security Register Lock                                               |    |

| 4.12 Standard JEDEC Hardware Reset                                            | 34 |

| 4.13 Chip Select Restrictions                                                 |    |

| 4.14 Active Status Interrupt                                                  | 35 |

| 4.15 Low Battery Detect                                                       |    |

| 4.16 Read-Modify-Write                                                        |    |

| 4.17 HOLD / RESET Function                                                    |    |

| 5. Status Registers                                                           |    |

| 5.1 Register Structure and Updates                                            |    |

| 5.2 Register Accesses                                                         |    |

| 5.3 Status Register 1                                                         |    |

| 5.4 Status Register 2                                                         |    |

| 5.5 Status Register 3                                                         |    |

| 5.6 Status Register 4                                                         |    |

| 5.7 Status Register 5                                                         |    |

| 5.8 Status Register 6                                                         |    |

| 6. Commands and Addressing                                                    |    |

| 6.1 Read Array (03h, 0Bh)                                                     |    |

| 6.2 Dual Output Read Array (3Bh)                                              |    |

| 6.3 Quad Output Read Array (6Bh)                                              |    |

| 6.4 XiP Mode Read (EBh), XiP Mode Read with Double-word Aligned Address (E7h) |    |

| 6.5 Page Erase (81h/DBh)                                                      |    |

| 6.6 Block Erase (20h, 52h, D8h)                                               |    |

| 6.7 Chip Erase (60h, C7h)                                                     |    |

| 6.8 Byte/Page Program (02h)                                                   |    |

| 6.9 Sequential Program Mode (ADh/AFh)                                         |    |

| 6.10 Dual Output Byte/Page Program (A2h)                                      |    |

| 6.11 Quad Output Page Program (32h)                                           |    |

| 6.12 Program/Erase Suspend (75h/B0h)                                          |    |

| 6.13 Program/Erase Resume (7Ah/D0h)                                           |    |

|       | 6.14 Set Burst Wrap (77h)                                                     | 72  |

|-------|-------------------------------------------------------------------------------|-----|

|       | 6.15 Buffer Read (D4h)                                                        |     |

|       | 6.16 Buffer Write (84h)                                                       |     |

|       | 6.17 Buffer to Main Memory Page Program without Erase (88h)                   |     |

|       | 6.18 Write Enable (06h)                                                       |     |

|       | 6.19 Write Disable (04h)                                                      |     |

|       | 6.20 Volatile Status Register Write Enable (50h)                              |     |

|       | 6.21 Individual Block Lock (36h)                                              |     |

|       | 6.22 Individual Block Unlock (39h)                                            |     |

|       | 6.23 Read Block Lock (3Ch/3Dh)                                                |     |

|       | 6.24 Global Block Lock (7Eh)                                                  |     |

|       | 6.25 Global Block Unlock (98h)                                                |     |

|       | 6.26 Program Security Register (9Bh)                                          |     |

|       | 6.27 Read OTP Security Register (4Bh)                                         |     |

|       | 6.28 Read Status Registers 1 - 3 (05h, 35h, 15h)                              |     |

|       | 6.29 Read Status Registers (65h)                                              |     |

|       | 6.30 Write Status Registers 1 - 3 — Direct (01h, 31h, 11h)                    |     |

|       | ·                                                                             |     |

|       | 6.31 Write Status Registers — Indirect (71h)                                  |     |

|       | 6.32 Status Register Lock (6Fh)                                               |     |

|       | 6.33 Deep Power-Down (B9h)                                                    |     |

|       | 6.34 Resume from Ultra-Deep Power-Down / Deep Power-Down with Device ID (ABh) |     |

|       | 6.35 Ultra-Deep Power-Down (79h)                                              |     |

|       | 6.36 Enable Reset (66h) and Reset Device (99h)                                |     |

|       | 6.37 Terminate (F0h)                                                          |     |

|       | 6.38 Read Manufacturer/Device ID (90h)                                        |     |

|       | 6.39 Quad Read Manufacturer/Device ID (94h)                                   |     |

|       | 6.40 Read JEDEC ID (9Fh)                                                      |     |

|       | 6.41 Active Status Interrupt (25h)                                            |     |

|       | 6.42 Single Command Read-Modify-Write — EEPROM Emulation (0Ah)                |     |

|       | 6.43 Low Battery Detect (EFh)                                                 |     |

|       | 6.44 Serial Flash Discoverable Parameters (5Ah)                               | 105 |

| 7. El | ectrical Specifications                                                       | 106 |

|       | 7.1 Absolute Maximum Ratings                                                  | 106 |

|       | 7.2 DC and AC Operating Range                                                 | 106 |

|       | 7.3 DC Characteristics                                                        | 106 |

|       | 7.4 AC Clock Characteristics                                                  | 107 |

|       | 7.5 AC Characteristics – All Other Parameters                                 | 107 |

|       | 7.6 Program and Erase Characteristics                                         | 108 |

|       | 7.7 Power-On Timing                                                           | 108 |

|       | 7.8 AC Timing Diagrams                                                        | 110 |

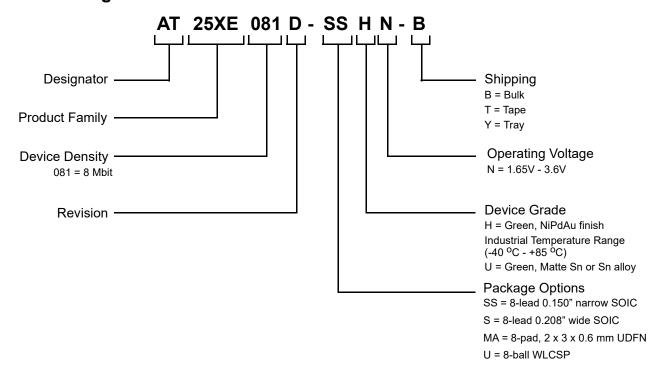

| 8. Or | dering Information                                                            | 112 |

|       | 8.1 Ordering Code Detail                                                      |     |

|       | ckaging Information                                                           |     |

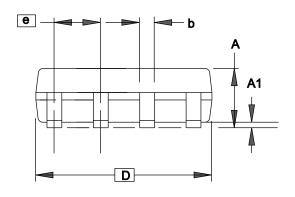

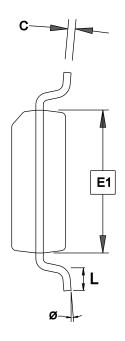

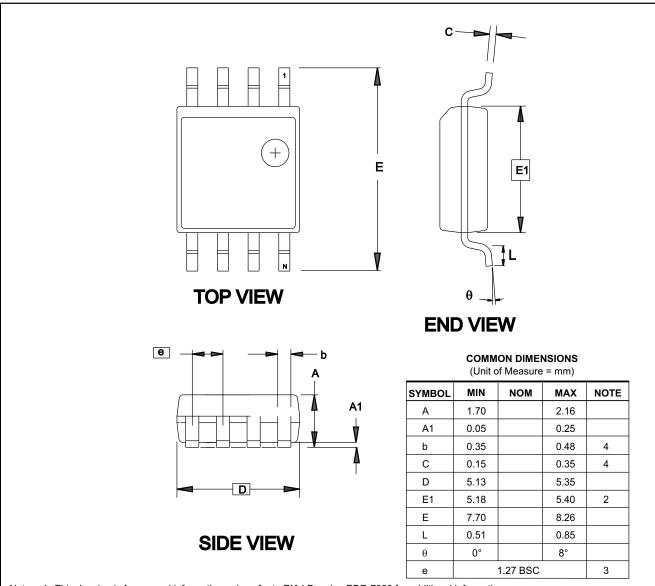

|       | 9.1 8-Lead 0.150" Narrow Body JEDEC SOIC                                      |     |

|       | 9.2 8-lead 0.208" Wide Body EIAJ                                              |     |

|       | 9.3 8-Pad – 2 x 3 X 0.6 mm UDFN                                               |     |

|       | 9.4 8-ball 3 x 2 x 3 WLCSP                                                    |     |

|       |                                                                               | 118 |

|       |                                                                               |     |

# **Figures**

| Figure 1. Block Diagram                                                                                | 7     |

|--------------------------------------------------------------------------------------------------------|-------|

| Figure 2. Memory Package Types                                                                         | 8     |

| Figure 3. SPI Transfer — Command Only                                                                  | 12    |

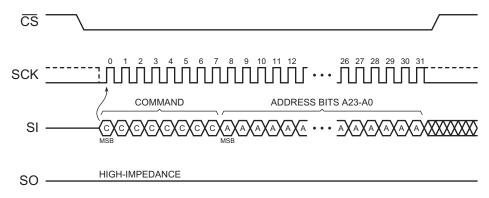

| Figure 4. SPI Transfer — Command and Address Only                                                      | 12    |

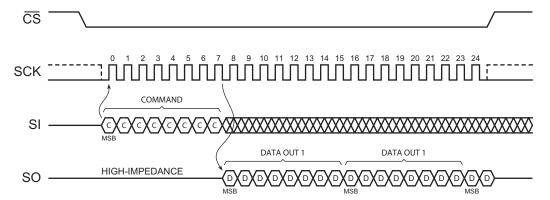

| Figure 5. SPI Transfer — Command and Data Only — Read Operation                                        | 13    |

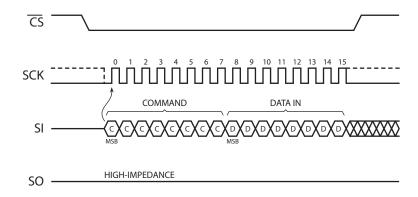

| Figure 6. SPI Transfer — Command and Data Only — Write Operation                                       | 13    |

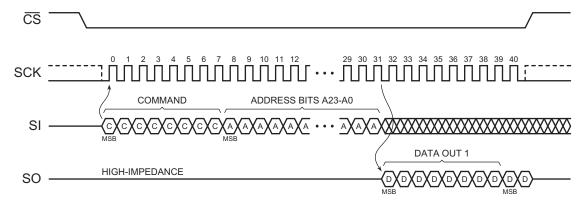

| Figure 7. SPI Transfer — Command, Address, and Data — Read Operation with No Dummy Bytes               | 14    |

| Figure 8. SPI Transfer — Command, Address, and Data — Read Operation with Dummy Bytes                  | 14    |

| Figure 9. SPI Transfer — Command, Address, and Data — Write Operation                                  | 14    |

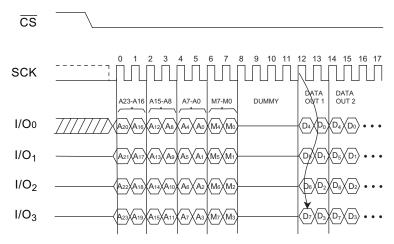

| Figure 10. Dual Output Read — 1-pin Command, 1-Pin Address, and 2-Pin Data                             | 15    |

| Figure 11. Dual Output Write — 1-pin Command, 1-Pin Address, and 2-Pin Data                            | 15    |

| Figure 12. Quad Output Transfer — 1-Pin Command, 1-Pin Address, and 4-Pin Data — Read Operation        | 16    |

| Figure 13. Quad Output Transfer — 1-Pin Command, 1-Pin Address, and 4-Pin Data — Write Operation       | 16    |

| Figure 14. Quad I/O Transfer — 1-Pin Command, 4-Pin Address, and 4-Pin Data — Read Operation           | 17    |

| Figure 15. XiP Transfer — 1-Pin Command, 4-Pin Address, and 4-Pin Data — Initial Read (M[5:4] = 2'b10) | 18    |

| Figure 16. XiP Transfer — No Command, 4-Pin Address, and 4-Pin Data — Subsequent                       |       |

| Reads (M[5:4] = 2'b10)                                                                                 |       |

| Figure 17. XiP Transfer — 1-Pin Command, 4-Pin Address, and 4-Pin Data — Write Operation               |       |

| Figure 18. Flow Diagram of Nested Operations Example                                                   | 30    |

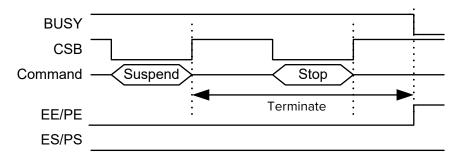

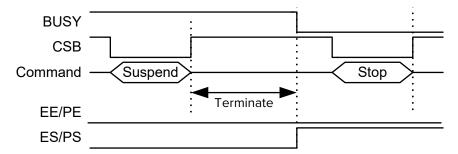

| Figure 19. Issuing a Terminate Command Before the Suspend Command has Completed                        |       |

| Figure 20. Allowing Enough Time for the Suspend Operation to Complete                                  | 33    |

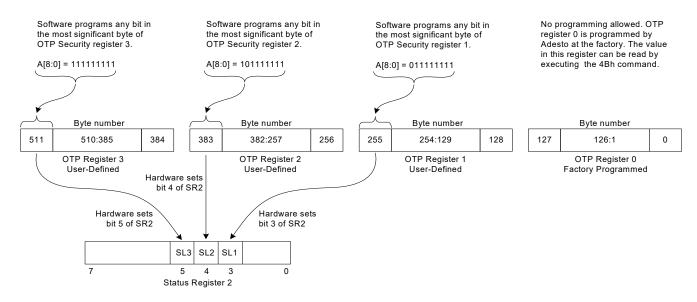

| Figure 21. OTP Security Register Program and Lock                                                      | 34    |

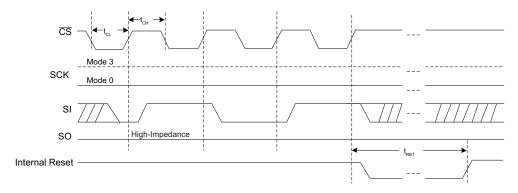

| Figure 22. JEDEC Standard Hardware Reset                                                               | 35    |

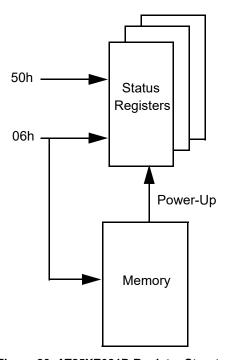

| Figure 23. AT25XE081D Register Structure                                                               | 38    |

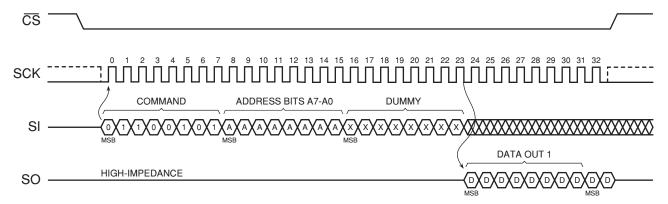

| Figure 24. Status Register Read Operation Showing 8-bit Address Field                                  | 87    |

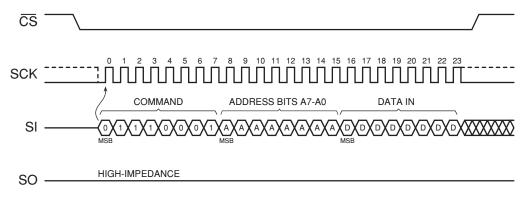

| Figure 25. Status Register Write Operation Showing 8-bit Address Field                                 | 90    |

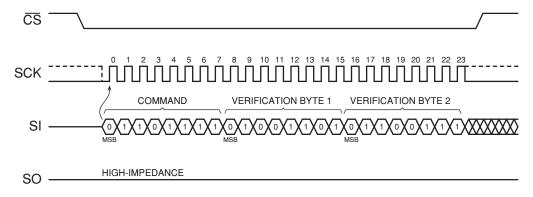

| Figure 26. Status Register Lock Operation with Two Verification Bytes                                  | 91    |

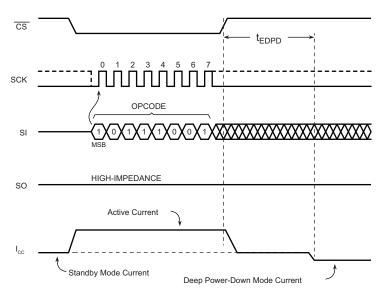

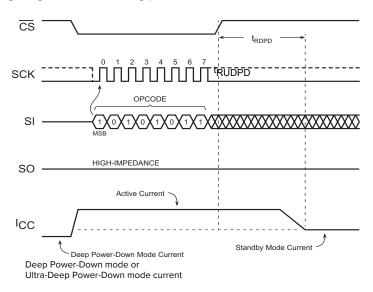

| Figure 27. Entering Deep Power-Down State                                                              | 92    |

| Figure 28. Resume from Deep Power-Down or Ultra-Deep Power-Down                                        |       |

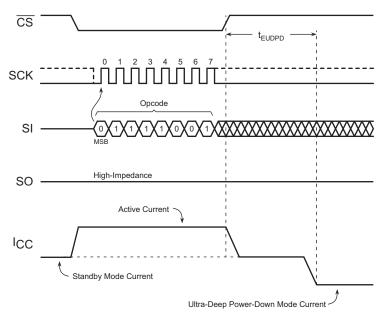

| Figure 29. Entering Ultra-Deep Power-Down State                                                        | 95    |

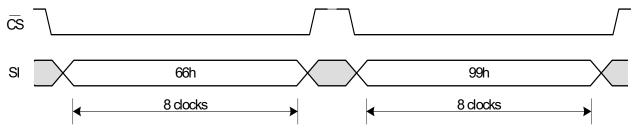

| Figure 30. Enable Reset and Reset Command Sequence (SPI Mode)                                          | 96    |

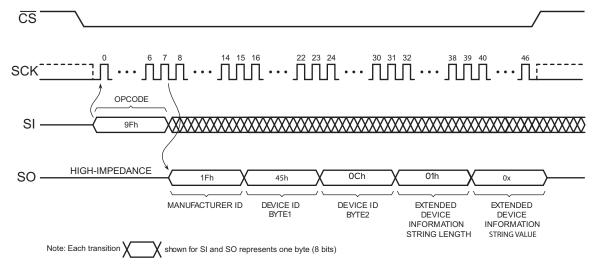

| Figure 31. Read JEDEC ID                                                                               | . 101 |

| Figure 32. Active Status Interrupt                                                                     | . 102 |

| Figure 33. AC Timing During Device Power Up                                                            | . 109 |

| Figure 34. AC Power-On Timing After a Brown-Out                                                        | . 109 |

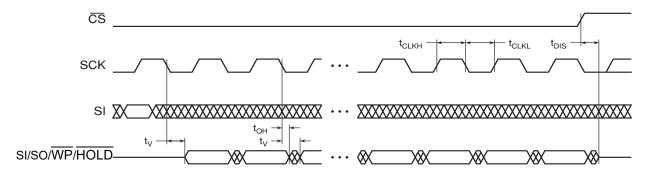

| Figure 35. Serial Input Timing                                                                         | . 110 |

| Figure 36. Serial Output Timing                                                                        | . 110 |

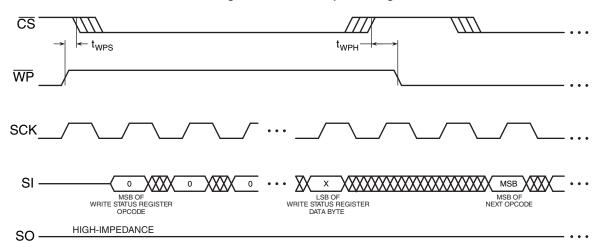

| Figure 37. WP Timing for Write Status Register Command                                                 | . 110 |

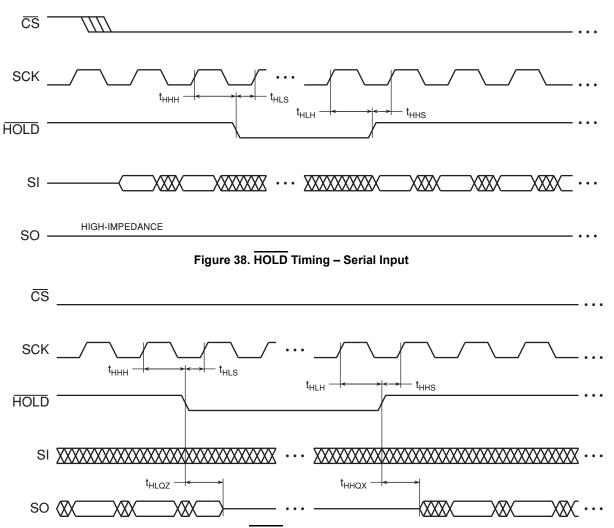

| Figure 38. HOLD Timing – Serial Input                                                                  | . 111 |

| Figure 39 HOLD Timing - Serial Output                                                                  | 111   |

# **Tables**

| Table 1. Pin Descriptions                                                                         | 9    |

|---------------------------------------------------------------------------------------------------|------|

| Table 2. Bus Transfer Types                                                                       | 11   |

| Table 3. Device Block Memory Map — Block Erase Address Ranges                                     | 21   |

| Table 4. AT25XE081D Device Block Memory Map — Page Erase and Page Program                         | 22   |

| Table 5. AT25XE081D Device Block Protection Map — CMPRT = 0, WPS = 0                              | 24   |

| Table 6. AT25XE081D Device Block Protection Map — CMPRT = 1, WPS = 0                              | 25   |

| Table 7. Entering DPD or UDPD Mode                                                                | 27   |

| Table 8. Exiting DPD or UDPD Mode                                                                 | 27   |

| Table 9. Resetting the Device During a Program or Erase Operation                                 | 28   |

| Table 10. Encoding of Erase/Program Suspend Operations                                            |      |

| Table 11. Command Errors and Their Effect on the EE and PE Bits                                   | 31   |

| Table 12. Indirect Addressing of Registers                                                        |      |

| Table 13. Status Register 1 Format                                                                | .40  |

| Table 14. Status Register 2 Format                                                                |      |

| Table 15. Status Register Protection During Normal Operation                                      |      |

| Table 16. Status Register Protection During Reset                                                 |      |

| Table 17. Status Register 3 Format                                                                |      |

| Table 18. Status Register 4 Format                                                                |      |

| Table 19. Status Register 5 Format                                                                |      |

| Table 20. Status Register 6 Format                                                                |      |

| Table 21. Command Listing                                                                         |      |

| Table 22. Frequency and Number of Dummy Clocks Based on Command Type in Non-Wrap Mode (default) . |      |

| Table 23. Frequency and Number of Dummy Clocks Based on Command Type in Wrap Mode (77h)           |      |

| Table 24. Command Behavior During Sequential Programming Mode                                     |      |

| Table 25. Command Behavior During Program/Erase or Program/Erase Suspend Operations               |      |

| Table 26. Encoding of Burst Wrap Bits                                                             |      |

| Table 27. OTP Security Register 0 Bit Assignments                                                 |      |

| Table 28. OTP Security Register 1 Bit Assignments                                                 |      |

| Table 29. OTP Security Register 2 Bit Assignments                                                 |      |

| Table 30. OTP Security Register 3 Bit Assignments                                                 |      |

| Table 31. OTP Register Access Map                                                                 |      |

| Table 32. Indirect Addressing of the Status Registers                                             |      |

| Table 33. Indirect Status Register Read Sequence                                                  |      |

| Table 34. Indirect Addressing of the Status Registers                                             |      |

| Table 35. Indirect Status Register Write Sequence                                                 |      |

| Table 36. Options for Exiting DPD and UDPD Modes                                                  |      |

| Table 37. Manufacturer and Device ID Details                                                      |      |

| Table 38. Device ID Part 4 Variants — EDI String Value                                            |      |

| Table 39. Power On Timing Requirements                                                            |      |

| Table 40. Valid Ordering Codes                                                                    | .112 |

## 1. Product Overview

The AT25XE081D is a serial interface Flash memory device designed for use in a wide variety of high-volume consumer and connected applications. It is optimized for low-energy applications and can be operated using modern Lithium battery technologies over a wide input voltage range of 1.65V - 3.6V.

The AT25XE081D is ideally suited for systems in which program code is shadowed from Flash memory into embedded or external RAM (code shadow) for execution, and where small amounts of data are stored and updated locally in the Flash memory.

The erase block sizes of the AT25XE081D have been optimized to meet the needs of today's code and data storage applications. The device supports 256-byte page erase, as well as 4 kilobyte (kB), 32 kB, and 64 kB block erase operations and a full-chip erase. By optimizing the size of the erase blocks, the memory space can be used much more efficiently.

The device also includes an active interrupt allowing the host to sleep during lengthy programming or erase operations, allowing the memory device to wake the MCU when completed, and optimized energy consumption and class-leading 7 nA ultra-deep power-down modes. The device contains four specialized 128-byte One-Time Programmable (OTP) security registers that can be used to store a unique device ID and locked key storage.

Specifically designed for use in a wide variety of systems, the AT25XE081D supports read, program, and erase operations. No separate voltage is required for programming and erasing.

Throughout this document, the term Multi-I/O is used generically to refer to all of the multiple I/O modes, including dual, quad, and XiP.

The physical block size for this device is 2 Mbit.

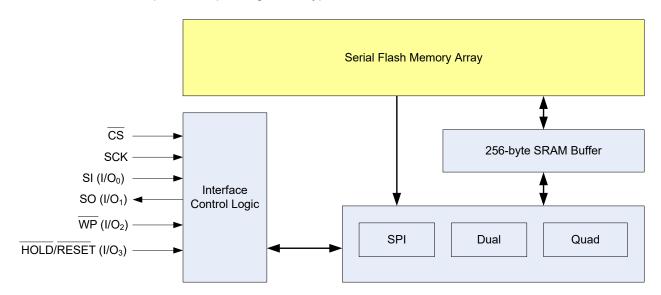

# 2. Block Diagram

Figure 1 shows a block diagram of the AT25XE081D device. The *Interface Control Logic* block connects to external device through a set of pins. The state of these pins is distributed *Interface Control Logic* block to other blocks as necessary. The design also contains an 8 Mbit serial Flash memory array, a 256-byte SRAM buffer, and an I/O *Interface Unit* that operates depending on the type of data transfer mode.

Figure 1. Block Diagram

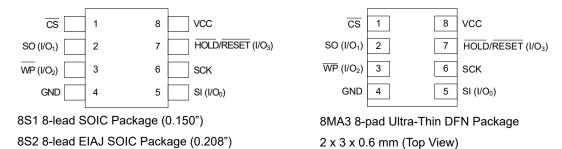

# 3. Package Pinouts

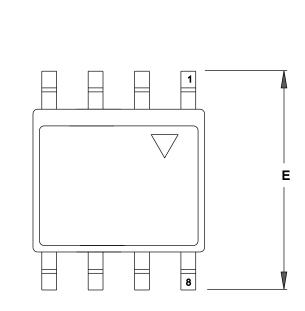

Figure 2 show the package pinouts for the following devices. Note that the Die Wafer Scale option is not shown.

(Top View)

### **Bottom View**

8-ball WLCSP Package 3 x 2 x 3 ball matrix (bottom view)

Figure 2. Memory Package Types

**Table 1. Pin Descriptions**

| Symbol                 | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Asserted<br>State | Туре         |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|

| <del>CS</del>          | CHIP SELECT  Asserting the $\overline{CS}$ pin selects the device. When the $\overline{CS}$ pin is deasserted, the device is be deselected and normally be placed in standby mode (not Deep Power-Down mode), and the SO pin is in a high-impedance state. When the device is deselected, data are not accepted on the SI pin.  A high-to-low transition on the $\overline{CS}$ pin is required to start an operation, and a low-to-high transition is required to end an operation. When ending an internally self-timed operation such as a program or erase cycle, the device does not enter the standby mode until the completion of the operation.  To ensure correct power-up sequencing, it is recommended to add a 10k Ohm pull-up resistor from $\overline{CS}$ to $V_{CC}$ . This ensures $\overline{CS}$ ramps together with $V_{CC}$ during power-up. | Low               | Input        |

| SCK                    | SERIAL CLOCK This pin provides a clock to the device and controls the flow of data to and from the device. Command, address, and input data present on the SI pin is always latched in on the rising edge of SCK, while output data on the SO pin is always clocked out on the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                 | Input        |

| SI (I/O <sub>0</sub> ) | SERIAL INPUT  The SI pin shifts data into the device. The SI pin is used for all data input including command and address sequences. Data on the SI pin is always latched in on the rising edge of SCK.  With the Multi I/O Read commands, the SI pin becomes an output pin (I/O <sub>0</sub> ) in conjunction with other pins to allow either two or four bits of data on (I/O <sub>1:0</sub> or I/O <sub>3:0</sub> ) to be clocked out on every falling edge of SCK.  Data present on the SI pin is ignored whenever the device is deselected (CS is deasserted and the device is in the reset condition).                                                                                                                                                                                                                                                      | -                 | Input/Output |

| SO (I/O <sub>1</sub> ) | SERIAL OUTPUT  The SO pin shifts data out from the device. Data on the SO pin is always clocked out on the falling edge of SCK.  With the Multi I/O Read commands, the SO pin remains an output pin (I/O <sub>1</sub> ) in conjunction with other pins to allow either two or four bits of data on (I/O <sub>1:0</sub> or I/O <sub>3:0</sub> ) to be clocked out on every falling edge of SCK.  The SO pin is in a high-impedance state whenever the device is deselected (CS is deasserted and the device is in the reset condition).                                                                                                                                                                                                                                                                                                                            | -                 | Input/Output |

| WP (I/O <sub>2</sub> ) | WRITE PROTECT  This pin is used either for write-protection, in which case it is referred to as \overline{WP}, or as one of the quad-SPI I/O pins, in which case it is referred to as IO2.  When the Quad Enable (QE) bit of Status Register 2 is 0, and the SRP1 and SRP0 bits are 0 and 1, respectively, the pin can be used for write-protection. It then can be asserted (driven low) to protect the Status Registers from modification.  When the QE bit of Status Register 2 is 1, quad-SPI communication is enabled, and the pin is used as I/O pin IO2 in any command that makes use of quad-SPI. In this setting, do not use the pin for write-protection.  The \overline{WP} pin is internally pulled-high and can be left floating if not used.                                                                                                        | Low               | Input/Output |

Table 1. Pin Descriptions (Continued)

| Symbol                                 | Name and Function                                                                                                                                                                                                                                                                                                                                                                                          | Asserted<br>State | Туре         |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|

|                                        | HOLD / RESET                                                                                                                                                                                                                                                                                                                                                                                               |                   |              |

|                                        | This pin is used either for pausing communication (HOLD), as a hardware reset pin (RESET), or as one of the quad-SPI I/O pins (IO <sub>3</sub> ).                                                                                                                                                                                                                                                          |                   |              |

| HOLD /<br>RESET<br>(I/O <sub>3</sub> ) | When the Quad Enable (QE) bit of Status Register 2 is 0, this pin is used either as a HOLD or RESET pin, depending on the value of the HOLD/RESET bit of Status Register 3. When the QE bit of Status Register 2 is 1, quad-SPI communication is enabled, and the pin is used as I/O pin IO <sub>3</sub> in any command that makes use of quad-SPI. In this setting, do not use the pin for hold or reset. | Low               | Input/Output |

|                                        | The HOLD pin is used to pause a SPI sequence without resetting the clocking sequence. To enable the HOLD mode, the CS must be low. The HOLD mode effect is on with the falling edge of the HOLD signal with SCK being low. The HOLD mode ends on the rising edge of the HOLD signal with SCK being low.                                                                                                    |                   |              |

|                                        | When configured as RESET, this pin can be used to perform a hardware reset on the device.                                                                                                                                                                                                                                                                                                                  |                   |              |

|                                        | The HOLD/RESET/IO <sub>3</sub> pin is internally pulled-high and can be left floating if not used.                                                                                                                                                                                                                                                                                                         |                   |              |

|                                        | DEVICE POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                        |                   |              |

| $V_{CC}$                               | The V <sub>CC</sub> pin supplies the source voltage to the device.                                                                                                                                                                                                                                                                                                                                         | -                 | Power        |

|                                        | Operations at invalid $V_{\mbox{\footnotesize{CC}}}$ voltages can produce spurious results; do not attempt this.                                                                                                                                                                                                                                                                                           |                   |              |

| GND                                    | GROUND                                                                                                                                                                                                                                                                                                                                                                                                     |                   | Power        |

| טויט                                   | The ground reference for the power supply. Connect GND to the system ground.                                                                                                                                                                                                                                                                                                                               | _                 | Power        |

# 4. Device Operation

This section describes the various data transfer modes supported by the device, as well as other system operations.

#### 4.1 Data Transfer Modes

The JEDEC specification uses a numerical system to indicate the type of transfer for a given command. The nomenclature for this system is defined as (x-y-z) to indicate the number of active pins used for the command (x), address (y), and data (z). For an example, a designation of 1-1-2 indicates that one pin (SI) transfers the command, one pin (SI) is for the address, and two pins (SI) are for data. The AT25XE081D supports the following transfer types.

| Transfer<br>Type | Transfer<br>Name | Command | Pin(s) Used for<br>Command | Address | Pin(s) Used for<br>Address | Data | Pin(s) Used for<br>Data |

|------------------|------------------|---------|----------------------------|---------|----------------------------|------|-------------------------|

| 1-0-0            | SPI              | Yes     | SI                         | No      |                            | No   |                         |

| 1-1-0            | SPI              | Yes     | SI                         | Yes     | SI                         | No   |                         |

| 1-0-1            | SPI              | Yes     | SI                         | No      |                            | Yes  | SI (write)<br>SO (read) |

| 1-1-1            | SPI              | Yes     | SI                         | Yes     | SI                         | Yes  | SI (write)<br>SO (read) |

| 1-1-2            | Dual Output      | Yes     | SI                         | Yes     | SI                         | Yes  | SI, SO                  |

| 1-1-4            | Quad Output      | Yes     | SI                         | Yes     | SI                         | Yes  | SI, SO, WP, HOLD        |

| 1-4-4            | Quad I/O         | Yes     | SI                         | Yes     | SI, SO, WP, HOLD           | Yes  | SI, SO, WP, HOLD        |

| 0-4-4            | XiP              | No      |                            | Yes     | SI, SO, WP, HOLD           | Yes  | SI, SO, WP, HOLD        |

**Table 2. Bus Transfer Types**

As shown in Table 2, the AT25XE081D supports the following transfer formats, which are described in the following subsections.

- Standard SPI Operation

- Dual Output Operation

- Quad Output Operation

- Quad I/O Operation

- XiP Operation

# 4.2 Standard SPI Operation

Standard SPI transfers are divided into three elements; command, address, and data. SPI mode support the following four transfer types, as described in Table 2.

- Command only, no address or data (1-0-0)

- Command and address only, no data (1-1-0)

- Command and data only, no address (1-0-1)

- Command, address, and data (1-1-1)

For standard SPI transfers, command and address are always transferred on the SI pin. For write operations, data is also transferred on the SI pin. For read operations, data is transferred on the SO pin.

The AT25XE081D supports the two most common SPI modes, 0 and 3, meaning that data is always latched on the rising edge of SCK and always output on the falling edge of SCK.

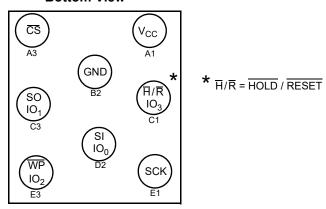

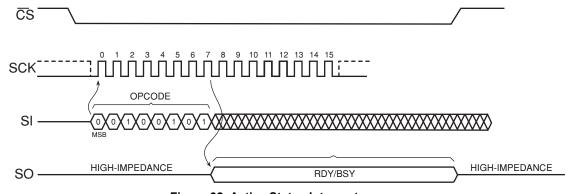

### 4.2.1 Command Only, No Address or Data (1-0-0)

The following diagram shows a command-only transfer. In this type of transfer no address or data are required. An example is the *Chip Erase* (60h/C7h) command. A 1-0-0 transfer type is shown in Figure 3.

Figure 3. SPI Transfer — Command Only

### 4.2.2 Command and Address Only, No Data (1-1-0)

The following diagram shows a transfer with command and address only. In this type of transfer no data is required. An example is the *Block Erase* (20h) command, where the address indicates the location of the block to be erased.

The 1-1-0 transfer type is shown in Figure 4.

Figure 4. SPI Transfer — Command and Address Only

## 4.2.3 Command and Data Only, No Address (1-0-1)

The following diagrams show a transfer with command and data only. In this type of transfer no address is required. An example is the *Status Register Read* (05h/35h/15h) and *Status Register Write* (01h/31h/11h) commands, where the command itself indicates the location of the register. The 1-0-1 transfer type for a read operation is shown in Figure 5.

Figure 5. SPI Transfer — Command and Data Only — Read Operation

The 1-0-1 transfer type for a write operation is shown in Figure 6.

Figure 6. SPI Transfer — Command and Data Only — Write Operation

### 4.2.4 Command, Address, and Data (1-1-1)

The following diagrams show a command, address, and data transfer. In this type of transfer the command and address are followed by one or more data types, depending on the command type.

Note that this type of transfer can contain one or more dummy bytes between the end of the address and the beginning of the data output depending on the type of command. See the command table in Section 7 for more information.

The 1-1-1 transfer type for a read operation without dummy bytes is shown in Figure 7. An example is the *Read Array* (03h) command.

Figure 7. SPI Transfer — Command, Address, and Data — Read Operation with No Dummy Bytes

The 1-1-1 transfer type for a read operation with dummy bytes is shown in Figure 8. An example is the *Fast Read Array* (0Bh) command. Note that eight dummy clocks are shown in the figure below for illustration purposes only. More than eight clocks may be required, depending on the type of operation and operating frequency.

Figure 8. SPI Transfer — Command, Address, and Data — Read Operation with Dummy Bytes

The 1-1-1 transfer type for a write operation is shown in Figure 9. An example is the Byte/Page Program (02h) command.

Figure 9. SPI Transfer — Command, Address, and Data — Write Operation

## 4.3 Dual Output Operation (1-1-2)

The AT25XE081D supports the Dual Output (1-1-2) transfer type which enhances overall throughput over the standard SPI mode. This mode transfer command and address on the SI pin like in SPI mode, but the data is transferred on to the SI and SO pins. This means that only half the number of clocks are required to transfer the data.

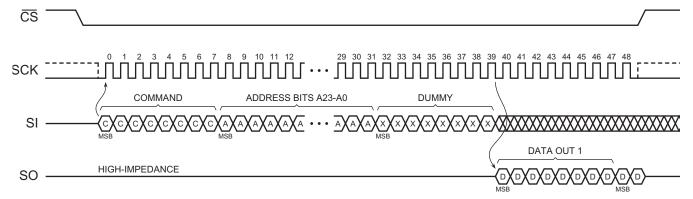

A Dual Output read operation is shown in Figure 10. An example of this operation is a *Dual Output Read* (3Bh). Note that this type of transfer can contain one or more dummy bytes between the end of the address and the beginning of the data output depending on the type of command and the operating frequency. See the Command table in Section 7 for more information.

A Dual Output 1-1-2 read operation is shown in Figure 10.

Figure 10. Dual Output Read — 1-pin Command, 1-Pin Address, and 2-Pin Data

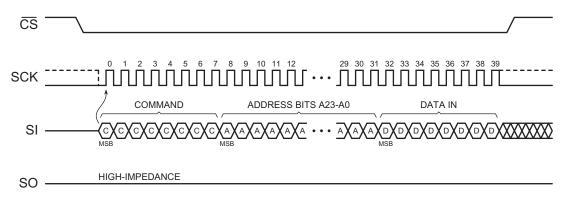

A Dual Output (1-1-2) write operation is shown in Figure 11. An example of this operation is a *Dual Output Byte/Page Program* (A2h).

Figure 11. Dual Output Write — 1-pin Command, 1-Pin Address, and 2-Pin Data

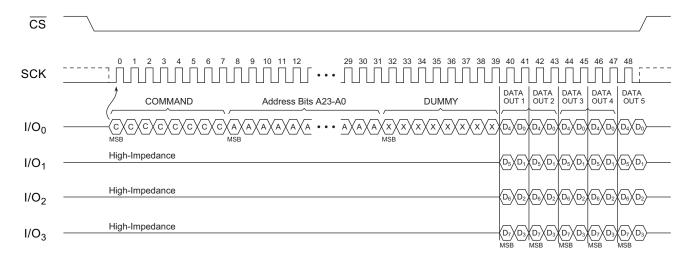

# 4.4 Quad Output Operation (1-1-4)

The AT25XE081D supports the Quad Output mode which enhances overall throughput over the standard SPI and dual operation modes by increasing the data transfer rate. In this mode, data is transferred on four pins:  $IO_0$ ,  $IO_1$ ,  $IO_2$ , and  $IO_3$ . This means that only 1/4th the number of clocks are required to transfer the data relative to standard SPI mode. This is known as a 1-1-4 transfer which is defined as follows: 1-pin command, 1-pin address, and 4-pin data (1-1-4).

In Quad Output mode, the command (C) and address (A) are driven to the memory device on the  $IO_0$  pin. During write operations, the  $IO_0$ ,  $IO_1$ ,  $IO_2$ , and  $IO_3$  pins switched to inputs and the data is driven on all four pins, allowing four data bits to be transferred on every clock. During read operations, once the command and address are transferred on the SI ( $IO_0$ ) pin, the  $IO_0$ ,  $IO_1$ ,  $IO_2$ , and  $IO_3$  pins switched to outputs and the data is driven on all four pins, allowing four data bits to be transferred on every clock.

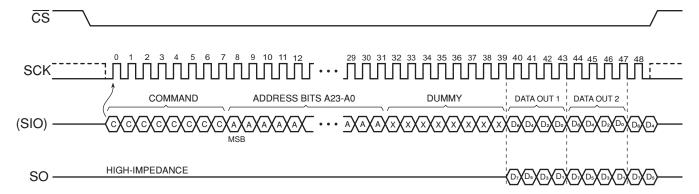

A 1-1-4 Quad Output read operation is shown in Figure 12. An example of this operation is a *Quad Output Read* (6Bh). Note that this type of transfer can contain one or more dummy bytes between the end of the address and the beginning of the data output depending on the type of command and the operating frequency. See the Command table in Section 7 for more information.

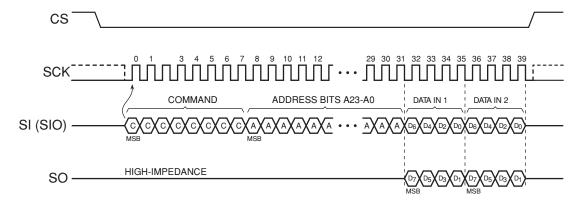

Figure 12. Quad Output Transfer — 1-Pin Command, 1-Pin Address, and 4-Pin Data — Read Operation A 1-1-4 Quad Output write operation is shown in Figure 13. An example of this operation is a *Quad Output Byte/Page Program* (32h).

Figure 13. Quad Output Transfer — 1-Pin Command, 1-Pin Address, and 4-Pin Data — Write Operation

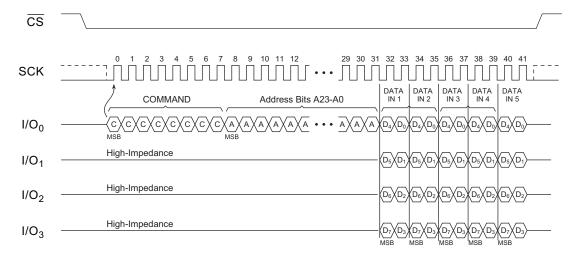

# 4.5 Quad I/O Operation (1-4-4)

The AT25XE081D supports the Quad I/O mode which enhances overall throughput over the standard SPI and dual operation modes by increasing the data transfer rate. In this mode, address and data are transferred on four pins:  $IO_0$ ,  $IO_1$ ,  $IO_2$ , and  $IO_3$ . This means that only 1/4th the number of clocks are required to transfer the address and data relative to standard SPI mode. This is known as a 1-4-4 transfer which is defined as follows: 1-pin command, 4-pin address, and 4-pin data (1-4-4).

In Quad I/O mode the command (C) is driven to the memory device on the  $IO_0$  pin. During write operations, the  $IO_0$ ,  $IO_1$ ,  $IO_2$ , and  $IO_3$  pins switched to inputs and the address and data are driven on all four pins, allowing four bits to be transferred on every clock. During read operations, once the command is transferred on the SI ( $IO_0$ ) pin, address is transferred on the  $IO_0$ ,  $IO_1$ ,  $IO_2$ , and  $IO_3$  pins, allowing a 24-bit address to be transferred in only six clocks. Once the address transfer is complete, these pins are switched to outputs and the data is driven on all four pins, allowing four data bits to be transferred on every clock. Note that mode bits II0 must not be in high-impedance (tri-state) mode. For optimal performance it is recommended to drive a value of 55h or FFh on these bits when not in XiP mode.

A 1-4-4 Quad I/O read operation is shown in Figure 14. An example of this operation is a *Manufacturer/Device ID Read* (94h). Note that this type of transfer can contain one or more dummy bytes between the end of the address and the beginning of the data output depending on the type of command and the operating frequency. See Table 21 for more information.

Figure 14. Quad I/O Transfer — 1-Pin Command, 4-Pin Address, and 4-Pin Data — Read Operation

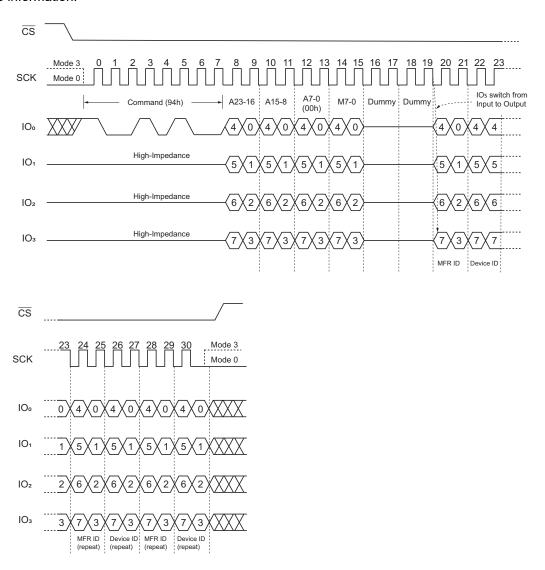

# 4.6 XiP Mode Operation

The XiP mode is similar to the Quad I/O mode in that both the address and data are transferred on all four pins, IO<sub>0</sub>, IO<sub>1</sub>, IO<sub>2</sub>, and IO<sub>3</sub>. Using all four pins to transfer address and data allows XiP mode to reduce the overall number of clocks required to complete the operation, thereby streamlining code execution.

The XiP mode is enabled by setting bit 2 (QE) of Status Register 1, and bit 3 (XiP) of Status Register 4. The QE bit enables Quad I/O mode, allowing address and data to be transferred on all four pins. Setting the XiP bit enables continuous read mode, allowing subsequent transfers to occur without driving the command each time. Continuous read mode is controlled by mode bits M[5:4] as explained below. Therefore, the initial EBh or E7h command requires the command to be driven, but for subsequent transfers the command is not required.

The XiP mode is only used for the following commands:

- EBh: XiP mode initial read (1-4-4)

- EBh: XiP mode subsequent reads (0-4-4)

- E7h: XiP mode initial read with Doubleword Aligned (DWA) address (1-4-4)

- E7h: XiP mode subsequent reads with DWA address (0-4-4)

As shown above, the only difference between the EBh and E7h commands is that the E7h command is performed only on a double-word-aligned address boundary. The EBh command does not have this restriction. Note that mode bits M[7:0] must not be in high-Z (tri-state) mode. For optimal performance it is recommended to drive a value of 55h or FFh on these bits when not in XiP mode.

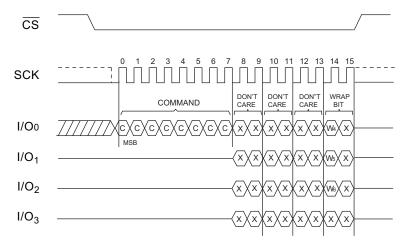

The Set Burst with Wrap (77h) command does not access the memory directly, but rather is used in conjunction with the EBh and E7h commands to select 8-, 16-, 32-, or 64-Byte sections within a 256-byte page. The user selects the size by programming the wrap bits as part of the 77h command. See the table in Section 6.14, Set Burst Wrap (77h) for more information.

When the EBh/E7h command is driven onto the bus, the associated data immediately following the address contains eight mode bits, known as M[7:0]. Of these bits, M[5:4] are decoded and used by hardware to determine if the device is in XiP continuous read mode. If the value on M[5:4] equals 2'b10, the device is placed into XiP mode to allow for continuous read operations to occur, meaning that for subsequent operations the command field is not required. Each time a subsequent transfer is made, it contains only the address and mode bits.

## 4.6.1 Initial Transfer and XiP Mode Detection (M[5:4])

The initial XiP transfer follows the 1-4-4 format, where the EBh or E7h command is transferred on the SI ( $IO_0$ ) pin, and address and data are transferred on the SI ( $IO_0$ ), SO ( $IO_1$ ),  $\overline{WP}$  ( $IO_2$ ), and  $\overline{HOLD}$  ( $IO_3$ ) pins. Because all four pins are used, the address requires only six clocks to transfer. The initial 1-4-4 XiP mode transfer is shown in Figure 15.

Figure 15. XiP Transfer — 1-Pin Command, 4-Pin Address, and 4-Pin Data — Initial Read (M[5:4] = 2'b10)

## 4.6.2 Subsequent Transfers

Once XiP mode is detected, subsequent operations do not require the command to be transferred. After the data stream starts, the user can deassert the  $\overline{\text{CS}}$  pin. Once  $\overline{\text{CS}}$  is deasserted, data output is suspended. Once  $\overline{\text{CS}}$  is again driven low, only the address and M[7:0] mode data are required because the device is already in XiP mode. Each time a new operation is transferred on the bus, hardware decodes the M[7:0] bits. As long as M[5:4] have a value of 2'b10, the device is in XiP mode and it is not necessary to transfer the command. Once M[5:4]  $\neq$  2'b10 (any value other than 2'b10), the operation completes and the device exits XiP mode. A subsequent 0-4-4 XiP mode transfer is shown in Figure 16.

Figure 16. XiP Transfer — No Command, 4-Pin Address, and 4-Pin Data — Subsequent Reads (M[5:4] = 2'b10)

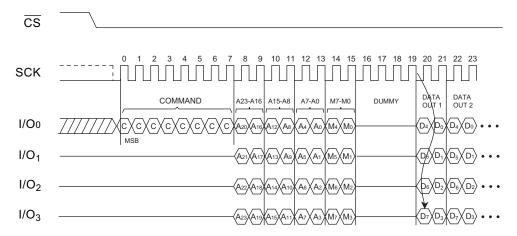

# 4.6.3 Set Burst with Wrap

As mentioned above, the *Set Burst with Wrap* (77h) command is used in conjunction with the EBh and E7h commands to select specific sections within a 256-byte page. When this command is transferred, the data field contains 8 wrap bits. Bits 6:4 of this field determine the wrap length, which can be between 8 and 64 bytes. See Section 6.14, Set Burst Wrap (77h) for more information.

Note that when the device receives the EBh/E7h command with M[5:4] = 2'b10, then the device enters XiP mode. While in the XiP (0-4-4) mode (see Subsequent Transfers subsection above) the only command that the device can execute are EBh (or E7h). This is mandatory since the command field for subsequent transfers does not exist.

During normal operation, the user sends the 77h command before entering XiP mode. If the user wants to issue a 77h command after XiP mode has been entered (to change the wrap length/properties), they must exit the XiP mode by sending a 0-4-4 command with  $M[5:4] \neq 2$ 'b10). This exits XiP mode. Then the user can issue the 77h command. The 77h command is a 1-4-4 XiP mode transfer as shown in Figure 17.

Figure 17. XiP Transfer — 1-Pin Command, 4-Pin Address, and 4-Pin Data — Write Operation

See Section 6.14, Set Burst Wrap (77h) for more information.

# 4.7 Memory Architecture

The memory array of the AT25XE081D memory array is divided into three levels of granularity comprising of blocks and pages;

- 64 kB blocks

- 32 kB blocks

- 4 kB blocks

- 256 byte pages

The size of the erase blocks is optimized for both code and data storage applications, allowing both code and data segments to reside in their own erase regions.

Table 3 details each level and the number of pages per block. The program operations to the memory array can be done at the full page level or at the byte level (a variable number of bytes). Erase operations can be performed at the chip, block, or page level.

Table 3. Device Block Memory Map — Block Erase Address Ranges

| 64 kB Block Erase (D8h) | 32 kB Block Erase (52h) | 4 kB Block Erase (20h)   | Block Address Range |

|-------------------------|-------------------------|--------------------------|---------------------|

|                         |                         | 4 kB (B255) <sup>1</sup> | 0FF000h - 0FFFFFh   |

|                         |                         | 4 kB (B254)              | 0FE000h - 0FEFFFh   |

|                         |                         | 4 kB (B253)              | 0FD000h - 0FDFFFh   |

|                         | 32 kB                   | 4 kB (B252)              | 0FC000h - 0FCFFFh   |

|                         | (block 31)              | 4 kB (B251)              | 0FB000h - 0FBFFFh   |

|                         |                         | 4 kB (B250)              | 0FA000h - 0FAFFFh   |

|                         |                         | 4 kB (B249)              | 0F9000h - 0F9FFFh   |

| 64 kB                   |                         | 4 kB (B248)              | 0F8000h - 0F8FFFh   |

| (block 15)              |                         | 4 kB (B247)              | 0F7000h - 0F7FFFh   |

|                         |                         | 4 kB (B246)              | 0F6000h - 0F6FFFh   |

|                         |                         | 4 kB (B245)              | 0F5000h - 0F5FFFh   |

|                         | 32 kB                   | 4 kB (B244)              | 0F4000h - 0F4FFFh   |

|                         | (block 30)              | 4 kB (B243)              | 0F3000h - 0F3FFFh   |

|                         |                         | 4 kB (B242)              | 0F2000h - 0F2FFFh   |

|                         | _                       | 4 kB (B241)              | 0F1000h - 0F1FFFh   |

|                         |                         | 4 kB (B240)              | 0F0000h - 0F0FFFh   |

| 64 kB (block 14)        | 32 kB (block 29)        | 4 kB (B239)              | 0EF000h - 0EFFFFh   |

| to                      | to                      | to                       | to                  |

| 64 kB (block 1)         | 32 kB (block 2)         | 4 kB (B16)               | 010000h - 010FFFh   |

|                         |                         | 4 kB (B15)               | 00F000h - 00FFFFh   |

|                         |                         | 4 kB (B14)               | 00E000h - 00EFFFh   |

|                         |                         | 4 kB (B13)               | 00D000h - 00DFFFh   |

|                         | 32 kB                   | 4 kB (B12)               | 00C000h - 00CFFFh   |

|                         | (block 1)               | 4 kB (B11)               | 00B000h - 00BFFFh   |

|                         |                         | 4 kB (B10)               | 00A000h - 00AFFFh   |

|                         |                         | 4 kB (B9)                | 009000h - 009FFFh   |

| 64 kB                   |                         | 4 kB (B8)                | 008000h - 008FFFh   |

| (block 0                |                         | 4 kB (B7)                | 007000h - 007FFFh   |

|                         |                         | 4 kB (B6)                | 006000h - 006FFFh   |

|                         |                         | 4 kB (B5)                | 005000h - 005FFFh   |

|                         | 32 kB                   | 4 kB (B4)                | 004000h - 004FFFh   |

|                         | (block 0)               | 4 kB (B3)                | 003000h - 003FFFh   |

|                         |                         | 4 kB (B2)                | 002000h - 002FFFh   |

|                         |                         | 4 kB (B1)                | 001000h - 001FFFh   |

|                         |                         | 4 kB (B0)                | 000000h - 000FFFh   |

<sup>1.</sup> B = block.

Table 4 shows how one 4 kB block maps to sixteen 256 byte pages. The very top and bottom 4 Kbyte blocks of the address space are shown.

Table 4. AT25XE081D Device Block Memory Map — Page Erase and Page Program

| 4 kB Blocks              |                     | 256 Byte Page Erase | 1 - 256 Byte Page Program |

|--------------------------|---------------------|---------------------|---------------------------|

| 4 kB (B255) <sup>1</sup> |                     | 256 Bytes           | 0FFF00h - 0FFFFFh         |

| 4 kB (B254)              |                     | 256 Bytes           | 0FFE00h - 0FFEFFh         |

| 4 kB (B253)              |                     | 256 Bytes           | 0FFD00h - 0FFDFFh         |

| 4 kB (B252)              |                     | 256 Bytes           | 0FFC00h - 0FFCFFh         |

| 4 kB (B251)              |                     | 256 Bytes           | 0FFB00h - 0FFBFFh         |

| 4 kB (B250)              |                     | 256 Bytes           | 0FFA00h - 0FFAFFh         |

| 4 kB (B249)              |                     | 256 Bytes           | 0FF900h - 0FF9FFh         |

| 4 kB (B248)              |                     | 256 Bytes           | 0FF800h - 0FF8FFh         |

| 4 kB (B247)              |                     | 256 Bytes           | 0FF700h - 0FF7FFh         |

| 4 kB (B246)              |                     | 256 Bytes           | 0FF600h - 0FF6FFh         |

| 4 kB (B245)              |                     | 256 Bytes           | 0FF500h - 0FF5FFh         |

| 4 kB (B244)              |                     | 256 Bytes           | 0FF400h - 0FF4FFh         |

| 4 kB (B243)              |                     | 256 Bytes           | 0FF300h - 0FF3FFh         |

| 4 kB (B242)              |                     | 256 Bytes           | 0FF200h - 0FF2FFh         |

| 4 kB (B241)              |                     | 256 Bytes           | 0FF100h - 0FF1FFh         |

| 4 kB (B240)              |                     | 256 Bytes           | 0FF000h - 0FF0FFh         |

| 4kB (B239)               |                     |                     |                           |

| to                       |                     | •                   |                           |

| 4kB (B16)                | · .                 | 050 D. 4            |                           |

| 4 kB (B15)               | <b>⊢</b> /⊦         | 256 Bytes           | 000F00h - 000FFFh         |

| 4 kB (B14)               | _                   | 256 Bytes           | 000E00h - 000EFFh         |

| 4 kB (B13)               | _ / /               | 256 Bytes           | 000D00h - 000DFFh         |

| 4 kB (B12)               | $\dashv$ / $\vdash$ | 256 Bytes           | 000C00h - 000CFFh         |

| 4 kB (B11)               | _ / /               | 256 Bytes           | 000B00h - 000BFFh         |

| 4 kB (B10)               | _ / /               | 256 Bytes           | 000A00h - 000AFFh         |

| 4 kB (B9)                | $\dashv$ / $\dashv$ | 256 Bytes           | 000900h - 0009FFh         |

| 4 kB (B8)                | $\perp$             | 256 Bytes           | 000800h - 0008FFh         |

| 4 kB (B7)                | $\perp$             | 256 Bytes           | 000700h - 0007FFh         |

| 4 kB (B6)                | _                   | 256 Bytes           | 000600h - 0006FFh         |

| 4 kB (B5)                | _  /                | 256 Bytes           | 000500h - 0005FFh         |

| 4 kB (B4)                | _  /                | 256 Bytes           | 000400h - 0004FFh         |

| 4 kB (B3)                | _  /                | 256 Bytes           | 000300h - 0003FFh         |

| 4 kB (B2)                | _ /                 | 256 Bytes           | 000200h - 0002FFh         |

| 4 kB (B1)                | _/                  | 256 Bytes           | 000100h - 0001FFh         |

| 4 kB (B0)                |                     | 256 Bytes           | 000000h - 0000FFh         |

1. B = Block

# 4.8 Memory Protection

The AT25XE081D device incorporates a robust memory protection scheme that allows memory locations to be protected down to the 4 kB block level. The device provides the ability to globally lock all blocks in one operation, or to lock individual blocks on a per-block basis.

## 4.8.1 Standard Memory Protection

The standard memory protection scheme is invoked by clearing bit 2 (WPS) of Status Register 3. When this bit is cleared, the AT25XE081D uses a combination of the following register fields to set the memory protection scheme:

- CMPRT: When this bit is set, unprotected areas of memory become protected, and protected areas of memory become unprotected. For example, when CMPRT = 0, a top 64 kB block can be protected while the rest of the array is not; when CMP = 1, the same 64 kB block becomes unprotected while the rest of the array becomes read-only. See bit 6 of Section 5.4, Status Register 2 for more information.

- BPSIZE: This bit works in conjunction with bits 4:2 (BP[2:0]) in Status Register 1 to determine the size of the blocks to be protected. Block sizes of 4 kB and 64 kB can be protected depending on the state of this bit. See bit 6 of Section 5.3, Status Register 1 for more information.

- TB: This bit indicates if the protection is from the bottom up of the top down of the memory. See bit 5 of Section

5.3, Status Register 1 for more information.

- BP[2:0]: This field can be programmed to protect all of the memory array, none of the memory array, or a portion of the memory array. When that portion of the memory if protected, it is protected from the program and erase commands. See bit 4:2 of Section 5.3, Status Register 1 for more information.

The protection scheme differs based on the setting of the CMPRT bit described above. Table 5 shows the relationship between the BPSIZE, BP[2:0], and TB bits when CMPRT = 0. The right-most column shows the protected address range. All addresses not shown are unprotected.

Table 5. AT25XE081D Device Block Protection Map — CMPRT = 0, WPS = 0

|   |   | ТВ | BP[2:0] | Protected Address Range |

|---|---|----|---------|-------------------------|

| 0 | 0 | 0  | 3'b000  | NONE                    |

| 0 | 0 | 0  | 3'b001  | 0F0000 - 0FFFFF         |

| 0 | 0 | 0  | 3'b010  | 0E0000 - 0FFFFF         |

| 0 | 0 | 0  | 3'b011  | 0C0000 - 0FFFFF         |

| 0 | 0 | 0  | 3'b100  | 080000 - 0FFFFF         |

| 0 | 0 | 0  | 3'b101  | 000000 - 0FFFFF         |

| 0 | 0 | 0  | 3'b110  | 000000 - 0FFFFF         |

| 0 | 0 | 0  | 3'b111  | 000000 - 0FFFFF         |

| 0 | 0 | 1  | 3'b000  | NONE                    |

| 0 | 0 | 1  | 3'b001  | 000000 - 00FFFF         |

| 0 | 0 | 1  | 3'b010  | 000000 - 01FFFF         |

| 0 | 0 | 1  | 3'b011  | 000000 - 03FFFF         |

| 0 | 0 | 1  | 3'b100  | 000000 - 07FFFF         |

| 0 | 0 | 1  | 3'b101  | 000000 - 0FFFFF         |

| 0 | 0 | 1  | 3'b110  | 000000 - 0FFFFF         |

| 0 | 0 | 1  | 3'b111  | 000000 - 0FFFFF         |

| 0 | 1 | 0  | 3'b000  | NONE                    |

| 0 | 1 | 0  | 3'b001  | 0FF000 - 0FFFFF         |

| 0 | 1 | 0  | 3'b010  | 0FE000 - 0FFFFF         |

| 0 | 1 | 0  | 3'b011  | 0FC000 - 0FFFFF         |

| 0 | 1 | 0  | 3'b100  | 0F8000 - 0FFFFF         |

| 0 | 1 | 0  | 3'b101  | 0F8000 - 0FFFFF         |

| 0 | 1 | 0  | 3'b110  | 000000 - 0FFFFF         |

| 0 | 1 | 0  | 3'b111  | 000000 - 0FFFFF         |

| 0 | 1 | 1  | 3'b000  | NONE                    |

| 0 | 1 | 1  | 3'b001  | 000000 - 000FFF         |

| 0 | 1 | 1  | 3'b010  | 000000 - 001FFF         |

| 0 | 1 | 1  | 3'b011  | 000000 - 003FFF         |

| 0 | 1 | 1  | 3'b100  | 000000 - 007FFF         |

| 0 | 1 | 1  | 3'b101  | 000000 - 007FFF         |

| 0 | 1 | 1  | 3'b110  | 000000 - 0FFFF          |

| U |   |    |         |                         |

Table 6 shows the relationship between the BPSIZE, BP[2:0], and TB bits when CMPRT = 1.

Table 6. AT25XE081D Device Block Protection Map — CMPRT = 1, WPS = 0

| CMPRT | BPSIZE | ТВ | BP[2:0] | Protected Address Range            |

|-------|--------|----|---------|------------------------------------|

| 1     | 0      | 0  | 3'b000  | 000000 - 0FFFFF                    |

| 1     | 0      | 0  | 3'b001  | 000000 - 0EFFFF                    |

| 1     | 0      | 0  | 3'b010  | 000000 - 0DFFFF                    |

| 1     | 0      | 0  | 3'b011  | 000000 - 0BFFFF                    |

| 1     | 0      | 0  | 3'b100  | 000000 - 07FFFF                    |

| 1     | 0      | 0  | 3'b101  | NONE                               |

| 1     | 0      | 0  | 3'b110  | NONE                               |

| 1     | 0      | 0  | 3'b111  | NONE                               |

| 1     | 0      | 1  | 3'b000  | 000000 - 0FFFFF                    |

| 1     | 0      | 1  | 3'b001  | 010000 - 0FFFFF                    |

| 1     | 0      | 1  | 3'b010  | 020000 - 0FFFFF                    |

| 1     | 0      | 1  | 3'b011  | 040000 - 0FFFFF                    |

| 1     | 0      | 1  | 3'b100  | 080000 - 0FFFF                     |

| 1     | 0      | 1  | 3'b101  | NONE                               |

| 1     | 0      | 1  | 3'b110  | NONE                               |

| 1     | 0      | 1  | 3'b111  | NONE                               |

| 1     | 1      | 0  | 3'b000  | 000000 - 0FFFFF                    |

| 1     | 1      | 0  | 3'b001  | 000000 - 0FEFFF <sup>[1][2]</sup>  |

| 1     | 1      | 0  | 3'b010  | 000000 - 0FDFFF <sup>(1)</sup> (2) |

| 1     | 1      | 0  | 3'b011  | 000000 - 0FBFFF <sup>(1)</sup> (2) |

| 1     | 1      | 0  | 3'b100  | 000000 - 0F7FFF <sup>(2)</sup>     |

| 1     | 1      | 0  | 3'b101  | 000000 - 0F7FFF <sup>(2)</sup>     |

| 1     | 1      | 0  | 3'b110  | NONE                               |

| 1     | 1      | 0  | 3'b111  | NONE                               |

| 1     | 1      | 1  | 3'b000  | 000000 - 0FFFFF                    |

| 1     | 1      | 1  | 3'b001  | 001000 - 0FFFF <sup>[3][4]</sup>   |

| 1     | 1      | 1  | 3'b010  | 002000 - 0FFFFF <sup>(3) (4)</sup> |

| 1     | 1      | 1  | 3'b011  | 004000 - 0FFFFF <sup>(3) (4)</sup> |

| 1     | 1      | 1  | 3'b100  | 008000 - 0FFFFF <sup>(4)</sup>     |

| 1     | 1      | 1  | 3'b101  | 008000 - 0FFFF <sup>(4)</sup>      |

| 1     | 1      | 1  | 3'b110  | NONE                               |

| 1     | 1      | 1  | 3'b111  | NONE                               |

<sup>1.</sup> When the 32 kB Erase command is used, the protected region is 0x00\_0000 - 0x0F\_7FFF.

<sup>2.</sup> When the 64 kB Erase command is used, the protected region is 0x00\_0000 - 0x0E\_FFFF.

<sup>3.</sup> When the 32 kB Erase command is used, the protected region is 0x00\_8000 - 0x0F\_FFFF.

<sup>4.</sup> When the 64 kB Erase command is used, the protected region is 0x01\_0000 - 0x0F\_FFFF.

#### 4.8.2 Individual Block Lock and Unlock

In addition to the standard protection scheme described in the previous subsection, the AT25XE081D device also provides the ability to lock individual memory locations. Protection of memory locations can be applied individually using the *Individual Block Lock* (36h) command and the *Individual Block Unlock* (39h) command. The user must execute a series of one or more *Individual Block Unlock* (39h) commands to unlock the desired memory locations.

The individual memory protection scheme is invoked by setting bit 2 (WPS) of Status Register 3. When this bit is set, the AT25XE081D uses the *Individual Block Lock* (36h) command that provides the address of the 4 kB or 64 kB block to be locked. See Table 17 for more information on the WPS bit.

Table 3 above shows the address ranges for each 4 kB block corresponding to the top and bottom 64 kB blocks of the memory map. The appropriate 24-bit address is driven on the SI pin after the 36h command. After decoding the command, hardware reads the address and sets the appropriate lock bit for that 4 kB block.

Note that the ability to lock 4 kB blocks only applies to the top and bottom 64 kB blocks of the map. This corresponds to blocks 0 and 15. For 64 kB blocks 1 - 14, the blocks can only be locked on the 64 kB boundary (1 lock bit per 64 kB). This equates to a total of 46 lock bits;

- 16 bits, one per 4 kB sub-block in the top 64 kB block

- 16 bits, one per 4 kB sub-block in the bottom 64 kB block

- 14 bits, one each for 64 kB blocks 1 14

See Section 6.21, Individual Block Lock (36h) and Section 6.22, Individual Block Unlock (39h) for more information.

#### 4.8.3 Global Block Lock and Unlock

In addition to individual block protection of memory locations as described in the previous subsection, the AT25XE081D also allows for the blocks to be locked and unlocked globally using the *Global Block Lock* (7Eh) and the *Global Block Unlock* (98h) commands. Note that in the AT25XE081D device all lock bits are set by default, making all memory locations protected. The user must execute a *Global Unlock Block* command to unlock the memory locations.

Note that in the AT25XE081D the factory default setting is the Standard Memory Protection scheme; therefore, all memory locations are unprotected.

See Section 6.24, Global Block Lock (7Eh) and Section 6.25, Global Block Unlock (98h) for more information.

## 4.8.4 Reading the State of the Lock Bits

In addition to globally or individually locking and unlocking selected memory blocks as described above, the AT25XE081D device allows the user to poll any block in memory to determine if it has been locked. This is done by executing either the 3Ch or 3Dh command, along with the 24-bit address. Both of these command perform the exact same operation and can be used interchangeably.

Once this information is decoded, hardware fetches the 8-bit lock field from the requested location and outputs this information onto the SO pin. The most significant bit (MSB) of the value is transferred first, and the least significant bit (LSB) is transferred last. If the LSB is 1, the corresponding block is locked and no erase or program operation can be executed to that block. If the LSB is 0, the block or section is unlocked and program/erase operations are allowed. See Section 6.23, Read Block Lock (3Ch/3Dh) for more information.

### 4.9 Power-Down Considerations

The AT25XE081D device supports the *Deep Power-Down* (B9h) and *Ultra-Deep Power-Down* (79h/B9h) modes. Also, bit 7 (PDM) of Status Register 4 (SR4) can be used to select either of these modes using the B9h command. The 79h command is provided for backward compatibility.

There are three ways to enter power-down mode:

- 1. Set the PDM bit in SR4 (logic 1) and execute the B9h command to place the device into *Deep Power-Down* (DPD) mode. In this mode it is possible to execute the *Resume from Deep Power-Down* (ABh) command or *Enable Reset* (66h) and *Reset Device* (99h) commands in order to exit DPD mode. The content of SRAM buffer is preserved in this case. The device could also be reset by JEDEC reset, hardware reset, or power-on-reset in order to exit DPD mode. The exit from DPD mode time is defined by the t<sub>RDPD</sub> timing parameter in Section 7.8. Also see Section 4.9.2, below. Note that in the AT25XE081D device, simply deasserting CS as in other devices does not exit DPD mode.

- 2. Clear the PDM bit in SR4 (logic 0) and execute the B9h command to place the device into *Ultra-Deep Power-Down* (UDPD) mode. To exit this mode, it is necessary to execute the *Resume from Ultra-Deep Power-Down* (ABh) command or a JEDEC reset, hardware reset, or power-on-reset to initiate an internal reset of the device. The contents of the SRAM buffer are NOT preserved. The resume from UDPD mode recovery time is defined by the t<sub>RUDPD</sub> timing parameter in Section 7.8. Also see Section 4.9.2, below. Note that in the AT25XE081D device, simply deasserting CS as in other devices does NOT exit UDPD mode.

- 3. Execute the 79h command to place the device into Ultra-Deep Power-Down (UDPD) mode. If this command is used, the state of the PDM bit in SR4 is ignored. This mode allows for software backward compatibility. A device reset is required to exit UPDP mode. In this mode it is necessary to execute the Resume from Ultra-Deep Power-Down (ABh) command or a JEDEC reset, hardware reset or power-on-reset to initiate an internal reset of the device. The contents of the SRAM buffer are NOT preserved. The exit from UDPD mode recovery time is defined by the t<sub>RUDPD</sub> timing parameter in Section 7.8. Also see Section 4.9.2, below for more information on exiting power-down mode.

## 4.9.1 Entering Power-Down Mode

The conditions for entering DPD or UDPD mode are shown in the Table 7. The PDM column indicates the state of the Power-Down Mode bit in Status Register 4.

| Command | PDM bit | Power-Down Mode       | SRAM Contents | Power-Down Exit<br>Recovery Time |

|---------|---------|-----------------------|---------------|----------------------------------|

| B9h     | 1       | Deep Power-Down       | Retained      | Short                            |

| B9h     | 0       | Ultra-Deep Power-Down | Lost          | Long                             |

| 79h     | х       | Ultra-Deep Power-Down | Lost          | Long                             |

Table 7. Entering DPD or UDPD Mode

# 4.9.2 Exiting Power-Down Mode

The following methods can be used to exit DPD or UDPD mode.

Table 8. Exiting DPD or UDPD Mode

| Command | PDM<br>bit | Power-Down<br>Mode | Exit<br>Command    | Power On<br>Reset | JEDEC<br>Reset | Hardware<br>Reset Pin <sup>[1]</sup> | 66h/99h<br>Command | Terminate<br>(F0h) | Status<br>After Exit |

|---------|------------|--------------------|--------------------|-------------------|----------------|--------------------------------------|--------------------|--------------------|----------------------|

| B9h     | 1          | DPD                | ABh <sup>[2]</sup> | Y                 | Y              | Y                                    | Y                  | N                  | Idle                 |

| B9h     | 0          | UDPD               | ABh <sup>[3]</sup> | Y                 | Y              | Y                                    | N                  | N                  | ldle                 |

| 79h     | х          | UDPD               | ABh <sup>(3)</sup> | Y                 | Y              | Y                                    | N                  | N                  | ldle                 |

- 1. Hardware reset function must be enabled by software before entering the Power-Down mode. See bit 7 of Status Register 3.

- 2. Executing the ABh command in DPD mode returns the device to an idle state. The SRAM contents are retained.

- 3. Executing the ABh command in UDPD mode causes the device to initiate an internal reset sequence. The SRAM contents are undefined.

#### **ABh Command**

Executing the ABh command while in the Deep Power-Down (DPD) mode causes the device to exit DPD and return back to an idle state. This command does not reset the device and no data is lost. Executing the ABh command while in the Ultra-Deep Power-Down (UDPD) mode causes the device to perform an internal reset. In this case the SRAM contents are undefined.

#### **Device Resets**

In addition to the ABh command described above, performing a Power On Reset (POR), a JEDEC reset, or asserting the hardware reset pin (RESET) also causes the device to exit DPD or UDPD mode. If the device is reset in any of these three ways, the SRAM contents are undefined.

#### Enable Reset (66h) / Reset (99h) Command

As shown in Table 8, the 66h/99h reset command is accepted in DPD mode. In this case the SRAM contents are retained. The device does not exit UDPD mode, regardless of whether the device entered UDPD mode using the B9h command or the 79h command. To exit UDPD mode, the device must be reset as described in the previous subsections.

#### **Terminate Command (F0h)**

The *Terminate* (F0) command does not cause exit from DPD or UDPD modes. To exit DPD or UDPD mode still requires either the ABh command, or resetting the device as described in the previous subsections.

### 4.9.3 Reset During Program and Erase Commands

The AT25XE081D device supports the following program and erase operations.

Program operations include:

- Byte/Page Program (02h)

- Sequential Program (AFh/ADh)

- Dual Output Byte/Page Program (A2h)

- Quad Output Byte/Page Program (32h)

- Read-Modify-Write (0Ah)

- Main Memory Page Program Without Erase (88h)

- Program Security Register (9Bh)

Erase operations include:

- Page Erase (81h/DBh)

- 4 kB Block Erase (20h)

- 32 kB Block Erase (52h)

- 64 kB Block Erase (D8h)

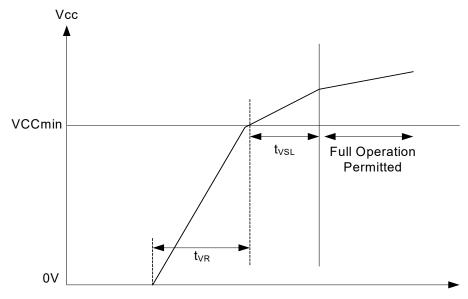

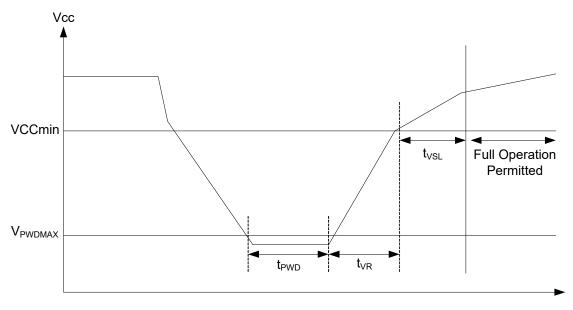

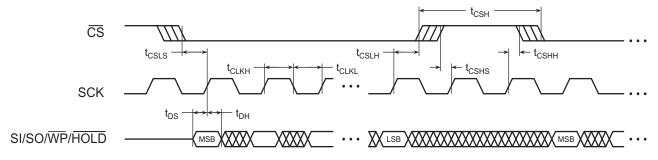

- Chip Erase (60h/C7h)