## Features

- Ideal Rewritable Attribute Memory

- Simple Write Operation

- Self-Timed Byte Writes

- On-chip Address and Data Latch for SRAM-like Write Operation

- Fast Write Cycle Time 1 ms

- 5-Volt-Only Nonvolatile Writes

- End of Write Detection

- RDY/BUSY Output

- DATA Polling

- High Reliability

- Endurance: 100,000 Write Cycles

- Data Retention: 10 Years Minimum

- Single 5-Volt Supply for Read and Write

Very Low Power

- 30 mA Active Current

- 100 µA Standby Current

## Description

The AT28C16-T is the ideal nonvolatile attribute memory: it is a low power, 5-volt-only byte writable nonvolatile memory (EEPROM). Standby current is typically less than 100  $\mu$ A. The AT28C16-T is written like a Static RAM, eliminating complex programming algorithms. The fast write cycle times of 1 ms, allow quick card reconfiguration in-system. Data retention is specified as 10 years minimum, precluding the necessity for batteries. Three access times have been specified to allow for varying layers of buffering between the memory and the PCMCIA interface.

The AT28C16-T is accessed like a Static RAM for read and write operations. During a byte write, the address and data are latched internally. Following the initiation of a write cycle, the device will go to a busy state and automatically write the latched data using an internal control timer. The device provides two methods for detecting the end of a write cycle; the RDY/BUSY output and DATA POLLING of I/O<sub>7</sub>.

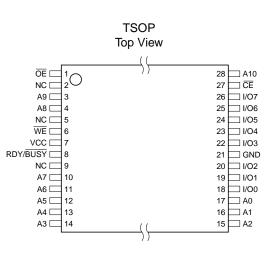

# **Pin Configurations**

| Pin Name    | Function            |

|-------------|---------------------|

| A0 - A10    | Addresses           |

| CE          | Chip Enable         |

| ŌE          | Output Enable       |

| WE          | Write Enable        |

| 1/00 - 1/07 | Data Inputs/Outputs |

| RDY/BUSY    | Ready/Busy Output   |

| NC          | No Connect          |

16K (2K x 8) PCMCIA Nonvolatile Attribute Memory

# AT28C16-T

Rev. 0258C-10/98

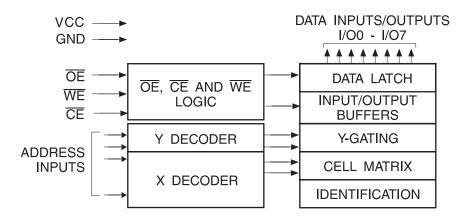

## **Block Diagram**

## **Absolute Maximum Ratings\***

| Temperature Under Bias                                                         |

|--------------------------------------------------------------------------------|

| Storage Temperature65°C to +125°C                                              |

| All Input Voltages (including NC Pins)<br>with Respect to Ground0.6V to +6.25V |

| All Output Voltages with Respect to Ground0.6V to $V_{\rm CC}$ + 0.6V          |

| Voltage on $\overline{\text{OE}}$ and A9 with Respect to Ground0.6V to +13.5V  |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

AT28C16-T

#### **Device Operation**

**READ:** The AT28C16-T is accessed like a Static RAM. When  $\overrightarrow{CE}$  and  $\overrightarrow{OE}$  are low and  $\overrightarrow{WE}$  is high, the data stored at the memory location determined by the address pins is asserted on the outputs. The outputs are put in a high impedance state whenever  $\overrightarrow{CE}$  or  $\overrightarrow{OE}$  is high. This dual-line control gives designers increased flexibility in preventing bus contention.

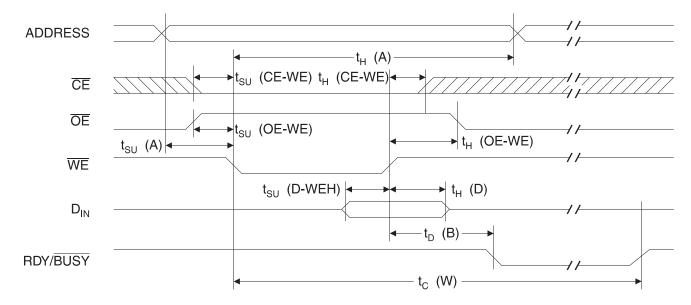

**BYTE WRITE:** Writing data into the AT28C16-T is similar to writing into a Static RAM. A low pulse on WE or CE input with OE high and CE or WE low (respectively) initiates a byte write. The address is latched on the falling edge of WE or CE (whichever occurs last) and the data is latched on the rising edge of WE or CE (whichever occurs first). Once a byte write is started it will automatically time itself to completion. For the AT28C16-T the write cycle time is 1 ms maximum. Once a programming operation has been initiated and for the duration of  $t_{WC}$ , a read operation will effectively be a polling operation.

**READY/BUSY**: Pin 1 is an open drain READY/BUSY output that indicates the current status of the self-timed internal write cycle. READY/BUSY is actively pulled low during the write cycle and is released at the completion of the write. The open drain output allows OR-tying of several devices to a common interrupt input.

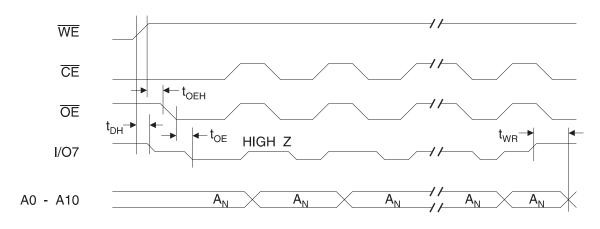

**DATA POLLING:** The AT28C16-T also provides DATA polling to signal the completion of a write cycle. During a write cycle, an attempted read of the data being written results in the complement of that data for  $I/O_7$  (the other outputs are indeterminate). When the write cycle is finished, true data appears on all outputs.

**WRITE PROTECTION:** Inadvertent writes to the device are protected against in the following ways: (a)  $V_{CC}$  sense—if  $V_{CC}$  is below 3.8V (typical) the write function is inhibited; (b)  $V_{CC}$  power on delay—once  $V_{CC}$  has reached 3.8V the device will automatically time out 5 ms (typical) before allowing a byte write; and (c) write inhibit—holding any one of  $\overline{OE}$  low,  $\overline{CE}$  high or  $\overline{WE}$  high inhibits byte write cycles.

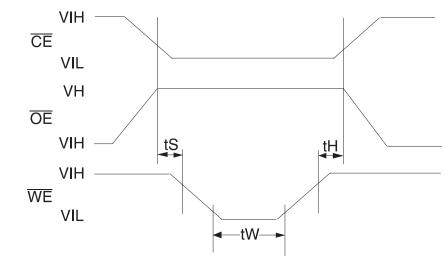

**CHIP CLEAR:** The contents of the entire memory of the AT28C16-T may be set to the high state by the Chip Clear operation. By setting  $\overline{CE}$  low and  $\overline{OE}$  to 12V, the chip is cleared when a 10 ms low pulse is applied to  $\overline{WE}$ .

**DEVICE IDENTIFICATION:** An extra 32 bytes of EEPROM memory are available to the user for device identification. By raising A9 to 12V ( $\pm$  0.5V) and using address locations 7E0H to 7FFH the additional bytes may be written to or read from in the same manner as the regular memory array.

# <u>AÎMEL</u>

# **DC and AC Operating Range**

|                                 |      | AT28C16-15T  |

|---------------------------------|------|--------------|

| Operating<br>Temperature (Case) | Com. | 0°C - 70°C   |

|                                 | Ind. | -40°C - 85°C |

| V <sub>CC</sub> Power Supply    |      | 5V ± 10%     |

# **Operating Modes**

| Mode                  | CE              | ŌĒ                            | WE              | I/O              |

|-----------------------|-----------------|-------------------------------|-----------------|------------------|

| Read                  | V <sub>IL</sub> | V <sub>IL</sub>               | V <sub>IH</sub> | D <sub>OUT</sub> |

| Write <sup>(2)</sup>  | V <sub>IL</sub> | V <sub>IH</sub>               | V <sub>IL</sub> | D <sub>IN</sub>  |

| Standby/Write Inhibit | V <sub>IH</sub> | X <sup>(1)</sup>              | Х               | High Z           |

| Write Inhibit         | Х               | Х                             | V <sub>IH</sub> |                  |

| Write Inhibit         | Х               | V <sub>IL</sub>               | X               |                  |

| Output Disable        | Х               | V <sub>IH</sub>               | X               | High Z           |

| Chip Erase            | V <sub>IL</sub> | V <sub>H</sub> <sup>(3)</sup> | V <sub>IL</sub> | High Z           |

Notes: 1. X can be  $V_{IL}$  or  $V_{IH}$ .

2. Refer to AC Programming Waveforms.

3.  $V_{H} = 12.0V \pm 0.5V.$

# **DC Characteristics**

| Symbol                                               | Parameter                                      | Condition                                                                                        |      | Min | Max | Units |

|------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| I <sub>LI</sub>                                      | Input Load Current                             | $V_{IN} = 0V$ to $V_{CC} + 1V$                                                                   |      |     | 10  | μA    |

| I <sub>LO</sub>                                      | Output Leakage Current                         | $V_{I/O} = 0V$ to $V_{CC}$                                                                       |      |     | 10  | μA    |

| I <sub>SB1</sub>                                     | V <sub>cc</sub> Standby Current CMOS           | $\overline{\text{CE}} = \text{V}_{\text{CC}} - 0.3\text{V} \text{ to } \text{V}_{\text{CC}} + 1$ | .0V  |     | 100 | μA    |

| I <sub>SB2</sub> V <sub>CC</sub> Standby Current TTL |                                                | $\overline{\text{CE}}$ = 2.0V to V <sub>CC</sub> + 1.0V                                          | Com. |     | 2   | mA    |

|                                                      | V <sub>CC</sub> Standby Current TTL            |                                                                                                  | Ind. |     | 3   | mA    |

|                                                      | N. Asting Oursent                              | f = 5 MHz; I <sub>OUT</sub> = 0 mA                                                               | Com. |     | 30  | mA    |

| ICC                                                  | I <sub>CC</sub> V <sub>CC</sub> Active Current |                                                                                                  | Ind. |     | 45  | mA    |

| V <sub>IL</sub>                                      | Input Low Voltage                              |                                                                                                  |      |     | 0.8 | V     |

| V <sub>IH</sub>                                      | Input High Voltage                             |                                                                                                  |      | 2.0 |     | V     |

| V <sub>OL</sub>                                      | Output Low Voltage                             | I <sub>OL</sub> = 2.1 mA                                                                         |      |     | 0.4 | V     |

| V <sub>OH</sub>                                      | Output High Voltage                            | I <sub>OH</sub> = -400 μA                                                                        |      | 2.4 |     | V     |

| PCMCIA Atmel          |                                   |                             | AT28C16-15T |     |       |

|-----------------------|-----------------------------------|-----------------------------|-------------|-----|-------|

| Symbol                | Symbol                            | Parameter                   | Min         | Max | Units |

| t <sub>C</sub> (R)    | t <sub>RC</sub>                   | Read Cycle Time             | 150         |     | ns    |

| t <sub>A</sub> (A)    | t <sub>ACC</sub>                  | Address Access Time         |             | 150 | ns    |

| t <sub>A</sub> (CE)   | t <sub>CE</sub> <sup>(1)</sup>    | CE Access Time              |             | 150 | ns    |

| t <sub>A</sub> (OE)   | t <sub>OE</sub> <sup>(2)</sup>    | OE Access Time              | 0           | 75  | ns    |

| t <sub>EN</sub> (CE)  | t <sub>Lz</sub> <sup>(4)</sup>    | Output Enable Time From CE  | 0           |     | ns    |

| t <sub>EN</sub> (OE)  | t <sub>OLZ</sub> <sup>(4)</sup>   | Output Enable Time From OE  | 0           |     | ns    |

| t <sub>v</sub> (A)    | t <sub>OH</sub>                   | Output Hold Time            | 0           |     | ns    |

| t <sub>DIS</sub> (CE) | t <sub>DF</sub> <sup>(3)(4)</sup> | Output Disable Time From CE | 0           | 50  | ns    |

| t <sub>DIS</sub> (OE) | t <sub>DF</sub> <sup>(3)(4)</sup> | Output Disable Time From OE | 0           | 50  | ns    |

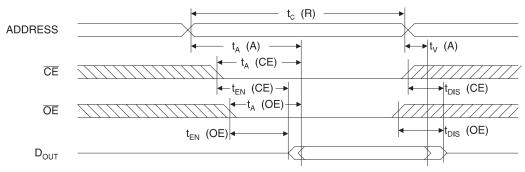

## **AC Read Characteristics**

## AC Read Waveforms<sup>(1)(2)(3)(4)</sup>

- Notes: 1.  $\overline{CE}$  may be delayed up to  $t_{ACC}$   $t_{CE}$  after the address transition without impact on  $t_{ACC}$ .

- OE may be delayed up to t<sub>CE</sub> t<sub>OE</sub> after the falling edge of CE without impact on t<sub>CE</sub> or by t<sub>ACC</sub> t<sub>OE</sub> after an address change without impact on t<sub>ACC</sub>.

- 3.  $t_{DF}$  is specified from  $\overline{OE}$  or  $\overline{CE}$  whichever occurs first (C<sub>L</sub> = 5 pF).

- 4. This parameter is characterized and is not 100% tested.

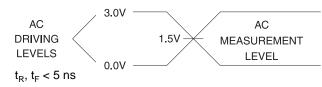

#### Input Test Waveforms and Measurement Level

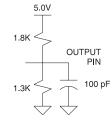

## **Output Test Load**

# **Pin Capacitance**

$f = 1 \text{ MHz}, T = 25^{\circ}C^{(1)}$

| Symbol           | Тур | Max | Units | Conditions     |

|------------------|-----|-----|-------|----------------|

| C <sub>IN</sub>  | 4   | 6   | pF    | $V_{IN} = 0V$  |

| C <sub>OUT</sub> | 8   | 12  | pF    | $V_{OUT} = 0V$ |

Note: 1. This parameter is characterized and is not 100% tested.

## **AC Write Characteristics**

| PCMCIA<br>Symbol        | Atmel<br>Symbol  | Parameter                                       | Min | Мах  | Units |

|-------------------------|------------------|-------------------------------------------------|-----|------|-------|

| t <sub>SU</sub> (A)     | t <sub>AS</sub>  | Address Setup Time                              | 10  |      | ns    |

| t <sub>SU</sub> (OE-WE) | t <sub>OES</sub> | Output Disable Time To WE                       | 10  |      | ns    |

| t <sub>SU</sub> (CE-WE) | t <sub>CS</sub>  | Chip Enable Time To WE                          | 0   |      | ns    |

| t <sub>w</sub> (WE)     | t <sub>WP</sub>  | Write Enable Pulse Width                        | 100 | 1000 | ns    |

| t <sub>SU</sub> (D-WEH) | t <sub>DS</sub>  | Data Setup To WE High                           | 50  |      | ns    |

| t <sub>H</sub> (A)      | t <sub>AH</sub>  | Address Hold Time From WE                       | 50  |      | ns    |

| t <sub>H</sub> (D)      | t <sub>DH</sub>  | Data Hold Time From $\overline{\text{WE}}$ High | 10  |      | ns    |

| t <sub>H</sub> (OE-WE)  | t <sub>OEH</sub> | Output Enable Hold Time From WE High            | 10  |      | ns    |

| t <sub>H</sub> (CE-WE)  | t <sub>CH</sub>  | Chip Enable Hold Time From WE High              | 0   |      | ns    |

| t <sub>D</sub> (B)      | t <sub>DB</sub>  | Delay From WE High To BUSY Asserted             |     | 50   | ns    |

| t <sub>C</sub> (W)      | t <sub>WC</sub>  | Write Cycle Time                                |     | 1    | ms    |

# **AC Write Waveforms**

# Data Polling Waveforms

Note: 1. Data Polling AC Timing Characteristics are the same as the AC Read Characteristics.

### **Chip Erase Waveforms**

$$\begin{split} t_S &= t_H = 1 \; \mu \text{sec (min.)} \\ t_W &= 10 \; \text{msec (min.)} \\ V_H &= 12.0 \pm 0.5 V \end{split}$$

# **Ordering Information**

| t <sub>ACC</sub> | I <sub>CC</sub> (mA) |         |               |         |                               |

|------------------|----------------------|---------|---------------|---------|-------------------------------|

| (ns)             | Active               | Standby | Ordering Code | Package | <b>Operation Range</b>        |

| 150              | 30                   | 0.1     | AT28C16-15TC  | 28T     | Commercial<br>(0°C to 70°C)   |

|                  | 45                   | 0.1     | AT28C16-15TI  | 28T     | Industrial<br>(-40°C to 85°C) |

Notes: 1. See Valid Part Numbers table below.

2. The 28C16 200 ns and 250 ns speed selections have been removed from valid selections table and are replaced by the faster 150 ns  $T_{AA}$  offering.

## **Valid Part Numbers**

The following table lists standard Atmel products that can be ordered.

| Device Numbers | Speed | Package and Temperature Combinations |  |

|----------------|-------|--------------------------------------|--|

| AT28C16        | 15    | TC, TI                               |  |

# **Die Products**

Reference Section: Parallel EEPROM Die Products

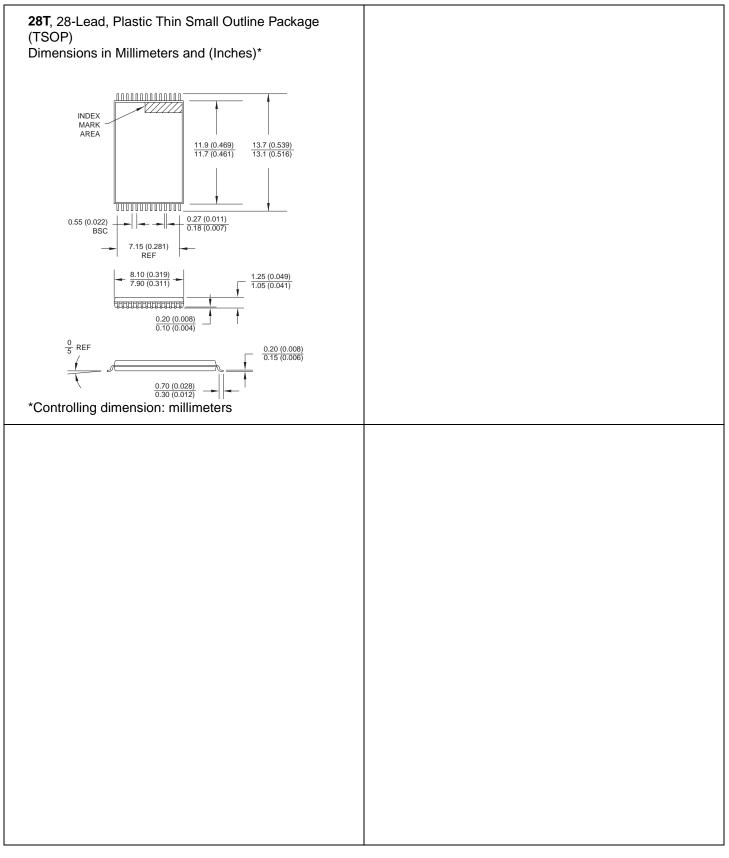

|     | Package Type                                       |

|-----|----------------------------------------------------|

| 28T | 28-Lead, Plastic Thin Small Outline Package (TSOP) |

# AT28C16-T

AT28C16-T

## **Packaging Information**

# AT28C16-T

#### **Atmel Headquarters**

#### Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131

TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel U.K., Ltd. Coliseum Business Centre Riverside Way Camberley, Surrey GU15 3YL England TEL (44) 1276-686677 FAX (44) 1276-686697

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon, Hong Kong TEL (852) 27219778 FAX (852) 27221369

#### Japan

Atmel Japan K.K. Tonetsu Shinkawa Bldg., 9F 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

#### Atmel Colorado Springs

1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4 42 53 60 00 FAX (33) 4 42 53 60 01

#### Fax-on-Demand

North America: 1-(800) 292-8635 International: 1-(408) 441-0732

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

**BBS** 1-(408) 436-4309

#### © Atmel Corporation 1998.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's website. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Marks bearing <sup>®</sup> and/or <sup>™</sup> are registered trademarks and trademarks of Atmel Corporation.

Terms and product names in this document may be trademarks of others.