### Features

- Usable for Automotive 12 V/24 V and Industrial Applications

- Maximum High-speed Data Transmissions up to 1 MBaud

- Fully Compatible with ISO 11898

- Controlled Slew Rate

- Standby Mode

- TXD Input Compatible to 3.3 V

- Short-circuit Protection

- Overtemperature Protection

- High Voltage Bus Lines Protection, -40 V to +40 V

- High Speed Differential Receiver Stage with a Wide Common Mode Range,

- -10 V to +10 V, for High Electromagnetic Immunity (EMI)

- Fully Controlled Bus Lines, CANH and CANL to Minimize Electromagnetic Emissions (EME)

- High ESD Protection at CANH, CANL HBM 8 kV, MM 300 V

## Description

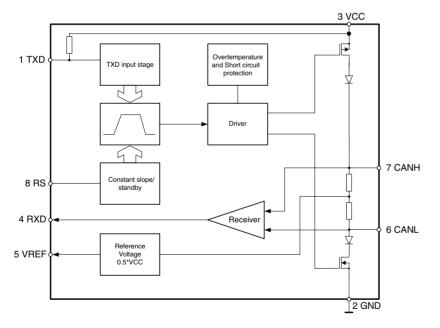

The ATA6660 is a monolithic circuit based on the Atmel's Smart Power BCD60-III technology. It is especially designed for high speed CAN-Controller (CAN-C) differential mode data transmission between CAN-Controllers and the physical differential bus lines.

Figure 1. Block Diagram

High-speed CAN Transceiver

# ATA6660

Rev. 4582B-BCD-03/03

## **Pin Configuration**

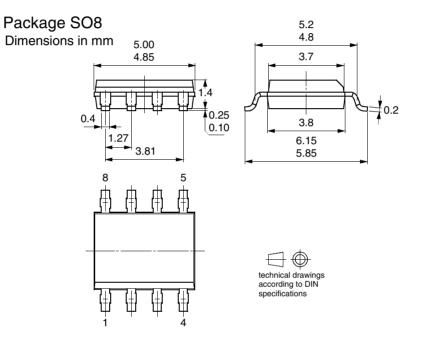

Figure 2. Pinning SO8

|       |   | $\bigcirc$ |   |        |

|-------|---|------------|---|--------|

| TXD 🗆 |   |            | 8 | 🗆 RS   |

| GND 🗆 |   |            | 7 |        |

| VCC 🗆 | 3 |            | 6 |        |

| RXD 🗆 | 4 |            | 5 | □ VREF |

## **Pin Description**

| Pin | Symbol | Function                            |

|-----|--------|-------------------------------------|

| 1   | TXD    | Transmit data input                 |

| 2   | GND    | Ground                              |

| 3   | VCC    | Supply voltage                      |

| 4   | RXD    | Receive data output                 |

| 5   | VREF   | Reference voltage output            |

| 6   | CANL   | Low level CAN voltage input/output  |

| 7   | CANH   | High level CAN voltage input/output |

| 8   | RS     | Switch standby mode/normal mode     |

| Functional<br>Description  | The ATA6660 is a monolithic circuit based on Atmel's Smart Power BCD60-III technol-<br>ogy. It is especially designed for high-speed differential mode data transmission in harsh<br>environments like automotive and industrial applications. Baudrate can be adjusted up<br>to 1 Mbaud. The ATA6660 is fully compatible to the ISO11898, the developed standard<br>for high speed CAN-C (Controller Area Network) communication. |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage Protection and ESD | High voltage protection circuitry on both line pins, CANH (Pin 7) and CANL (Pin 6), allow<br>bus line voltages in the range of -40 V to +40 V. ESD protection circuitry on line pins<br>allow HBM = 8 kV, MM = 300 V. The implemented high voltage protection on bus line<br>output/input pins (7/6) makes the ATA6660 suitable for 12 V automotive applications as<br>well as 24 V automotive applications.                       |

| Slope Control              | A fixed slope is adjusted to prevent unsymmetrical transients on bus lines causing EMC problems. Controlled bus lines, both CANH and CANL signal, will reduce radio frequency interference to a minimum. In well designed bus configurations the filter design costs can be reduced dramatically.                                                                                                                                  |

| Overcurrent Protection     | In the case of a line shorts, like CANH to GND, CANL to VCC, integrated short current limitation allows a maximum current of $I_{CANH_SC}$ or $I_{CANL_SC}$ . If junction temperature rises above 165°C an internal overtemperature protection circuitry shuts down both output stages, the receiver will stay activated.                                                                                                          |

| Standby Mode                 | The ATA6660 can be switched to standby mode by forcing the voltage VRS > 0.87 × VCC. In standby mode the supply current will reduce dramatically, supply current during standby mode is typical 600 $\mu$ A ( $I_{VCC\_stby}$ ). Transmitting data function will not be supported, but the oppertunity will remain to receive data. A high-speed comparator is listening for activities on the bus. A dominant bus signal will force the output RXD to a low level in typical t <sub>dRXDL</sub> = 400 ns. If the RS pin is not connected, causing through a broken connection to the controller, the ATA6660 will switch to standby mode automatically. |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-speed Receiver          | In normal mode a fast receiver circuitry combined with a resistor network is able to detect differential bus line voltages $V_{rec_th} > 0.9$ V as dominant bit, differential bus line voltages $V_{rec_th} < 0.5$ V as recessive bit.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                              | The wide receiver common mode range, -10 V to +10 V, combined with a symmetrical differential receiver stage offers high immunity against electromagnetic interference. A typical hysteresis of 70 mV is implemented. Dominant differential bus voltages forces RXD output (Pin 4) to low level, recessive differential bus voltages to high level.                                                                                                                                                                                                                                                                                                      |

| TXD Input                    | The input stage Pin 1 (TXD) is compatible for 3.3 V output levels from new controller families. Pull-up resistance (25 k $\Omega$ ) forces the IC to recessive mode, if TXD-Pin is not connected. TXD low signal drives the transmitter into dominant state.                                                                                                                                                                                                                                                                                                                                                                                             |

| Transmitter                  | A integrated complex compensation technique allows stable data transmission up to 1 MBaud. Low level on TXD input forces bus line voltages CANH to 3.5 V, CANL to 1.5 V with a termination resistor of 60 $\Omega$ . In the case of a line short circuit, like CANH to GND, CANL to VCC, integrated short current limitation circuitry allows a maximum current of 150 mA. If junction temperature rises above typical 163°C an internal overtemperature protection shuts down both output stages, the receive mode will stay activated.                                                                                                                 |

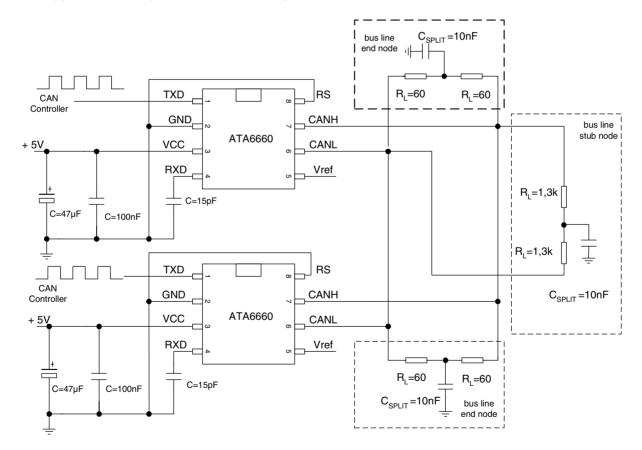

| Split Termination<br>Concept | With a modified bus termination (see Figure 5) a reduction of emission and a higher immunity of the bus system can be achieved. The one 120 $\Omega$ resistor at the bus line end nodes is split into two resistors of equal value, i.e., two resistors of 60 $\Omega$ . The resistors for the stub nodes is recommended with two resistors of 1,3 k $\Omega$ . (for example 8 stub nodes and 2 bus end nodes) Notice: The bus load of all the termination resistors has to stay within the range of 50 $\Omega$ to 65 $\Omega$ .                                                                                                                        |

|                              | The common mode signal at the centre tap of the termination is connected to ground via a capacitor of e.g., $C_{split} = 10 \text{ nF}$ to 100 nF. A seperate ground lead to the ground pin of the module connector is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                      |

## **Absolute Maximum Ratings**

| Parameters                        | Symbol                                                                      | Conditions                                       | Min.          | Max.                 | Unit   |

|-----------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|---------------|----------------------|--------|

| Supply voltage                    | V <sub>CC</sub>                                                             |                                                  | -0.3          | +6                   | V      |

| DC voltage at Pins 1, 4, 5 and 8  | V <sub>TXD</sub> , V <sub>REF</sub> , V <sub>RS</sub> ,<br>V <sub>RXD</sub> |                                                  | -0.3          | V <sub>CC</sub> +0.3 | V      |

| DC voltage at Pins 6 and 7        | V <sub>CANH</sub> , V <sub>CANL</sub>                                       | 0 V < V <sub>CC</sub> < 5.25 V;<br>no time limit | -40.0         | +40.0                | V      |

| Transient voltage at Pins 6 and 7 |                                                                             |                                                  | -150          | +100                 | V      |

| Storage temperature               | T <sub>Stg</sub>                                                            |                                                  | -55           | +150                 | °C     |

| Operating ambient temperature     | T <sub>amb</sub>                                                            |                                                  | -40           | +125                 | °C     |

| ESD classification                | All pins                                                                    | HBM ESD S.5.1<br>MM JEDEC A115A                  | ±3000<br>±200 |                      | V<br>V |

| ESD classification                | Pin 6, 7 versus<br>Pin 2                                                    | HBM 1.5 kΩ, 100 pF<br>MM 0Ω, 200 pF              | ±8000<br>±300 |                      | V<br>V |

## **Thermal Resistance**

| Parameters                                  | Symbol            | Value | Unit |

|---------------------------------------------|-------------------|-------|------|

| Thermal resistance from junction to ambient | R <sub>thJA</sub> | 160   | K/W  |

### **Truth Table**

| VCC              | TXD             | RS                     | CANH               | CANL               | Bus State | RXD |

|------------------|-----------------|------------------------|--------------------|--------------------|-----------|-----|

| 4.75 V to 5.25 V | 0               | $< 0.3 \times V_{CC}$  | 3.5 V              | 1.5 V              | Dominant  | 0   |

| 4.75 V to 5.25 V | 1 (or floating) | $< 0.3 \times V_{CC}$  | $0.5 	imes V_{CC}$ | $0.5 	imes V_{CC}$ | Recessive | 1   |

| 4.75 V to 5.25 V | Х               | $> 0.87 \times V_{CC}$ | $0.5 	imes V_{CC}$ | $0.5 	imes V_{CC}$ | Recessive | 1   |

## **RS (Pin 8) Functionality**

| Slope Control Mode                |                        | Voltage and Current Levels |

|-----------------------------------|------------------------|----------------------------|

| $V_{RS} > 0.87 \times V_{CC}$     | Standby                | I <sub>RS</sub> < Ι 10 μΑ  |

| $V_{\rm RS}$ < 0.3 × $V_{\rm CC}$ | Constant slope control | $I_{RS} \le 500 \ \mu A$   |

## **Electrical Characteristics**

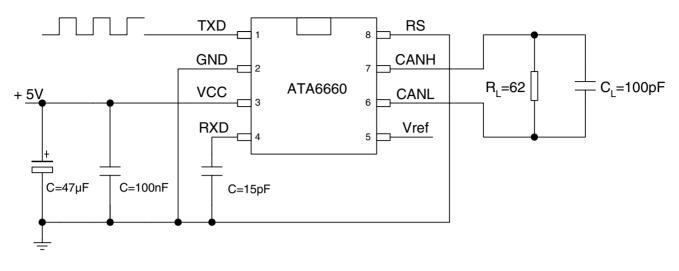

$V_{CC}$  = 4.75 V to 5.25 V;  $T_{amb}$  = -40°C to +125°C;  $R_{Bus}$  = 60  $\Omega$ ; unless otherwise specified All voltages referenced to ground (Pin 2); positive input current.

| No. | Parameters                                                 | Test Conditions                                                                                       | Pin  | Symbol                                   | Min.                 | Тур. | Max.                 | Unit | Туре |

|-----|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------------------------------------------|----------------------|------|----------------------|------|------|

| 1   | Supply Current                                             |                                                                                                       |      |                                          |                      |      |                      |      | 1    |

| 1.1 | Supply current dominant                                    | V <sub>TXD</sub> = 0 V<br>V <sub>RS</sub> = 0 V                                                       | 3    | I <sub>vcc_dom</sub>                     |                      | 45   | 60                   | mA   | A    |

| 1.2 | Supply current recessive                                   | V <sub>TXD</sub> = 5 V<br>V <sub>RS</sub> = 0 V                                                       | 3    | I <sub>vcc_rec</sub>                     |                      | 10   | 15                   | mA   | Α    |

| 1.3 | Supply current stand-<br>by                                | V <sub>RS</sub> = 5 V                                                                                 | 3    | I <sub>vcc_stby</sub>                    |                      | 600  | 980                  | μA   | Α    |

| 2   | Transmitter Data Inpu                                      | t TXD                                                                                                 |      |                                          |                      |      |                      |      |      |

| 2.1 | HIGH level input<br>voltage                                | V <sub>TXD</sub> = 5 V<br>V <sub>RS</sub> = 0 V                                                       | 1    | $V_{TXDH}$                               | 2                    |      | V <sub>CC</sub> +0.3 | V    | A    |

| 2.2 | LOW level input voltage                                    | V <sub>TXD</sub> = 0 V<br>V <sub>RS</sub> = 0 V                                                       | 1    | $V_{TXDL}$                               | -0.3                 |      | +1                   | V    | A    |

| 2.3 | HIGH level input<br>current                                | $V_{TXD} = V_{CC}$                                                                                    | 1    | I <sub>IH</sub>                          | -1                   |      | 0                    | μA   | A    |

| 2.4 | LOW level input voltage                                    | V <sub>TXD</sub> = 0 V                                                                                | 1    | I <sub>IL</sub>                          | -500                 |      | -50                  | μA   | Α    |

| 3   | Receiver Data Output                                       | RXD                                                                                                   | • •  |                                          |                      |      |                      |      |      |

| 3.1 | High level output voltage                                  | I <sub>RXD</sub> = -100 μA                                                                            | 4    | V <sub>RXDH</sub>                        | $0.8 \times V_{CC}$  |      | V <sub>cc</sub>      | V    | A    |

| 3.2 | Low level output voltage                                   | I <sub>RXD</sub> = 1 mA                                                                               | 4    | V <sub>RXDL</sub>                        | 0                    |      | $0.2 \times V_{CC}$  | V    | A    |

| 3.3 | Short current at RXD                                       | V <sub>TXD</sub> = 5 V<br>V <sub>RXD</sub> = 0 V                                                      | 4    | I <sub>RXDs1</sub>                       | -3                   |      | -1                   | mA   | A    |

| 3.4 | Short current at RXD                                       | $V_{TXD} = 0 V$<br>$V_{RXD} = 5 V$                                                                    | 4    | I <sub>RXDs2</sub>                       | 2                    |      | 6                    | mA   | A    |

| 4   | Reference Output Vol                                       | tage VREF                                                                                             |      |                                          |                      |      |                      |      |      |

| 4.1 | Reference output voltage normal mode                       | VRS = 0 V;<br>-50 μA < I5 < 50 μA                                                                     | 5    | V <sub>ref_no</sub>                      | 0.45 V <sub>CC</sub> | -    | 0.55 V <sub>CC</sub> | V    | Α    |

| 4.2 | Reference output voltage standby mode                      | VRS = 5 V;<br>-5μA < I5 < 5 μA                                                                        | 5    | $V_{ref\_stby}$                          | $0.4 \times V_{CC}$  | -    | 0.6 V <sub>CC</sub>  | V    | A    |

| 5   | DC Bus Transmitter C                                       | ANH; CANL                                                                                             |      |                                          |                      |      |                      |      |      |

| 5.1 | Recessive bus voltage                                      | $V_{TXD} = V_{CC}$ ; no load                                                                          | 6, 7 | V <sub>CANH</sub> ;<br>V <sub>CANL</sub> | 2.0                  | 2.5  | 3.0                  | V    | A    |

| 5.2 | I <sub>O(CANH)(reces)</sub><br>I <sub>O(CANL)(reces)</sub> | $\begin{array}{l} -40 \ V < V_{CANH;} \\ V_{CANL} < 40 \ V; \\ 0 \ V < V_{CC} < 5.25 \ V \end{array}$ | 6, 7 | I <sub>O_reces</sub>                     | -5                   |      | +5                   | mA   | A    |

| 5.3 | CANH output voltage dominant                               | V <sub>TXD</sub> = 0 V                                                                                | 6, 7 | $V_{CANH}$                               | 2.8                  | 3.5  | 4.5                  | V    | A    |

| 5.4 | CANL output voltage dominant                               | $V_{TXD} = 0 V$                                                                                       | 6, 7 | $V_{CANL}$                               | 0.5                  | 1.5  | 2.0                  | V    | A    |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

## **Electrical Characteristics (Continued)**

$V_{CC} = 4.75$  V to 5.25 V;  $T_{amb} = -40$  °C to +125 °C;  $R_{Bus} = 60 \Omega$ ; unless otherwise specified All voltages referenced to ground (Pin 2); positive input current.

| No. | Parameters                                                                     | Test Conditions                                                              | Pin  | Symbol                                          | Min. | Тур. | Max. | Unit | Type* |

|-----|--------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|-------------------------------------------------|------|------|------|------|-------|

| 5.5 | Differential bus output<br>voltage<br>(V <sub>CANH</sub> – V <sub>CANL</sub> ) |                                                                              | 6, 7 | Vdiff <sub>dom</sub>                            | 1.5  | 2    | 3.0  | V    | A     |

| 5.6 |                                                                                | $V_{TXD} = V_{CC}$ ; no load                                                 | 6, 7 | Vdiff <sub>rec</sub>                            | -500 |      | +50  | mV   | Α     |

| 5.7 | Short-circuit CANH<br>current                                                  | V <sub>CANH</sub> = -10 V<br>TXD = 0 V                                       | 6, 7 | I <sub>CANH_SC</sub>                            | -35  |      | -100 | mA   | A     |

| 5.8 | Short-circuit CANL current                                                     | V <sub>CANL</sub> = 18 V<br>TXD = 0 V                                        | 6, 7 | I <sub>CANL_SC</sub>                            | 50   | -    | 150  | mA   | A     |

| 6   | DC Bus Receiver CAN                                                            | NH; CANL                                                                     |      |                                                 |      |      |      | •    |       |

| 6.1 | Differential receiver<br>threshold voltage<br>normal mode                      | -10 V < V <sub>CANH</sub> < +10<br>V<br>-10 V < V <sub>CANL</sub> <<br>+10 V | 6, 7 | V <sub>rec_th</sub>                             | 0.5  | 0.7  | 0.9  | V    | A     |

| 6.2 | Differential receiver<br>threshold voltage<br>stand-by mode                    | V <sub>RS</sub> = V <sub>CC</sub>                                            | 6, 7 | V <sub>rec_th_stby</sub>                        | 0.5  | 0.7  | 0.9  | V    | A     |

| 6.3 | Differential input<br>hysteresis                                               |                                                                              | 6, 7 | V <sub>diff(hys)</sub>                          |      | 70   |      | mV   | A     |

| 6.4 | CANH and CANL<br>common mode input<br>resistance                               |                                                                              | 6, 7 | R <sub>i</sub>                                  | 5    | 15   | 25   | kΩ   | A     |

| 6.5 | Differential input resistance                                                  |                                                                              | 6, 7 | R <sub>diff</sub>                               | 10   | 30   | 100  | kΩ   | A     |

| 6.6 | Matching between<br>CANH and CANL<br>common mode input<br>resistance           |                                                                              | 6, 7 | R <sub>i_m</sub>                                | -3   |      | +3   | %    | A     |

| 6.7 | CANH, CANL input capacitance                                                   |                                                                              | 6, 7 | C <sub>i</sub>                                  |      |      | 20   | pF   | D     |

| 6.8 | Differential input capacitance                                                 |                                                                              | 6, 7 | C <sub>diff</sub>                               |      |      | 10   | pF   | D     |

| 6.9 | CANH, CANL input leakage input current                                         | $V_{CC} = 0 V$ $V_{CANH} = 3.5 V$ $V_{CANL} = 1.5 V$                         | 6, 7 | I <sub>li(Canh);</sub><br>I <sub>li(Canl)</sub> |      |      | 250  | μA   | A     |

| 7   | Thermal Shut-down                                                              |                                                                              |      |                                                 |      |      |      |      |       |

| 7.1 | Shut-down junction<br>temperature for<br>CANH/CANL                             |                                                                              |      | T <sub>J(SD)</sub>                              | 150  | 163  | 175  | °C   | В     |

| 7.2 | Switch on junction<br>temperature for<br>CANH/CANL                             |                                                                              |      | T <sub>J(SD)</sub>                              | 140  | 154  | 165  | °C   | В     |

| 7.3 | Temperature<br>hysteresis                                                      |                                                                              |      | T <sub>Hys</sub>                                |      | 10   |      | К    | В     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

6

### **Electrical Characteristics (Continued)**

$V_{CC} = 4.75 \text{ V}$  to 5.25 V;  $T_{amb} = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ;  $R_{Bus} = 60 \Omega$ ; unless otherwise specified All voltages referenced to ground (Pin 2); positive input current.

| No.  | Parameters                                                                                                     | Test Conditions                                                   | Pin                  | Symbol                              | Min.                 | Тур. | Max.                | Unit | Type* |

|------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|-------------------------------------|----------------------|------|---------------------|------|-------|

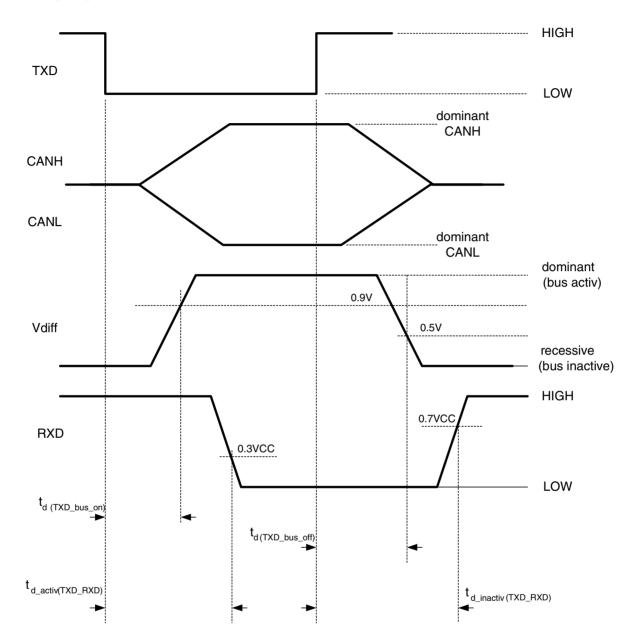

| 8    | Timing Characteristic                                                                                          | s Normal Mode , V <sub>RS</sub> ≤0                                | ).3 ×V <sub>cc</sub> | ; (see Figure 3                     | )                    | 1    | I.                  | 1    |       |

| 8.1  | Delay TXD to bus active                                                                                        | V <sub>RS</sub> = 0 V                                             |                      | t <sub>d(TXD-</sub><br>BUS_ON)      |                      | 120  | 180                 | ns   | A     |

| 8.2  | Delay TXD to bus<br>inactive                                                                                   | V <sub>RS</sub> = 0 V                                             |                      | t <sub>d(TXD-</sub><br>BUS_OFF)     |                      | 50   | 100                 | ns   | A     |

| 8.3  | Delay TXD to RXD, recessive to dominant                                                                        | V <sub>RS</sub> = 0 V                                             | 6, 7                 | t <sub>d_activ(TXD-</sub><br>RXD)   |                      | 200  | 420                 | ns   | A     |

| 8.4  | Delay TXD to RXD,<br>dominant to recessive                                                                     | V <sub>RS</sub> = 0 V                                             |                      | t <sub>d_inactiv(TXD-</sub><br>RXD) |                      | 180  | 460                 | ns   | A     |

| 8.5  | Difference between<br>Delay TXD to RXD<br>dominant to Delay<br>recessive                                       | $t_{diff} = t_{d\_activ(TXD-RXD)}$<br>- $t_{d\_inactiv(TXD-RXD)}$ |                      | t <sub>diff</sub>                   | -280                 |      | 80                  | ns   | A     |

| 9    | Timing Characteristic                                                                                          | s Stand-by Mode V <sub>RS</sub> ≥                                 | 0.87 × V             | сс                                  |                      |      |                     |      |       |

| 9.1  | Bus dominant to RXD low in stand-by mode                                                                       | $V_{RS} = V_{CC}$                                                 | 4                    | t <sub>dRxDL</sub>                  | -                    | 300  | 450                 | ns   | A     |

| 9.2  | Wake up time after<br>stand-by mode (time<br>delay between stand-<br>by to normal mode<br>and to bus dominant) | TXD = 0 V<br>VRS from 0 V to V <sub>CC</sub>                      | 6, 7                 | T <sub>wake_up</sub>                |                      |      | 2                   | μs   | A     |

| 10.1 | Standby/Normal Mode                                                                                            | e Selecteable via RS (Pi                                          | n 8)                 |                                     |                      |      |                     |      |       |

| 10.1 | Input voltage for<br>normal mode                                                                               | $V_{RS} = V_{CC}$                                                 | 8                    | V <sub>RS</sub>                     | -                    | -    | $0.3 \times V_{CC}$ | V    | A     |

| 10.2 | Input current for<br>normal mode                                                                               | V <sub>RS</sub> = 0 V                                             | 8                    | I <sub>RS</sub>                     | -700                 |      |                     | μA   | A     |

| 10.3 | Input voltage for<br>stand-by mode                                                                             |                                                                   | 8                    | V <sub>stby</sub>                   | $0.87 \times V_{CC}$ |      |                     | V    | A     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Figure 3. Timing Diagrams

8

Figure 5. Bus Application with Split Termination Concept

## **Ordering Information**

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| ATA6660              | SO8     | _       |

## **Package Information**

### **Atmel Headquarters**

*Corporate Headquarters* 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

### **Microcontrollers**

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

### *Biometrics/Imaging/Hi-Rel MPU/*

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2003.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel<sup>®</sup> is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.