## Features

- Core

- ARM<sup>®</sup> Cortex<sup>®</sup>-M3 revision 2.0 running at up to 84 MHz

- Memory Protection Unit (MPU)

- Thumb<sup>®</sup>-2 instruction set

- 24-bit SysTick Counter

- Nested Vector Interrupt Controller

- Memories

- From 256 to 512 Kbytes embedded Flash, 128-bit wide access, memory accelerator, dual bank

- From 32 to 100 Kbytes embedded SRAM with dual banks

- 16 Kbytes ROM with embedded bootloader routines (UART, USB) and IAP routines

- Static Memory Controller (SMC): SRAM, NOR, NAND support. NAND Flash controller with 4-kbyte RAM buffer and ECC

- System

- Embedded voltage regulator for single supply operation

- POR, BOD and Watchdog for safe reset

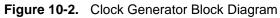

- Quartz or ceramic resonator oscillators: 3 to 20 MHz main and optional low power 32.768 kHz for RTC or device clock.

- High precision 8/12 MHz factory trimmed internal RC oscillator with 4 MHz Default Frequency for fast device startup

- Slow Clock Internal RC oscillator as permanent clock for device clock in low power mode

- One PLL for device clock and one dedicated PLL for USB 2.0 High Speed Mini Host/Device

- Temperature Sensor

- Up to 17 peripheral DMA (PDC) channels and 6-channel central DMA plus dedicated DMA for High-Speed USB Mini Host/Device and Ethernet MAC

- Low Power Modes

- Sleep and Backup modes, down to 2.5 µA in Backup mode.

- Backup domain: VDDBU pin, RTC, eight 32-bit backup registers

- Ultra Low-power RTC

- Peripherals

- USB 2.0 Device/Mini Host: 480 Mbps, 4-kbyte FIFO, up to 10 bidirectional Endpoints, dedicated DMA

- Up to 4 USARTs (ISO7816, IrDA<sup>®</sup>, Flow Control, SPI, Manchester and LIN support) and one UART

- 2 TWI (I2C compatible), up to 6 SPIs, 1 SSC (I2S), 1 HSMCI (SDIO/SD/MMC) with up to 2 slots

- 9-Channel 32-bit Timer/Counter (TC) for capture, compare and PWM mode, Quadrature Decoder Logic and 2-bit Gray Up/Down Counter for Stepper Motor

- Up to 8-channel 16-bit PWM (PWMC) with Complementary Output, Fault Input, 12bit Dead Time Generator Counter for Motor Control

- 32-bit Real Time Timer (RTT) and RTC with calendar and alarm features

- 16-channel 12-bit 1Msps ADC with differential input mode and programmable gain stage

- One 2-channel 12-bit 1 Msps DAC

- One Ethernet MAC 10/100 (EMAC) with dedicated DMA

- Two CAN Controller with eight Mailboxes

- One True Random Number Generator (TRNG)

- Write Protected Registers

- I/O

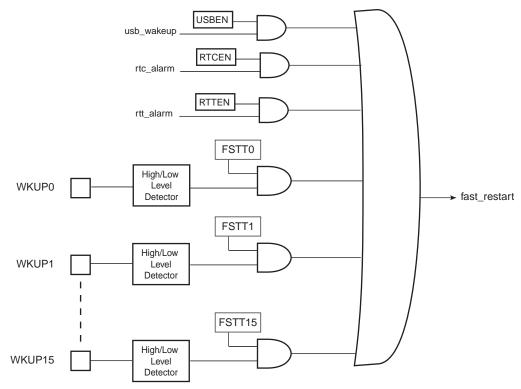

- Up to 103 I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and on-die Series Resistor Termination

- Up to Six 32-bit Parallel Input/Outputs (PIO)

- Packages

- 100-lead LQFP, 14 x 14 mm, pitch 0.5 mm

- 100-ball LFBGA, 9 x 9 mm, pitch 0.8 mm

- 144-lead LQFP, 20 x 20 mm, pitch 0.5 mm

- 144-ball LFBGA, 10 x 10 mm, pitch 0.8 mm

AT91SAM ARM-based Flash MCU

SAM3X SAM3A Series

# Summary

11057BS-ATARM-13-Jul-12

## 1. SAM3X/A Description

Atmel's SAM3X/A series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M3 RISC processor. It operates at a maximum speed of 84 MHz and features up to 512 Kbytes of Flash and up to 100 Kbytes of SRAM. The peripheral set includes a High Speed USB Host and Device port with embedded transceiver, an Ethernet MAC, 2x CANs, a High Speed MCI for SDIO/SD/MMC, an External Bus Interface with NAND Flash controller, 5x UARTs, 2x TWIs, 4x SPIs, as well as 1 PWM timer, 9x general-purpose 32-bit timers, an RTC, a 12-bit ADC and a 12-bit DAC.

The SAM3X/A series is ready for capacitive touch thanks to the QTouch library, offering an easy way to implement buttons, wheels and sliders.

The SAM3X/A architecture is specifically designed to sustain high speed data transfers. It includes a multi-layer bus matrix as well as multiple SRAM banks, PDC and DMA channels that enable it to run tasks in parallel and maximize data throughput.

It operates from 1.62V to 3.6V and is available in 100- and 144-pin QFP and LFBGA packages.

The SAM3X/A devices are particularly well suited for networking applications: industrial and home/building automation, gateways.

## 1.1 Configuration Summary

The SAM3X/A series devices differ in memory sizes, package and features list. Table 1-1 below summarizes the configurations.

| Feature                           | SAM3X8E                                           | SAM3X8C               | SAM3X4E                                           | SAM3X4C               | SAM3A8C               | SAM3A4C               |

|-----------------------------------|---------------------------------------------------|-----------------------|---------------------------------------------------|-----------------------|-----------------------|-----------------------|

| Flash                             | 2 x 256 Kbytes                                    | 2 x 256 Kbytes        | 2 x 128 Kbytes                                    | 2 x 128 Kbytes        | 2 x 256 Kbytes        | 2 x 128 Kbytes        |

| SRAM                              | 64 + 32 Kbytes                                    | 64 + 32 Kbytes        | 32 + 32 Kbytes                                    | 32 + 32 Kbytes        | 64 + 32 Kbytes        | 32 + 32<br>Kbytes     |

| Nand Flash<br>Controller<br>(NFC) | Yes                                               | -                     | Yes                                               | s                     |                       | -                     |

| NFC SRAM <sup>(1)</sup>           | 4K bytes                                          | -                     | 4K bytes                                          | -                     | -                     | -                     |

| Package                           | LQFP144<br>LFBGA144                               | LQFP100<br>LFBGA100   | LQFP144<br>LFBGA144                               | LQFP100<br>LFBGA100   | LQFP100<br>LFBGA100   | LQFP100<br>LFBGA100   |

| Number of<br>PIOs                 | 103                                               | 63                    | 103                                               | 63                    | 63                    | 63                    |

| SHDN<br>Pin                       | Yes                                               | No                    | Yes                                               | No                    | No                    | No                    |

| EMAC                              | MII/RMII                                          | RMII                  | MII/RMII                                          | RMII                  | -                     | -                     |

| External<br>Bus<br>Interface      | 16-bit data,<br>8 chip selects,<br>23-bit address | -                     | 16-bit data,<br>8 chip selects,<br>23-bit address | -                     | -                     | -                     |

| Central DMA                       | 6                                                 | 4                     | 6                                                 | 4                     | 4                     | 4                     |

| 12-bit ADC                        | 16 ch. <sup>(2)</sup>                             | 16 ch. <sup>(2)</sup> | 16 ch. <sup>(2)</sup>                             | 16 ch. <sup>(2)</sup> | 16 ch. <sup>(2)</sup> | 16 ch. <sup>(2)</sup> |

| 12-bit DAC                        | 2 ch.                                             | 2 ch.                 | 2 ch.                                             | 2 ch.                 | 2 ch.                 | 2 ch.                 |

| 32-bit Timer                      | 9 <sup>(5)</sup>                                  | 9 <sup>(6)</sup>      | 9 <sup>(5)</sup>                                  | 9 <sup>(6)</sup>      | 9 <sup>(5)</sup>      | 9 <sup>(5)</sup>      |

| PDC<br>Channels                   | 17                                                | 15                    | 17                                                | 15                    | 15                    | 15                    |

| USART/<br>UART                    | 3/2 <sup>(7)</sup>                                | 3/1                   | 3/2 <sup>(7)</sup>                                | 3/1                   | 3/1                   | 3/1                   |

| SPI <sup>(3)</sup>                | 1/4 + 3                                           | 1/4 + 3               | 1/4 + 3                                           | 1/4 + 3               | 1/4 + 3               | 1/4 + 3               |

| HSMCI                             | 1 slot<br>8 bits                                  | 1 slot<br>4 bits      | 1 slot<br>8 bits                                  | 1 slot<br>4 bits      | 1 slot<br>4 bits      | 1 slot<br>4 bits      |

Table 1-1.

Configuration Summary

Notes: 1. 4 Kbytes RAM buffer of the NAND Flash Controller (NFC) which can be used by the core if not used by the NFC

- 2. One channel is reserved for internal temperature sensor

- 3. 2 / 8 + 4 = Number of SPI Controllers / Number of Chip Selects + Number of USART with SPI Mode

- 4. 9 TC channels are accessible through PIO

- 5. 6 TC channels are accessible through PIO

- 6. 3 TC channels are accessible through PIO

- 7. USART3 in UART mode (RXD3 and TXD3 available)

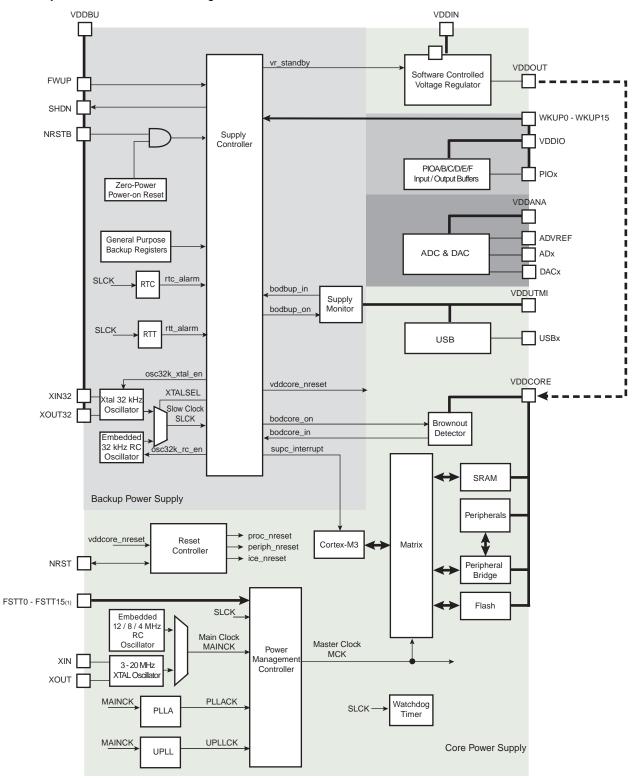

# 2. SAM3X/A Block Diagram

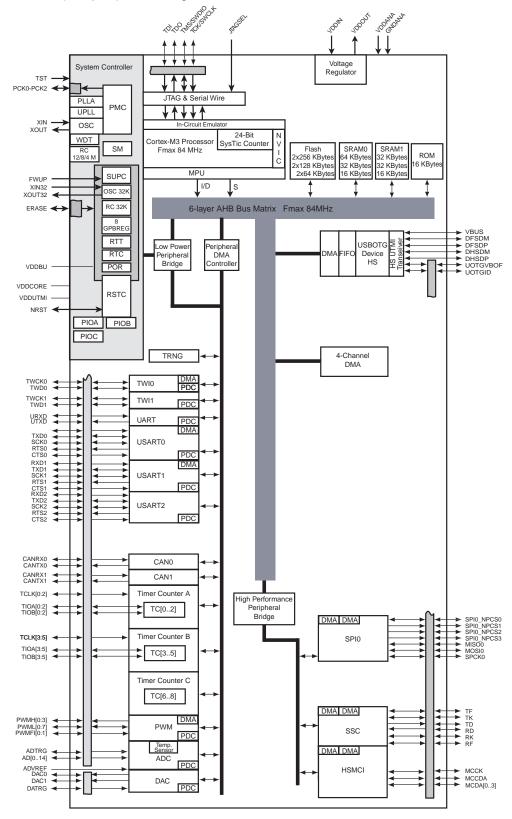

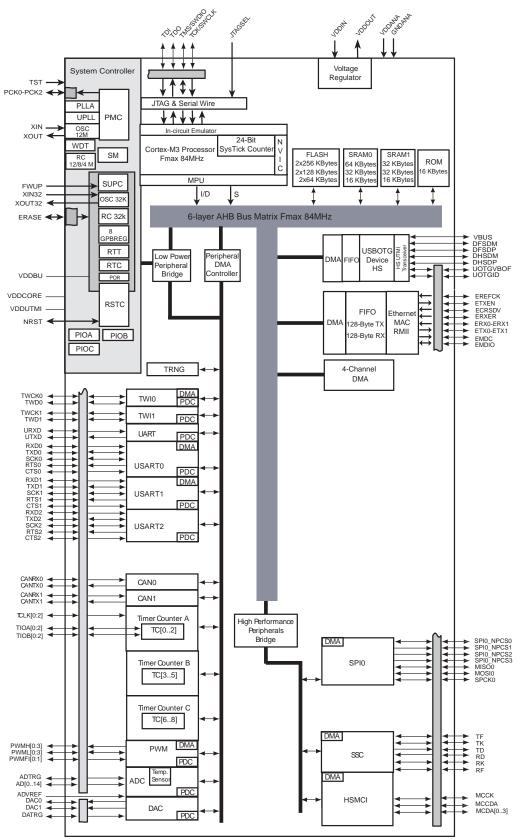

Figure 2-1. SAM3A4/8C (100 pins) Block Diagram

SAM3X/A

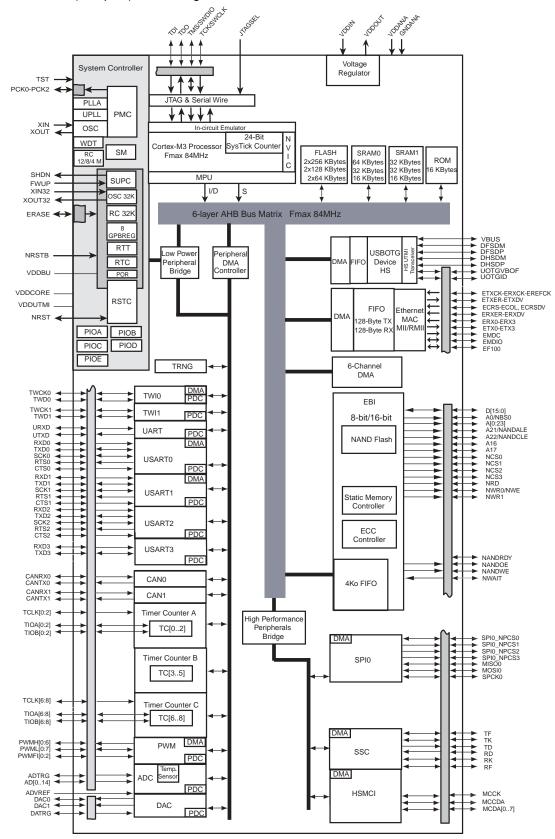

Figure 2-3. SAM3X4/8E (144 pins) Block Diagram

SAM3X/A

# 3. Signal Description

Table 3-1 gives details on the signal names classified by peripheral.

### Table 3-1.Signal Description List

| Signal Name | Function                                       | Туре         | Active<br>Level | Voltage<br>Reference | Comments                                                                                  |

|-------------|------------------------------------------------|--------------|-----------------|----------------------|-------------------------------------------------------------------------------------------|

|             | Power Su                                       | pplies       | I               |                      |                                                                                           |

| VDDIO       | Peripherals I/O Lines Power Supply             | Power        |                 |                      | 1.62V to 3.6V                                                                             |

| VDDUTMI     | USB UTMI+ Interface Power Supply               | Power        |                 |                      | 3.0V to 3.6V                                                                              |

| VDDOUT      | Voltage Regulator Output                       | Power        |                 |                      |                                                                                           |

| VDDIN       | Voltage Regulator, ADC and DAC Power<br>Supply | Power        |                 |                      |                                                                                           |

| GNDUTMI     | USB UTMI+ Interface Ground                     | Ground       |                 |                      |                                                                                           |

| VDDBU       | Backup I/O Lines Power Supply                  | Power        |                 |                      | 1.62V to 3.6V                                                                             |

| GNDBU       | Backup Ground                                  | Ground       |                 |                      |                                                                                           |

| VDDPLL      | PLL A, UPLL and Oscillator Power Supply        | Power        |                 |                      | 1.62 V to 1.95V                                                                           |

| GNDPLL      | PLL A, UPLL and Oscillator Ground              | Ground       |                 |                      |                                                                                           |

| VDDANA      | ADC and DAC Analog Power Supply                | Power        |                 |                      | 2.0V to 3.6V                                                                              |

| GNDANA      | ADC and DAC Analog Ground                      | Ground       |                 |                      |                                                                                           |

| VDDCORE     | Core Chip Power Supply                         | Power        |                 |                      | 1.62V to 1.95V                                                                            |

| GND         | Ground                                         | Ground       |                 |                      |                                                                                           |

|             | Clocks, Oscillato                              | ors and PLLs |                 |                      |                                                                                           |

| XIN         | Main Oscillator Input                          | Input        |                 | VDDPLL               |                                                                                           |

| XOUT        | Main Oscillator Output                         | Output       |                 | VDDPLL               |                                                                                           |

| XIN32       | Slow Clock Oscillator Input                    | Input        |                 | VDDBU                |                                                                                           |

| XOUT32      | Slow Clock Oscillator Output                   | Output       |                 |                      |                                                                                           |

| VBG         | Bias Voltage Reference                         | Analog       |                 |                      |                                                                                           |

| PCK0 - PCK2 | Programmable Clock Output                      | Output       |                 |                      |                                                                                           |

|             | Shutdown, Wa                                   | keup Logic   |                 |                      |                                                                                           |

| SHDN        | Shut-Down Control                              | Output       |                 | VDDBU                | 0: The device is in<br>backup mode<br>1: The device is<br>running (not in<br>backup mode) |

| FWUP        | Force Wake-up Input                            | Input        |                 | VDDBU                | Needs external Pull-<br>up                                                                |

| Signal Name  | Function                                          | Туре           | Active<br>Level | Voltage<br>Reference | Comments                            |  |

|--------------|---------------------------------------------------|----------------|-----------------|----------------------|-------------------------------------|--|

|              | ICE and                                           | JTAG           |                 |                      |                                     |  |

| TCK/SWCLK    | Test Clock/Serial Wire Clock                      | Input          |                 |                      |                                     |  |

| TDI          | Test Data In                                      | Input          |                 |                      | Reset State:                        |  |

| TDO/TRACESWO | Test Data Out / Trace Asynchronous Data<br>Out    | Output         |                 | VDDIO                | - SWJ-DP Mode<br>- Internal pull-up |  |

| TMS/SWDIO    | Test Mode Select /Serial Wire<br>Input/Output     | Input / I/O    |                 |                      | disabled <sup>(1)</sup>             |  |

| JTAGSEL      | JTAG Selection                                    | Input          | High            | VDDBU                | Permanent Internal<br>pull-down     |  |

|              | Flash Me                                          | emory          |                 |                      |                                     |  |

| ERASE        | Flash and NVM Configuration Bits<br>Erase Command | Input          | High            | VDDIO                | Pull-down resistor                  |  |

|              | Reset/                                            | Test           |                 |                      |                                     |  |

| NRST         | Microcontroller Reset                             | I/O            | Low             | VDDIO                | Pull-up resistor                    |  |

| NRSTB        | Asynchronous Microcontroller Reset                | Input          | Low             | VDDBU                | Pull-up resistor                    |  |

| TST          | Test Mode Select                                  | Input          |                 | VDDBU                | Pull-down resistor                  |  |

|              | Universal Asynchronous Re                         | ceiver Transco | eiver - UART    |                      |                                     |  |

| URXD         | UART Receive Data                                 | Input          |                 |                      |                                     |  |

| UTXD         | UART Transmit Data                                | Output         |                 |                      |                                     |  |

| Signal Name | Function                 | Туре                  | Active<br>Level | Voltage<br>Reference | Comments                                                                                      |

|-------------|--------------------------|-----------------------|-----------------|----------------------|-----------------------------------------------------------------------------------------------|

|             | PIO Controller - PI      | OA - PIOB - PIOC - PI | OD - PIOE       |                      |                                                                                               |

| PA0 - PA31  | Parallel IO Controller A | I/O                   |                 |                      | •Schmitt Trigger <sup>(3)</sup><br>Reset State:<br>•PIO Input<br>•Internal pull-up<br>enabled |

| PB0 - PB31  | Parallel IO Controller B | I/O                   |                 | _                    | •Schmitt Trigger <sup>(4)</sup><br>Reset State:<br>•PIO Input<br>•Internal pull-up<br>enabled |

| PC0 - PC30  | Parallel IO Controller C | I/O                   |                 |                      | •Schmitt Trigger <sup>(5)</sup><br>Reset State:<br>•PIO Input<br>•Internal pull-up<br>enabled |

| PD0 - PD30  | Parallel IO Controller D | I/O                   |                 |                      | •Schmitt Trigger <sup>(6)</sup><br>Reset State:<br>•PIO Input<br>•Internal pull-up<br>enabled |

| PE0 - PE31  | Parallel IO Controller E | I/O                   |                 |                      | •Schmitt Trigger <sup>(7)</sup><br>Reset State:<br>•PIO Input<br>•Internal pull-up<br>enabled |

| PF0 - PF6   | Parallel IO Controller F | I/O                   |                 |                      | •Schmitt Trigger <sup>(7)</sup><br>Reset State:<br>•PIO Input<br>•Internal pull-up<br>enabled |

|             | Exte                     | rnal Memory Bus       |                 |                      |                                                                                               |

| D0 - D15    | Data Bus                 | I/O                   |                 |                      | Pulled-up input at reset                                                                      |

| A0 - A23    | Address Bus              | Output                |                 |                      | 0 at reset                                                                                    |

|             | Static Me                | mory Controller - SM  | C               | - 1                  | 1                                                                                             |

| NCS0 - NCS7 | Chip Select Lines        | Output                | Low             |                      |                                                                                               |

| NWR0 - NWR1 | Write Signal             | Output                | Low             |                      |                                                                                               |

| NRD         | Read Signal              | Output                | Low             |                      |                                                                                               |

| NWE         | Write Enable             | Output                | Low             |                      |                                                                                               |

| NBS0 - NBS1 | Byte Mask Signal         | Output                | Low             |                      |                                                                                               |

| NWAIT       | External Wait Signal     | Input                 | Low             |                      |                                                                                               |

| Signal Name   | Function                       | Туре             | Active<br>Level | Voltage<br>Reference           | Comments |

|---------------|--------------------------------|------------------|-----------------|--------------------------------|----------|

|               | NAND Flash                     | Controller-NFC   |                 |                                |          |

| NANDOE        | NAND Flash Output Enable       | Output           | Low             |                                |          |

| NANDWE        | NAND Flash Write Enable        | Output           | Low             |                                |          |

| NANDRDY       | NAND Ready                     | Input            |                 |                                |          |

| NANDCLE       | NAND Flash Command Line Enable | Output           | Low             |                                |          |

| NANDALE       | NAND Flash Address Line Enable | Output           | Low             |                                |          |

|               | High Speed Multimedi           | a Card Interface | e HSMCI         |                                |          |

| MCCK          | Multimedia Card Clock          | I/O              |                 |                                |          |

| MCCDA         | Multimedia Card Slot A Command | I/O              |                 |                                |          |

| MCDA0 - MCDA7 | Multimedia Card Slot A Data    | I/O              |                 |                                |          |

| MCCDB         | Multimedia Card Slot B Command | I/O              |                 |                                |          |

| MCDB0 - MCDB3 | Multimedia Card Slot A Data    | I/O              |                 |                                |          |

|               | Universal Synchronous Asynchro | nous Receiver    | Transmitter     | USARTx                         | 1        |

| SCKx          | USARTx Serial Clock            | I/O              |                 |                                |          |

| TXDx          | USARTx Transmit Data           | I/O              |                 |                                |          |

| RXDx          | USARTx Receive Data            | Input            |                 |                                |          |

| RTSx          | USARTx Request To Send         | Output           |                 |                                |          |

| CTSx          | USARTx Clear To Send           | Input            |                 |                                |          |

|               | Ethernet MAC                   | 10/100 - EMAC    |                 | -                              | 1        |

| EREFCK        | Reference Clock                | Input            |                 | RMII only                      |          |

| ETXCK         | Transmit Clock                 | Input            |                 | MII only                       |          |

| ERXCK         | Receive Clock                  | Input            |                 | MII only                       |          |

| ETXEN         | Transmit Enable                | Output           |                 |                                |          |

| ETX0 - ETX3   | Transmit Data                  | Output           |                 | ETX0 -<br>ETX1 only<br>in RMII |          |

| ETXER         | Transmit Coding Error          | Output           |                 | MII only                       |          |

| ERXDV         | Receive Data Valid             | Input            |                 | MII only                       |          |

| ECRSDV        | Carrier Sense and Data Valid   | Input            |                 | RMII only                      |          |

| ERX0 - ERX3   | Receive Data                   | Input            |                 | ERX0 -<br>ERX1 only<br>in RMII |          |

| ERXER         | Receive Error                  | Input            |                 |                                |          |

| ECRS          | Carrier Sense                  | Input            |                 | MII only                       |          |

| ECOL          | Collision Detected             | Input            |                 | MII only                       |          |

| EMDC          | Management Data Clock          | Output           |                 |                                |          |

| EMDIO         | Management Data Input/Output   | I/O              |                 |                                |          |

| Signal Name                | Function                               | Туре           | Active<br>Level | Voltage<br>Reference | Comments                                                                          |

|----------------------------|----------------------------------------|----------------|-----------------|----------------------|-----------------------------------------------------------------------------------|

| CANRXx                     | CAN Input                              | Input          |                 |                      |                                                                                   |

| CANTXx                     | CAN Output                             | Output         |                 |                      |                                                                                   |

|                            | Synchronous Serial                     | Controller - S | SSC             |                      |                                                                                   |

| TD                         | SSC Transmit Data                      | Output         |                 |                      |                                                                                   |

| RD                         | SSC Receive Data                       | Input          |                 |                      |                                                                                   |

| ТК                         | SSC Transmit Clock                     | I/O            |                 |                      |                                                                                   |

| RK                         | SSC Receive Clock                      | I/O            |                 |                      |                                                                                   |

| TF                         | SSC Transmit Frame Sync                | I/O            |                 |                      |                                                                                   |

| RF                         | SSC Receive Frame Sync                 | I/O            |                 |                      |                                                                                   |

|                            | Timer/Cour                             | iter - TC      | 1               |                      | 1                                                                                 |

| TCLKx                      | TC Channel x External Clock Input      | Input          |                 |                      |                                                                                   |

| TIOAx                      | TC Channel x I/O Line A                | I/O            |                 |                      |                                                                                   |

| TIOBx                      | TC Channel x I/O Line B                | I/O            |                 |                      |                                                                                   |

|                            | Pulse Width Modulation                 | n Controller-  | PWMC            |                      |                                                                                   |

| PWMHx                      | PWM Waveform Output High for channel x | Output         |                 |                      |                                                                                   |

| PWMLx                      | PWM Waveform Output Low for channel x, | Output         |                 |                      | only output in<br>complementary<br>mode when dead<br>time insertion is<br>enabled |

| PWMFIx                     | PWM Fault Input for channel x          | Input          |                 |                      |                                                                                   |

|                            | Serial Peripheral I                    | nterface - SP  | Ix              | ·                    |                                                                                   |

| MISOx                      | Master In Slave Out                    | I/O            |                 |                      |                                                                                   |

| MOSIx                      | Master Out Slave In                    | I/O            |                 |                      |                                                                                   |

| SPCKx                      | SPI Serial Clock                       | I/O            |                 |                      |                                                                                   |

| SPIx_NPCS0                 | SPI Peripheral Chip Select 0           | I/O            | Low             |                      |                                                                                   |

| SPIx_NPCS1 -<br>SPIx_NPCS3 | SPI Peripheral Chip Select             | Output         | Low             |                      |                                                                                   |

|                            | Two-Wire Inter                         | face- TWIx     |                 |                      |                                                                                   |

| TWDx                       | TWIx Two-wire Serial Data              | I/O            |                 |                      |                                                                                   |

| TWCKx                      | TWIx Two-wire Serial Clock             | I/O            |                 |                      |                                                                                   |

|                            | Analog-to-Digital C                    | onverter - Al  | C               |                      |                                                                                   |

| AD0 - AD14                 | Analog Inputs                          | Analog         |                 |                      |                                                                                   |

| ADTRG                      | ADC Trigger                            | Input          |                 |                      |                                                                                   |

| ADVREF                     | ADC and DAC Reference                  | Analog         |                 |                      |                                                                                   |

|                            | Digital-to-Analog C                    | onverter - DA  | CC              | ·                    |                                                                                   |

| DAC0                       | DAC channel 0 analog output            | Analog         |                 |                      |                                                                                   |

| DAC1                       | DAC channel 1 analog output            | Analog         |                 |                      |                                                                                   |

| DATRG                      | DAC Trigger                            |                |                 |                      |                                                                                   |

| Signal Name   | Function                                                  | Туре           | Active<br>Level | Voltage<br>Reference | Comments |

|---------------|-----------------------------------------------------------|----------------|-----------------|----------------------|----------|

|               | Fast Flash Progra                                         | amming Interfa | се              |                      |          |

| PGMEN0-PGMEN2 | Programming Enabling                                      | Input          |                 | VDDIO                |          |

| PGMM0-PGMM3   | Programming Mode                                          | Input          |                 | VDDIO                |          |

| PGMD0-PGMD15  | Programming Data                                          | I/O            |                 | VDDIO                |          |

| PGMRDY        | Programming Ready                                         | Output         | High            | VDDIO                |          |

| PGMNVALID     | Data Direction                                            | Output         | Low             | VDDIO                |          |

| PGMNOE        | Programming Read                                          | Input          | Low             | VDDIO                |          |

| PGMCK         | Programming Clock                                         | Input          |                 | VDDIO                |          |

| PGMNCMD       | Programming Command                                       | Input          | Low             | VDDIO                |          |

|               | USB Mini Host/Devic                                       | e High Speed [ | Device          | <u>+</u>             |          |

| VBUS          | USB Bus Power Measurement Port                            | Analog         |                 |                      |          |

| DFSDM         | USB Full Speed Data -                                     | Analog         |                 | VDDUTMI              |          |

| DFSDP         | USB Full Speed Data +                                     | Analog         |                 | VDDUTMI              |          |

| DHSDM         | USB High Speed Data -                                     | Analog         |                 | VDDUTMI              |          |

| DHSDP         | USB High Speed Data +                                     | Analog         |                 | VDDUTMI              |          |

| UOTGVBOF      | USB VBus On/Off: Bus Power Control<br>Port                |                |                 | VDDIO                |          |

| UOTGID        | USB Identification: Mini Connector<br>Identification Port |                |                 | VDDIO                |          |

Notes: 1. TDO pin is set in input mode when the Cortex-M3 Core is not in debug mode. Thus the internal pull-up corresponding to this PIO line must be enabled to avoid current consumption due to floating input.

2. PIOA: Schmitt Trigger on all, except PA0, PA9, PA26, PA29, PA30, PA31

- 3. PIOB: Schmitt Trigger on all, except PB14 and PB22

- 4. PIOC: Schmitt Trigger on all, except PC2 to PC9, PC15 to PC24

- 5. PIOD: Schmitt Trigger on all, except PD10 to PD30

- 6. PIOE: Schmitt Trigger on all, except PE0 to PE4, PE15, PE17, PE19, PE21, PE23, PE25, PE29

- 7. PIOF: Schmitt Trigger on all PIOs

#### 3.1 Design Considerations

In order to facilitate schematic capture when using a SAM3X/A design, Atmel provides a "Schematics Checklist" Application Note. See http://www.atmel.com/products/AT91/

## 4. Package and Pinout

### 4.1 SAM3A4/8C and SAM3X4/8C Package and Pinout

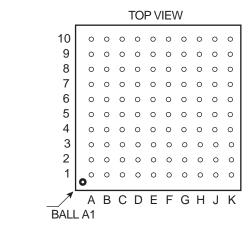

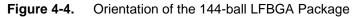

The SAM3A4/8C and SAM3X4/8C are available in 100-lead LQFP and 100-ball LFBGA packages.

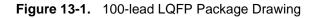

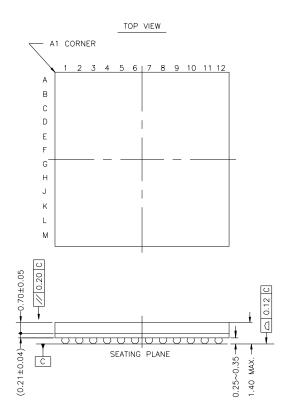

## 4.1.1 100-lead LQFP Package Outline

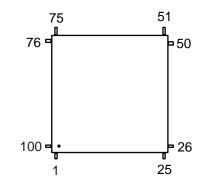

Figure 4-1. Orientation of the 100-lead LQFP Package

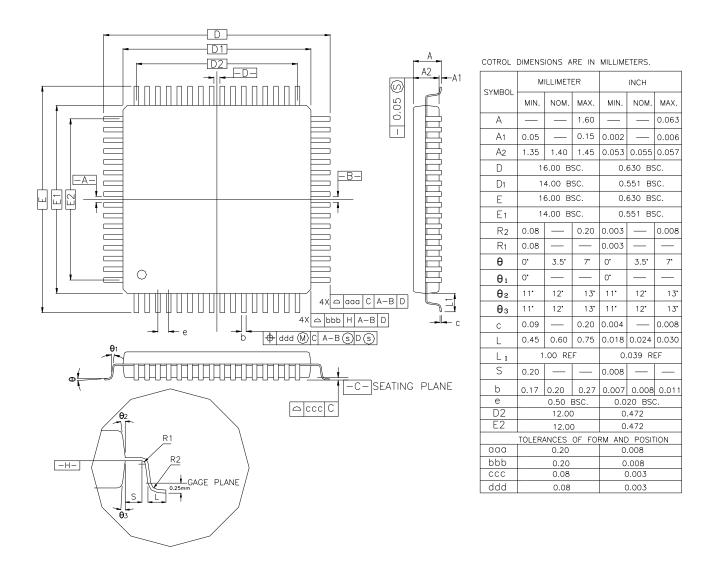

#### 4.1.2 100-ball LFBGA Package Outline

### Figure 4-2. Orientation of the 100-ball LFBGA Package

#### 4.1.3 100-lead LQFP Pinout

| 1  | PB26    | 26 | DHSDP   | 51 | VDDANA  | 76  | PA26    |

|----|---------|----|---------|----|---------|-----|---------|

| 2  | PA9     | 27 | DHSDM   | 52 | GNDANA  | 77  | PA27    |

| 3  | PA10    | 28 | VBUS    | 53 | ADVREF  | 78  | PA28    |

| 4  | PA11    | 29 | VBG     | 54 | PB15    | 79  | PA29    |

| 5  | PA12    | 30 | VDDUTMI | 55 | PB16    | 80  | PB0     |

| 6  | PA13    | 31 | DFSDP   | 56 | PA16    | 81  | PB1     |

| 7  | PA14    | 32 | DFSDM   | 57 | PA24    | 82  | PB2     |

| 8  | PA15    | 33 | GNDUTMI | 58 | PA23    | 83  | PB3     |

| 9  | PA17    | 34 | VDDCORE | 59 | PA22    | 84  | PB4     |

| 10 | VDDCORE | 35 | JTAGSEL | 60 | PA6     | 85  | PB5     |

| 11 | VDDIO   | 36 | XIN32   | 61 | PA4     | 86  | PB6     |

| 12 | GND     | 37 | XOUT32  | 62 | PA3     | 87  | PB7     |

| 13 | PA0     | 38 | TST     | 63 | PA2     | 88  | PB8     |

| 14 | PA1     | 39 | VDDBU   | 64 | PB12    | 89  | VDDCORE |

| 15 | PA5     | 40 | FWUP    | 65 | PB13    | 90  | VDDIO   |

| 16 | PA7     | 41 | GND     | 66 | PB17    | 91  | GND     |

| 17 | PA8     | 42 | VDDOUT  | 67 | PB18    | 92  | PB9     |

| 18 | PB28    | 43 | VDDIN   | 68 | PB19    | 93  | PB10    |

| 19 | PB29    | 44 | GND     | 69 | PB20    | 94  | PB11    |

| 20 | PB30    | 45 | VDDCORE | 70 | PB21    | 95  | PC0     |

| 21 | PB31    | 46 | PB27    | 71 | VDDCORE | 96  | PB14    |

| 22 | GNDPLL  | 47 | NRST    | 72 | VDDIO   | 97  | PB22    |

| 23 | VDDPLL  | 48 | PA18    | 73 | GND     | 98  | PB23    |

| 24 | XOUT    | 49 | PA19    | 74 | PA21    | 99  | PB24    |

| 25 | XIN     | 50 | PA20    | 75 | PA25    | 100 | PB25    |

## Table 4-1. 100-lead LQFP SAM3A4/8C and SAM3X4/8C Pinout

### 4.1.4 100-ball LFBGA Pinout

| A1  | PB26 | C6  | PB11    | F1  | VDDPLL  | H6  | NRST    |

|-----|------|-----|---------|-----|---------|-----|---------|

| A2  | PB24 | C7  | PB8     | F2  | GNDPLL  | H7  | PA19    |

| A3  | PB22 | C8  | PB4     | F3  | PB30    | H8  | PA4     |

| A4  | PB14 | C9  | PB0     | F4  | PB29    | H9  | PA6     |

| A5  | PC0  | C10 | PA25    | F5  | GND     | H10 | PA22    |

| A6  | PB9  | D1  | PA5     | F6  | GND     | J1  | VBUS    |

| A7  | PB6  | D2  | PA0     | F7  | VDDIO   | J2  | DHSDP   |

| A8  | PB2  | D3  | PA1     | F8  | PB13    | J3  | DHSDM   |

| A9  | PA28 | D4  | VDDCORE | F9  | PB17    | J4  | JTAGSEL |

| A10 | PA26 | D5  | VDDIO   | F10 | PB18    | J5  | XIN32   |

| B1  | PA11 | D6  | VDDCORE | G1  | XOUT    | J6  | VDDIN   |

| B2  | PB25 | D7  | VDDCORE | G2  | VDDUTMI | J7  | PA23    |

| B3  | PB23 | D8  | PB5     | G3  | PB31    | J8  | PA24    |

| B4  | PA10 | D9  | PB1     | G4  | GNDBU   | J9  | PB16    |

| B5  | PA9  | D10 | PA21    | G5  | PB27    | J10 | PA16    |

| B6  | PB10 | E1  | PB28    | G6  | PA18    | K1  | VBG     |

| B7  | PB7  | E2  | PA7     | G7  | PA20    | K2  | DFSDP   |

| B8  | PB3  | E3  | PA8     | G8  | PA3     | K3  | DFSDM   |

| B9  | PA29 | E4  | VDDCORE | G9  | PA2     | K4  | VDDCORE |

| B10 | PA27 | E5  | GND     | G10 | PB12    | K5  | XOUT32  |

| C1  | PA12 | E6  | GND     | H1  | XIN     | K6  | VDDOUT  |

| C2  | PA14 | E7  | VDDIO   | H2  | GNDUTMI | K7  | VDDANA  |

| C3  | PA13 | E8  | PB19    | H3  | TST     | K8  | GNDANA  |

| C4  | PA17 | E9  | PB20    | H4  | VDDBU   | K9  | ADVREF  |

| C5  | PA15 | E10 | PB21    | H5  | WAKEUP  | K10 | PB15    |

Table 4-2.

100-ball LFBGA SAM3X4/8E Package and Pinout

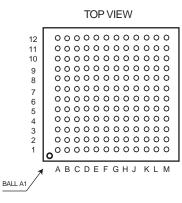

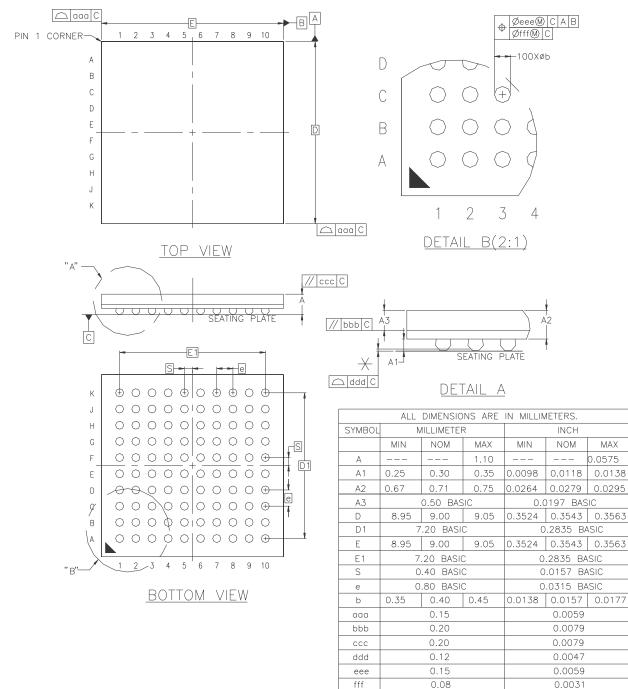

## 4.2 SAM3X4/8E Package and Pinout

The SAM3X4/8E is available in 144-lead LQFP and 144-ball LFBGA packages.

#### 4.2.1 144-lead LQFP Package Outline

Figure 4-3. Orientation of the 144-lead LQFP Package

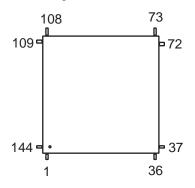

#### 4.2.2 144-ball LFBGA Package Outline

The 144-Ball LFBGA package has a 0.8 mm ball pitch and respects Green Standards. Its dimensions are 10 x 10 x 1.4 mm.

#### 4.2.3 144-lead LQFP Pinout

Table 4-3.144-lead LQFP SAM3X4/8E Pinout

| 1  | PB26    | 37 | DHSDP   | 73  | VDDANA  | 109 | PA26    |

|----|---------|----|---------|-----|---------|-----|---------|

| 2  | PA9     | 38 | DHSDM   | 74  | GNDANA  | 110 | PA27    |

| 3  | PA10    | 39 | VBUS    | 75  | ADVREF  | 111 | PA28    |

| 4  | PA11    | 40 | VBG     | 76  | PB15    | 112 | PA29    |

| 5  | PA12    | 41 | VDDUTMI | 77  | PB16    | 113 | PB0     |

| 6  | PA13    | 42 | DFSDP   | 78  | PA16    | 114 | PB1     |

| 7  | PA14    | 43 | DFSDM   | 79  | PA24    | 115 | PB2     |

| 8  | PA15    | 44 | GNDUTMI | 80  | PA23    | 116 | PC4     |

| 9  | PA17    | 45 | VDDCORE | 81  | PA22    | 117 | PC10    |

| 10 | VDDCORE | 46 | JTAGSEL | 82  | PA6     | 118 | PB3     |

| 11 | VDDIO   | 47 | NRSTB   | 83  | PA4     | 119 | PB4     |

| 12 | GND     | 48 | XIN32   | 84  | PA3     | 120 | PB5     |

| 13 | PD0     | 49 | XOUT32  | 85  | PA2     | 121 | PB6     |

| 14 | PD1     | 50 | SHDN    | 86  | PB12    | 122 | PB7     |

| 15 | PD2     | 51 | TST     | 87  | PB13    | 123 | PB8     |

| 16 | PD3     | 52 | VDDBU   | 88  | PB17    | 124 | VDDCORE |

| 17 | PD4     | 53 | FWUP    | 89  | PB18    | 125 | VDDIO   |

| 18 | PD5     | 54 | GNDBU   | 90  | PB19    | 126 | GND     |

| 19 | PD6     | 55 | PC1     | 91  | PB20    | 127 | PB9     |

| 20 | PD7     | 56 | VDDOUT  | 92  | PB21    | 128 | PB10    |

| 21 | PD8     | 57 | VDDIN   | 93  | PC11    | 129 | PB11    |

| 22 | PD9     | 58 | GND     | 94  | PC12    | 130 | PC0     |

| 23 | PA0     | 59 | PC2     | 95  | PC13    | 131 | PC20    |

| 24 | PA1     | 60 | PC3     | 96  | PC14    | 132 | PC21    |

| 25 | PA5     | 61 | VDDCORE | 97  | PC15    | 133 | PC22    |

| 26 | PA7     | 62 | VDDIO   | 98  | PC16    | 134 | PC23    |

| 27 | PA8     | 63 | PC5     | 99  | PC17    | 135 | PC24    |

| 28 | PB28    | 64 | PC6     | 100 | PC18    | 136 | PC25    |

| 29 | PB29    | 65 | PC7     | 101 | PC19    | 137 | PC26    |

| 30 | PB30    | 66 | PC8     | 102 | PC29    | 138 | PC27    |

| 31 | PB31    | 67 | PC9     | 103 | PC30    | 139 | PC28    |

| 32 | PD10    | 68 | PB27    | 104 | VDDCORE | 140 | PB14    |

| 33 | GNDPLL  | 69 | NRST    | 105 | VDDIO   | 141 | PB22    |

| 34 | VDDPLL  | 70 | PA18    | 106 | GND     | 142 | PB23    |

| 35 | XOUT    | 71 | PA19    | 107 | PA21    | 143 | PB24    |

| 36 | XIN     | 72 | PA20    | 108 | PA25    | 144 | PB25    |

#### 4.2.4 144-ball LFBGA Pinout

| A1  | PA9  | D1  | PA17    | G1  | PA5     | K1  | VDDCORE |

|-----|------|-----|---------|-----|---------|-----|---------|

| A2  | PB23 | D2  | PD0     | G2  | PA7     | K2  | GNDUTMI |

| A3  | PB14 | D3  | PA11    | G3  | PA8     | K3  | VDDPLL  |

| A4  | PC26 | D4  | PA15    | G4  | PA1     | K4  | NRSTB   |

| A5  | PC24 | D5  | PA14    | G5  | GND     | K5  | SHDN    |

| A6  | PC20 | D6  | PC27    | G6  | GND     | K6  | PC3     |

| A7  | PB10 | D7  | PC25    | G7  | GND     | K7  | PC6     |

| A8  | PB6  | D8  | VDDIO   | G8  | PC16    | K8  | PC7     |

| A9  | PB4  | D9  | PB5     | G9  | PC15    | K9  | PA18    |

| A10 | PC4  | D10 | PB0     | G10 | PC13    | K10 | PA23    |

| A11 | PA28 | D11 | PC30    | G11 | PB13    | K11 | PA16    |

| A12 | PA27 | D12 | PC19    | G12 | PB18    | K12 | PA24    |

| B1  | PA10 | E1  | PD1     | H1  | XOUT    | L1  | DHSDP   |

| B2  | PB26 | E2  | PD2     | H2  | PB30    | L2  | DHSDM   |

| B3  | PB24 | E3  | PD3     | H3  | PB28    | L3  | VDDUTMI |

| B4  | PC28 | E4  | PD4     | H4  | PB29    | L4  | JTAGSEL |

| B5  | PC23 | E5  | PD5     | H5  | VDDBU   | L5  | GNDBU   |

| B6  | PC0  | E6  | VDDCORE | H6  | VDDCORE | L6  | PC1     |

| B7  | PB9  | E7  | VDDCORE | H7  | VDDIO   | L7  | PC2     |

| B8  | PB8  | E8  | VDDCORE | H8  | PC12    | L8  | PC5     |

| B9  | PB3  | E9  | PB1     | H9  | PC11    | L9  | PC9     |

| B10 | PB2  | E10 | PC18    | H10 | PA3     | L10 | PA20    |

| B11 | PA26 | E11 | PB19    | H11 | PB12    | L11 | VDDANA  |

| B12 | PA25 | E12 | PB21    | H12 | PA2     | L12 | PB16    |

| C1  | PA13 | F1  | PD8     | J1  | XIN     | M1  | DFSDP   |

| C2  | PA12 | F2  | PD6     | J2  | GNDPLL  | M2  | DFSDM   |

| C3  | PB25 | F3  | PD9     | J3  | PD10    | M3  | VBG     |

| C4  | PB22 | F4  | PA0     | J4  | PB31    | M4  | VBUS    |

| C5  | PC22 | F5  | PD7     | J5  | TST     | M5  | XIN32   |

| C6  | PC21 | F6  | GND     | J6  | FWUP    | M6  | XOUT32  |

| C7  | PB11 | F7  | GND     | J7  | PB27    | M7  | VDDOUT  |

| C8  | PB7  | F8  | VDDIO   | J8  | NRST    | M8  | VDDIN   |

| C9  | PC10 | F9  | PC17    | J9  | PA19    | M9  | PC8     |

| C10 | PA29 | F10 | PC14    | J10 | PA22    | M10 | GNDANA  |

| C11 | PA21 | F11 | PB20    | J11 | PA4     | M11 | ADVREF  |

| C12 | PC29 | F12 | PB17    | J12 | PA6     | M12 | PB15    |

#### Table 4-4.144-ball LFBGA SAM3X4/8E Pinout

20 SAM3X/A

## 5. Power Considerations

## 5.1 Power Supplies

The SAM3X/A series product has several types of power supply pins:

- VDDCORE pins: Power the core, the embedded memories and the peripherals; voltage ranges from 1.62V to 1.95V.

- VDDIO pins: Power the Peripherals I/O lines; voltage ranges from 1.62V to 3.6V.

- VDDIN pin: Powers the Voltage regulator

- VDDOUT pin: It is the output of the voltage regulator.

- VDDBU pin: Powers the Slow Clock oscillator and a part of the System Controller; voltage ranges from 1.62V to 3.6V. VDDBU must be supplied before or at the same time than VDDIO and VDDCORE.

- VDDPLL pin: Powers the PLL A, UPLL and 3-20 MHz Oscillator; voltage ranges from 1.62V to 1.95V.

- VDDUTMI pin: Powers the UTMI+ interface; voltage ranges from 3.0V to 3.6V, 3.3V nominal.

- VDDANA pin: Powers the ADC and DAC cells; voltage ranges from 2.0V to 3.6V.

Ground pins GND are common to VDDCORE and VDDIO pins power supplies.

Separated ground pins are provided for VDDBU, VDDPLL, VDDUTMI and VDDANA. These ground pins are respectively GNDBU, GNDPLL, GNDUTMI and GNDANA.

### 5.2 Voltage Regulator

The SAM3X/A series embeds a voltage regulator that is managed by the Supply Controller.

This internal regulator is intended to supply the internal core of SAM3X/A series but can be used to supply other parts in the application. It features two different operating modes:

- In Normal mode, the voltage regulator consumes less than 700  $\mu$ A static current and draws 150 mA of output current. Internal adaptive biasing adjusts the regulator quiescent current depending on the required load current. In Wait Mode or when the output current is low, quiescent current is only 7 $\mu$ A.

- In Shutdown mode, the voltage regulator consumes less than 1  $\mu$ A while its output is driven internally to GND. The default output voltage is 1.80V and the start-up time to reach Normal mode is inferior to 400  $\mu$ s.

For adequate input and output power supply decoupling/bypassing, refer to "Voltage Regulator" in the "Electrical Characteristics" section of the product datasheet.

## 5.3 Typical Powering Schematics

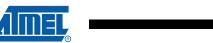

The SAM3X/A series supports a 1.62V-3.6V single supply mode. The internal regulator input connected to the source and its output feeds VDDCORE. Figure 5-1 shows the power schematics.

Figure 5-1. Single Supply

Note: Restrictions For USB, VDDUTMI needs to be greater than 3.0V. For ADC, VDDANA needs to be greater than 2.0V. For DAC, VDDANA needs to be greater than 2.4V.

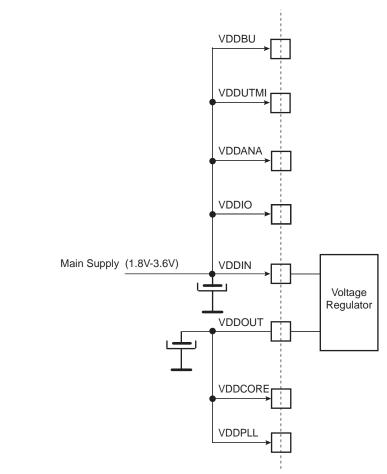

Figure 5-2. Core Externally Supplied

Note: Restrictions

For USB, VDDUTMI needs to be greater than 3.0V. For ADC, VDDANA needs to be greater than 2.0V. For DAC, VDDANA needs to be greater than 2.4V.

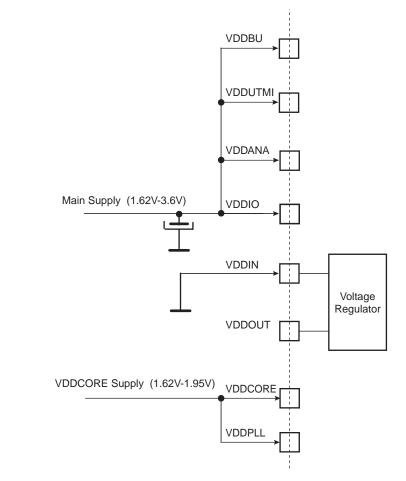

#### Note: Backup Batteries Used

#### Note: 1. Restrictions

- For USB, VDDUTMI needs to be greater than 3.0V. For ADC, VDDANA needs to be greater than 2.0V. For DAC, VDDANA needs to be greater than 2.4V.

- 2. VDDUTMI and VDDANA cannot be left unpowered.

#### 5.4 Active Mode

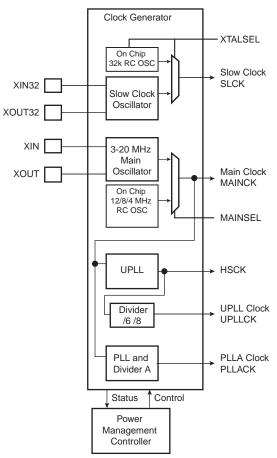

Active mode is the normal running mode with the core clock running from the fast RC oscillator, the main crystal oscillator or the PLLA. The power management controller can be used to adapt the frequency and to disable the peripheral clocks.

#### 5.5 Low Power Modes

The various low power modes of the SAM3X/A series are described below:

#### 5.5.1 Backup Mode

The purpose of backup mode is to achieve the lowest power consumption possible in a system which is performing periodic wake-ups to perform tasks but not requiring fast startup time (< 0.5ms).

The Supply Controller, zero-power power-on reset, RTT, RTC, Backup registers and 32 kHz Oscillator (RC or crystal oscillator selected by software in the Supply Controller) are running. The regulator and the core supply are off.

Backup Mode is based on the Cortex-M3 deep-sleep mode with the voltage regulator disabled.

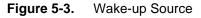

The SAM3X/A series can be awakened from this mode through the Force Wake-up pin (FWUP), and Wake-up input pins WKUP0 to WKUP15, Supply Monitor, RTT or RTC wake-up event. Current Consumption is  $2.5 \ \mu$ A typical on VDDBU.

Backup mode is entered by using WFE instructions with the SLEEPDEEP bit in the System Control Register of the Cortex-M3 set to 1. (See the Power management description in the "ARM Cortex M3 Processor" section of the product datasheet).

Exit from Backup mode happens if one of the following enable wake up events occurs:

- FWUP pin (low level, configurable debouncing)

- WKUPEN0-15 pins (level transition, configurable debouncing)

- SM alarm

- RTC alarm

- RTT alarm

#### 5.5.2 Wait Mode

The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a powered state for a startup time of less than 10  $\mu$ s.

In this mode, the clocks of the core, peripherals and memories are stopped. However, the core, peripherals and memories power supplies are still powered. From this mode, a fast start up is available.

This mode is entered via Wait for Event (WFE) instructions with LPM = 1 (Low Power Mode bit in PMC\_FSMR). The Cortex-M3 is able to handle external events or internal events in order to wake-up the core (WFE). This is done by configuring the external lines WKUP0-15 as fast startup wake-up pins (refer to Section 5.7 "Fast Start-Up"). RTC or RTT Alarm and USB wake-up events can be used to wake up the CPU (exit from WFE).

Current Consumption in Wait mode is typically 23  $\mu$ A for total current consumption if the internal voltage regulator is used or 15  $\mu$ A if an external regulator is used.

Entering Wait Mode:

- Select the 4/8/12 MHz Fast RC Oscillator as Main Clock

- Set the LPM bit in the PMC Fast Startup Mode Register (PMC\_FSMR)

- Execute the Wait-For-Event (WFE) instruction of the processor

- Note: Internal Main clock resynchronization cycles are necessary between the writing of MOSCRCEN bit and the effective entry in Wait mode. Depending on the user application, Waiting for MOSCRCEN bit to be cleared is recommended to ensure that the core will not execute undesired instructions.

#### 5.5.3 Sleep Mode

The purpose of sleep mode is to optimize power consumption of the device versus response time. In this mode, only the core clock is stopped. The peripheral clocks can be enabled. This mode is entered via Wait for Interrupt (WFI) or Wait for Event (WFE) instructions with LPM = 0 in PMC\_FSMR.

The processor can be awakened from an interrupt if WFI instruction of the Cortex M3 is used, or from an event if the WFE instruction is used to enter this mode.

#### 5.5.4 Low Power Mode Summary Table

The modes detailed above are the main low power modes. Each part can be set to on or off separately and wake-up sources can be individually configured. Table 5-1 below shows a summary of the configurations of the low power modes.

| Mode           | VDDBU<br>Region <sup>(1)</sup> | Regulator      | Core<br>Memory<br>Peripherals              | Mode Entry                                          | Potential Wake-up<br>Sources                                                                                                                                                                 | Core at<br>Wake-up | PIO State<br>while in Low<br>Power Mode | PIO State<br>at Wake-up                                                           | Consumption<br>(2) (3)         | Wake-up<br>Time <sup>(4)</sup> |

|----------------|--------------------------------|----------------|--------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|--------------------------------|

| Backup<br>Mode | ON                             | OFF<br>SHDN =0 | OFF<br>(Not<br>powered)                    | WFE<br>+SLEEPDEEP<br>bit = 1                        | FWUP pin<br>WKUP0-15 pins<br>BOD alarm<br>RTC alarm<br>RTT alarm                                                                                                                             | Reset              |                                         | PIOA &<br>PIOB &<br>PIOC &<br>PIOD &<br>PIOE &<br>PIOF<br>Inputs with<br>pull-ups | 2.5 μΑ typ <sup>(5)</sup>      | < 0.5 ms                       |

| Wait<br>Mode   | ON                             | ON<br>SHDN =1  | Powered<br>(Not<br>clocked)                | WFE<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 1        | Any Event from: Fast<br>startup through<br>WKUP0-15 pins<br>RTC alarm<br>RTT alarm<br>USB wake-up                                                                                            | Clocked<br>back    | Previous<br>state saved                 | Unchanged                                                                         | 18.4 µА/26.6 µА <sup>(6)</sup> | < 10 µs                        |

| Sleep<br>Mode  | ON                             | ON<br>SHDN =1  | Powered <sup>(7)</sup><br>(Not<br>clocked) | WFE or WFI<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 0 | Entry mode = WFI<br>Interrupt Only;<br>Entry mode = WFE<br>Any Enabled Interrupt<br>and/or Any Event from<br>Fast start-up through<br>WKUP0-15 pins<br>RTC alarm<br>RTT alarm<br>USB wake-up |                    | Previous<br>state saved                 | Unchanged                                                                         | (7)                            | (7)                            |

Table 5-1.

Low Power Mode Configuration Summary

Notes: 1. SUPC, 32 kHz Oscillator, RTC, RTT, Backup Registers, POR

2. The external loads on PIOs are not taken into account in the calculation.

- 3. BOD current consumption is not included.

- 4. When considering the wake-up time, the time required to start the PLL is not taken into account. Once started, the device works with the 4/8/12 MHz Fast RC oscillator. The user has to add the PLL start-up time if it is needed in the system. The wake-up time is defined as the time taken for wake-up until the first instruction is fetched

- 5. Current consumption on VDDBU.

- 6. 18.4 µA on VDDCORE, 26.6 µA for total current consumption (using internal voltage regulator).

- 7. Depends on MCK frequency. In this mode, the core is supplied and not clocked but some peripherals can be clocked.

SAM3X/A

## 5.6 Wake-up Sources

The wake-up events allow the device to exit the backup mode. When a wake-up event is detected, the Supply Controller performs a sequence which automatically reenables the core power supply.

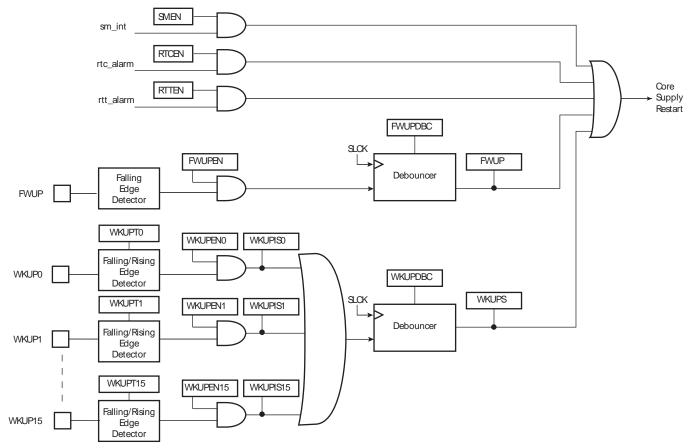

## 5.7 Fast Start-Up

The SAM3X/A series allows the processor to restart in a few microseconds while the processor is in wait mode. A fast start up can occur upon detection of a low level on one of the 19 wake-up inputs.

The fast restart circuitry, as shown in Figure 5-4, is fully asynchronous and provides a fast startup signal to the Power Management Controller. As soon as the fast start-up signal is asserted, the PMC automatically restarts the embedded 4/8/12 MHz fast RC oscillator, switches the master clock on this 4/8/12 MHz clock and reenables the processor clock.

#### Figure 5-4. Fast Start-Up Sources

## 6. Input/Output Lines

The SAM3X/A has different kinds of input/output (I/O) lines, such as general purpose I/Os (GPIO) and system I/Os. GPIOs can have alternate functions thanks to multiplexing capabilities of the PIO controllers. The same PIO line can be used whether in IO mode or by the multiplexed peripheral. System I/Os include pins such as test pins, oscillators, erase or analog inputs.

With a few exceptions, the I/Os have input schmitt triggers. Refer to the footnotes associated with PIOA to PIOF on page 14, at the end of Table 3-1, "Signal Description List".

## 6.1 General Purpose I/O Lines (GPIO)

GPIO Lines are managed by PIO Controllers. All I/Os have several input or output modes such as pull-up, input schmitt triggers, multi-drive (open-drain), glitch filters, debouncing or input change interrupt. Programming of these modes is performed independently for each I/O line through the PIO controller user interface. For more details, refer to the "PIO Controller" section of the product datasheet.

The input output buffers of the PIO lines are supplied through VDDIO power supply rail.

The SAM3X/A embeds high speed pads able to handle up to 65 MHz for HSMCI and SPI clock lines and 45 MHz on other lines. See product AC Characteristics for more details. Typical pull-up value is 100 k $\Omega$  for all I/Os.

Each I/O line also embeds an ODT (On-Die Termination), (see Figure 6-1 below). ODT consists of an internal series resistor termination scheme for impedance matching between the driver output (SAM3) and the PCB track impedance preventing signal reflection. The series resistor helps to reduce IOs switching current (di/dt) thereby reducing in turn, EMI. It also decreases overshoot and undershoot (ringing) due to inductance of interconnect between devices or between boards. In conclusion, ODT helps reducing signal integrity issues.

## 6.2 System I/O Lines

System I/O lines are pins used by oscillators, test mode, reset, flash erase and JTAG to name but a few. Described below are the SAM3X/A system I/O lines shared with PIO lines.

These pins are software configurable as general purpose I/O or system pins. At startup, the default function of these pins is always used.

| SYSTEM_IO<br>Bit Number | Peripheral | Default Function<br>After Reset | Other Function | Constraints for<br>Normal Start       | Configuration                                                                                                                                   |  |

|-------------------------|------------|---------------------------------|----------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 12                      | -          | ERASE                           | PC0            | Low Level at<br>startup <sup>()</sup> | In Matrix User Interface Registers<br>(Refer to "System IO Configuration<br>Register" in the "Bus Matrix" section<br>of the product datasheet.) |  |

|                         | А          | TCK/SWCLK                       | PB28           | -                                     |                                                                                                                                                 |  |

|                         | А          | TDI                             | PB29           | -                                     | In PIO Controller                                                                                                                               |  |

|                         | А          | TDO/TRACESWO                    | PB30           | -                                     | in PIO Controller                                                                                                                               |  |

|                         | А          | TMS/SWDIO                       | PB31           | -                                     |                                                                                                                                                 |  |

Table 6-1.

System I/O Configuration Pin List

Note: 1. If PC0 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the user application sets PC0 into PIO mode.

#### 6.2.1 Serial Wire JTAG Debug Port (SWJ-DP) Pins

The SWJ-DP pins are TCK/SWCLK, TMS/SWDIO, TDO/SWO, TDI and commonly provided on a standard 20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table 3-1.

At startup, SWJ-DP pins are configured in SWJ-DP mode to allow connection with debugging probe. Please refer to the "Debug and Test" section of the product datasheet.

SWJ-DP pins can be used as standard I/Os to provide users with more general input/output pins when the debug port is not needed in the end application. Mode selection between SWJ-DP mode (System IO mode) and general IO mode is performed through the AHB Matrix Special Function Registers (MATRIX\_SFR). Configuration of the pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

By default, the JTAG Debug Port is active. If the debugger host wants to switch to the Serial Wire Debug Port, it must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables the JTAG-DP and enables the SW-DP. When the Serial Wire Debug Port is active, TDO/TRACESWO can be used for trace.

The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be used with SW-DP, not JTAG-DP. For more information about SW-DP and JTAG-DP switching, please refer to the "Debug and Test" section of the product datasheet.

All JTAG signals are supplied with VDDIO except JTAGSEL, supplied by VDDBU.

#### 6.3 Test Pin

The TST pin is used for JTAG Boundary Scan Manufacturing Test or Fast Flash programming mode of the SAM3X/A series. The TST pin integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations. To enter fast programming mode, see the "Fast Flash Programming Interface" section. For more information on the manufacturing and test mode, refer to the "Debug and Test" section of the product datasheet.

30 SAM3X/A

## 6.4 NRST Pin

The NRST pin is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components, or asserted low externally to reset the microcontroller. It will reset the Core and the peripherals except the Backup region (RTC, RTT and Supply Controller). There is no constraint on the length of the reset pulse, and the reset controller can guarantee a minimum pulse length.

The NRST pin integrates a permanent pull-up resistor to VDDIO of about 100 k $\Omega$ .

### 6.5 NRSTB Pin

The NRSTB pin is input only and enables asynchronous reset of the SAM3X/A series when asserted low. The NRSTB pin integrates a permanent pull-up resistor of about 15 k $\Omega$  This allows connection of a simple push button on the NRSTB pin as a system-user reset. In all modes, this pin will reset the chip including the Backup region (RTC, RTT and Supply Controller). It reacts as the Power-on reset. It can be used as an external system reset source. In harsh environments, it is recommended to add an external capacitor (10 nF) between NRSTB and VDDBU. (For filtering values, refer to "I/O characteristics" in the "Electrical Characteristics" section of the product datasheet)

It embeds an anti-glitch filter.

#### 6.6 ERASE Pin

The ERASE pin is used to reinitialize the Flash content (and some of its NVM bits) to an erased state (all bits read as logic level 1). It integrates a pull-down resistor of about 100 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

This pin is debounced by SCLK to improve the glitch tolerance. When the ERASE pin is tied high during less than 100 ms, it is not taken into account. The pin must be tied high during more than 220 ms to perform a Flash erase operation.

The ERASE pin is a system I/O pin and can be used as a standard I/O. At startup, the ERASE pin is not configured as a PIO pin. If the ERASE pin is used as a standard I/O, the startup level of this pin must be low to prevent unwanted erasing. Please refer to Section 11.2 "Peripheral Signal Multiplexing on I/O Lines". Also, if the ERASE pin is used as a standard I/O output, asserting the pin to low does not erase the Flash.

## 7. Processor and Architecture

## 7.1 ARM Cortex-M3 Processor

- Version 2.0

- Thumb-2 (ISA) subset consisting of all base Thumb-2 instructions, 16-bit and 32-bit.

- Harvard processor architecture enabling simultaneous instruction fetch with data load/store.

- Three-stage pipeline.

- Single cycle 32-bit multiply.

- Hardware divide.

- Thumb and Debug states.

- Handler and Thread modes.

- Low latency ISR entry and exit.

## 7.2 APB/AHB Bridge

The SAM3X/A series product embeds two separate APB/AHB bridges:

- a low speed bridge

- a high speed bridge

This architecture enables a concurrent access on both bridges.

SPI, SSC and HSMCI peripherals are on the high-speed bridge connected to DMAC with the internal FIFO for Channel buffering.

UART, ADC, TWI0-1, USART0-3, PWM, DAC and CAN peripherals are on the low-speed bridge and have dedicated channels for the Peripheral DMA Channels (PDC). Please not that USART0-1 can be used with the DMA as well.

The peripherals on the high speed bridge are clocked by MCK. On the low-speed bridge, CAN controllers can be clocked at MCK divided by 2 or 4. Refer to the Power Management Controller (PMC) section of the Full datasheet for further details.

## 7.3 Matrix Masters

The Bus Matrix of the SAM3X/A series product manages 5 (SAM3A) or 6 (SAM3X) masters, which means that each master can perform an access, concurrently with others, to an available slave.

Each master has its own decoder, which is defined specifically for each master. In order to simplify the addressing, all masters have the same decodings.

| Master 0 | Cortex-M3 Instruction/Data      |

|----------|---------------------------------|

| Master 1 | Cortex-M3 System                |

| Master 2 | Peripheral DMA Controller (PDC) |

| Master 3 | USB OTG High Speed DMA          |

| Master 4 | DMA Controller                  |

| Master 5 | Ethernet MAC (SAM3X)            |

Table 7-1.

List of Bus Matrix Masters

#### 7.4 **Matrix Slaves**

The Bus Matrix of the SAM3X/A series product manages 9 slaves. Each slave has its own arbiter, allowing a different arbitration per slave.

| Table 7-2. | List of Bus Matrix Slaves |                                    |  |  |

|------------|---------------------------|------------------------------------|--|--|

| Slave 0    |                           | Internal SRAM0                     |  |  |

| Slave 1    |                           | Internal SRAM1                     |  |  |

| Slave 2    |                           | Internal ROM                       |  |  |

| Slave 3    |                           | Internal Flash                     |  |  |

| Slave 4    |                           | USB High Speed Dual Port RAM (DPR) |  |  |

| Slave 5    |                           | NAND Flash Controller RAM          |  |  |

| Slave 6    |                           | External Bus Interface             |  |  |

| Slave 7    |                           | Low Speed Peripheral Bridge        |  |  |

| Slave 8    |                           | High Speed Peripheral Bridge       |  |  |

#### 7.5 **Master to Slave Access**

All the Masters can normally access all the Slaves. However, some paths do not make sense, for example allowing access from the USB High Speed DMA to the Internal Peripherals. Thus, these paths are forbidden or simply not wired, and shown as "-" in the following table.

| Table 7-3. SAM3X/A Series Master to Slave Acce |

|------------------------------------------------|

|------------------------------------------------|

|        | Masters                      | 0                    | 1                  | 2   | 3                     | 4                 | 5           |

|--------|------------------------------|----------------------|--------------------|-----|-----------------------|-------------------|-------------|

| Slaves |                              | Cortex-M3<br>I/D Bus | Cortex-M3 S<br>Bus | PDC | USB High<br>Speed DMA | DMA<br>Controller | EMAC<br>DMA |

| 0      | Internal SRAM0               | -                    | Х                  | Х   | Х                     | Х                 | Х           |

| 1      | Internal SRAM1               | -                    | Х                  | Х   | Х                     | Х                 | Х           |

| 2      | Internal ROM                 | Х                    | -                  | Х   | Х                     | Х                 | Х           |

| 3      | Internal Flash               | Х                    | -                  | -   | -                     | -                 | -           |

| 4      | USB High Speed Dual Port RAM | -                    | Х                  | -   | -                     | Х                 | -           |

| 5      | Nand Flash Controller RAM    | -                    | Х                  | Х   | Х                     | Х                 | Х           |

| 6      | External Bus Interface       | -                    | Х                  | Х   | Х                     | Х                 | Х           |

| 7      | Low Speed Peripheral Bridge  | -                    | Х                  | Х   | -                     | Х                 | -           |

| 8      | High Speed Peripheral Bridge | -                    | Х                  | -   | -                     | Х                 | -           |

## 7.6 DMA Controller

- Acting as one Matrix Master

- Embeds 4 (SAM3A and 100-pin SAM3X) or 6 (144-pin SAM3X) channels

| Table 7-4. | DMA Channels |

|------------|--------------|

|------------|--------------|

| DMA Channel Size                    | SAM3A<br>100-pin SAM3X     | 144-pin SAM3X                 |  |

|-------------------------------------|----------------------------|-------------------------------|--|

| 8 bytes FIFO for Channel Buffering  | 3<br>(Channels 0, 1 and 2) | 4<br>(Channels 0, 1, 2 and 4) |  |

| 32 bytes FIFO for Channel Buffering | 1<br>(Channel 3)           | 2<br>(Channels 3 and 5)       |  |

- Linked List support with Status Write Back operation at End of Transfer

- Word, HalfWord, Byte transfer support.

- Handles high speed transfer of SPI0-1, USART0-1, SSC and HSMCI (peripheral to memory, memory to peripheral)

- Memory to memory transfer

- Can be triggered by PWM and T/C which enables to generates waveform though the External Bus Interface

The DMA controller can handle the transfer between peripherals and memory and so receives the triggers from the peripherals below. The hardware interface numbers are also given in Table 7-5.

| Instance Name | Channel T/R      | DMA Channel HW<br>Interface Number |

|---------------|------------------|------------------------------------|

| HSMCI         | Transmit/Receive | 0                                  |

| SPI0          | Transmit         | 1                                  |

| SPI0          | Receive          | 2                                  |

| SSC           | Transmit         | 3                                  |

| SSC           | Receive          | 4                                  |

| SPI1          | Transmit         | 5                                  |

| SPI1          | Receive          | 6                                  |

| TWIO          | Transmit         | 7                                  |

| TWIO          | Receive          | 8                                  |

| -             | -                | -                                  |

| -             | -                | -                                  |

| USART0        | Transmit         | 11                                 |

| USART0        | Receive          | 12                                 |

| USART1        | Transmit         | 13                                 |

| USART1        | Receive          | 14                                 |

| PWM           | Transmit         | 15                                 |

Table 7-5.DMA Controller

## 7.7 Peripheral DMA Controller

- Handles data transfer between peripherals and memories

- Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- Next Pointer management for reducing interrupt latency requirement

The Peripheral DMA Controller handles transfer requests from the channel according to the following priorities (Low to High priorities):

| Instance Name | Channel T/R | 144 Pins | 100 Pins |

|---------------|-------------|----------|----------|

| DAC           | Transmit    | Х        | Х        |

| PWM           | Transmit    | Х        | х        |

| TWI1          | Transmit    | Х        | х        |

| TWI0          | Transmit    | Х        | Х        |

| USART3        | Transmit    | Х        | Х        |

| USART2        | Transmit    | Х        | Х        |

| USART1        | Transmit    | Х        | Х        |

| USART0        | Transmit    | Х        | Х        |

| UART          | Transmit    | Х        | Х        |

| ADC           | Receive     | Х        | Х        |

| TWI1          | Receive     | Х        | Х        |

| TWI0          | Receive     | Х        | Х        |

| USART3        | Receive     | Х        | N/A      |

| USART2        | Receive     | Х        | Х        |

| USART1        | Receive     | X        | Х        |

| USART0        | Receive     | Х        | Х        |

| UART          | Receive     | Х        | Х        |

Table 7-6.

Peripheral DMA Controller