**HARRIS**

OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

NO RECOMMENDED REPLACEMENT

1-800-442-7747

Call Central Applications

or email: centapp@harris.com

CA3126

May 1999

**TV Chroma Processor**

# **Features**

- Phase Locked Subcarrier Regeneration Utilizes Sample-and-Hold Techniques

- Automatic Chrominance Control (ACC)/Killer Detector Employs Sample-and-Hold Techniques

- Supplementary ACC with an Overload Detector to Prevent Oversaturation of this Picture Tube

- Sinusoidal Subcarrier Output

- · Keyed Chroma Output

- Emitter Follower Buffered Outputs for Low Output Impedance

- Linear DC Saturation Control

# **Applications**

- TV/CATV Receiver Circuits

- NTSC Color Decoder/Processor

- Computer Graphics Subcarrier Regenerator

- Timing Reference for Frame Grabbers

- DSP Clock Timing Reference Source

# Description

The Harris CA3126 is a monolithic silicon integrated circuit designed for TV chroma processing and is ideally suited for NTSC color graphic applications that require subcarrier regeneration of the color burst signal.

# Part Number Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |  |

|-------------|---------------------|------------|-------------|--|

| CA3126E     | -40 to 85           | 16 Ld PDIP | E16.3       |  |

| CA3126M1    | -40 to 85           | 20 Ld SOIC | M20.3       |  |

# Pinouts

CA3126 CA3126 (PDIP) (SOIC) **TOP VIEW TOP VIEW** CHROMA IN 20 CHROMA GAIN CONT. CHROMA IN 1 CHROMA GAIN CONT. AFPC FILTER + 19 CHROMA OUT AFPC FILTER + 2 **CHROMA OUT** NC 18 NC 14 ZENER REF AFPC FILTER - 3 AFPC FILTER -17 ZENER REF RF BYPASS 4 OVERLOAD DET. 13 **RF BYPASS** 16 OVERLOAD DET. GROUND 5 12 V+ GROUND 15 V+ VCO OUT 6 ACC+ VCO OUT 14 ACC + VCO IN 7 ACC-VCO IN 13 ACC -HORIZ. KEY IN CARRIER OUT 8 NC HORIZ. KEY IN NC 10 **CARRIER OUT**

# CA3126

#### **Thermal Information Absolute Maximum Ratings** DC Supply Voltage (V+ to GND) (Note 1).......................13.2V Thermal Resistance (Typical, Note 1) $\theta_{JA}$ (°C/W) DC Current: 100 SOIC Package..... Maximum Junction Temperature (Plastic Packages) . . . . . . 150°C DC Voltage (Horizontal Key In) Maximum Storage Temperature Range ..... -65°C to 150°C Negative Rating .....-5V Maximum Lead Temperature (Soldering 10s).....300°C (SOIC - Lead Tips Only)

# **Operating Conditions**

Temperature Range . . . . . . . . . -40°C to 85°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. This rating does not apply when using the internal zener reference in conjunction with an external pass transistor.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

# **Electrical Specifications**

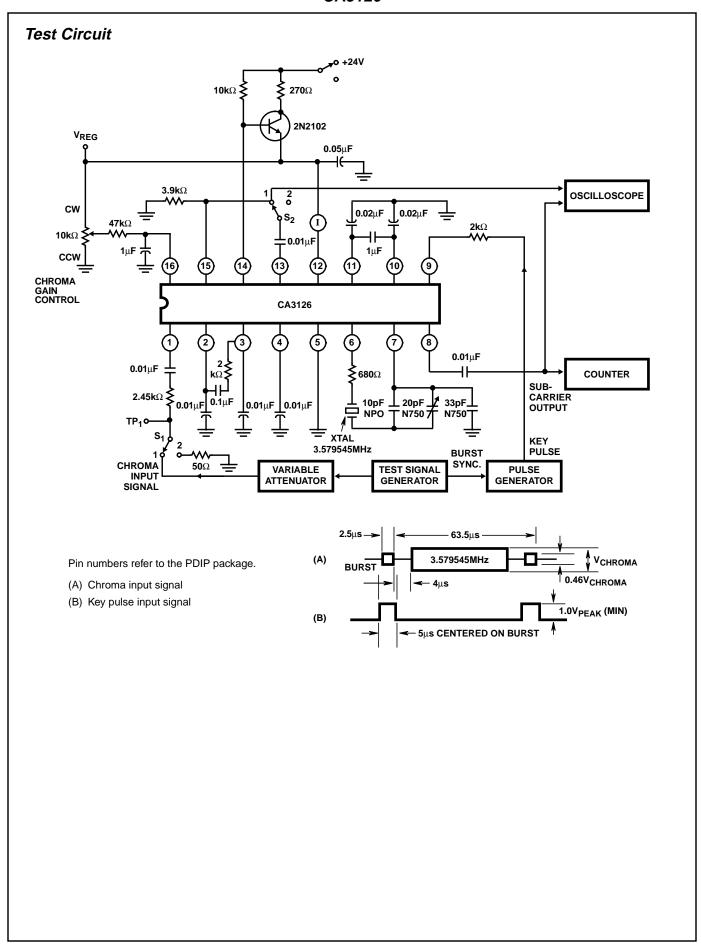

$T_A = 25^{\circ}$ C, Chroma Gain Control at maximum position for all tests except as noted. Electrical specifications referenced to test circuit.

| PARAMETER                                    | TERMINAL,<br>MEASUREMENT<br>AND SYMBOL | SWITCH POS.    |                |                                           |      |      |      |                   |  |  |

|----------------------------------------------|----------------------------------------|----------------|----------------|-------------------------------------------|------|------|------|-------------------|--|--|

|                                              |                                        | S <sub>1</sub> | S <sub>2</sub> | V <sub>CHROMA</sub> INPUT TP <sub>1</sub> | MIN  | TYP  | MAX  | UNITS             |  |  |

| DC ELECTRICAL SPECIFICATIONS                 |                                        |                |                |                                           |      |      |      |                   |  |  |

| Voltage Regulator                            | V <sub>12</sub>                        | 2              | 2              | 0                                         | 10.1 | 11.2 | 12.1 | V                 |  |  |

| Supply Current                               | I <sub>12</sub>                        | 2              | 2              | 0                                         | 16   | 25   | 38   | mA                |  |  |

| SWITCHING ELECTRICAL SPECIFICATIONS (Note 3) |                                        |                |                |                                           |      |      |      |                   |  |  |

| Pull-In Range (Note 4)                       | V <sub>8</sub>                         | (Note 6)       | 2              | 0.5V <sub>P-P</sub>                       | ±250 | -    | -    | Hz                |  |  |

| Oscillator Output                            | V <sub>8</sub>                         | 2              | 2              | 0                                         | 0.6  | 1.0  | -    | V <sub>P-P</sub>  |  |  |

| 100% Chroma Output                           | V <sub>15</sub>                        | 1              | 2              | 0.5V <sub>P-P</sub>                       | 1.4  | 2.7  | -    | V <sub>P-P</sub>  |  |  |

| Overload Detector                            | V <sub>15</sub>                        | 1              | 1              | 0.5V <sub>P-P</sub>                       | 0.4  | -    | 0.7  | V <sub>P-P</sub>  |  |  |

| Minimum Chroma Output<br>(Note 5)            | V <sub>15</sub>                        | 1              | 2              | 0.5V <sub>P-P</sub>                       | -    | -    | 20   | mV <sub>P-P</sub> |  |  |

| 200% Chroma Output                           | V <sub>15</sub>                        | 1              | 2              | 1V <sub>P-P</sub>                         | 70   | 100  | 140  | % of              |  |  |

| 20% Chroma Output                            | V <sub>15</sub>                        | 1              | 2              | 0.1V <sub>P-P</sub>                       | 40   | -    | 105  | 100%<br>Reading   |  |  |

| Kill Level                                   | V <sub>TP1</sub>                       | 1              | 2              | Vary                                      | 5    | -    | 60   | mV <sub>P-P</sub> |  |  |

#### NOTES:

- 3. Except for pull-in range testing, tune oscillator trimmer capacitor for free running frequency of 3.579545MHz ±10Hz.

- $4. \ \ Set \ Switch \ 1 \ to \ Position \ 2, \ detune \ oscillator \ \pm 250 Hz, \ set \ Switch \ 1 \ to \ Position \ 1, \ and \ check \ for \ oscillator \ pull-in.$

- 5. Set Chroma Gain Control to minimum position (CCW).

# NOTES:

- 6. Optional design features.

- 7. Pinout numbers refer to the PDIP package.

# **Application Information**

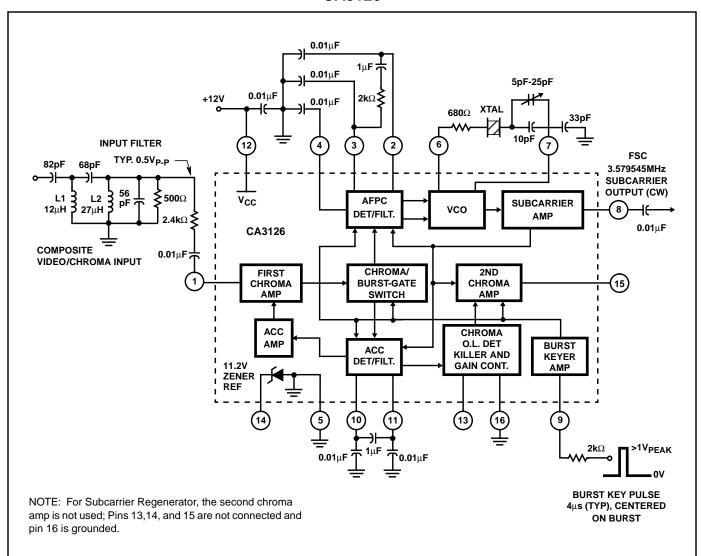

Circuit Description (Pin numbers refer to the DIP package.)

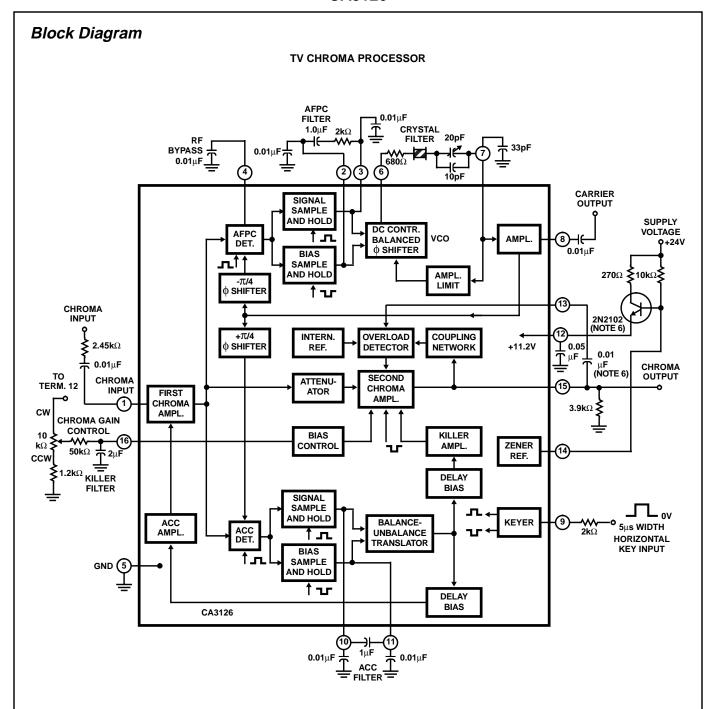

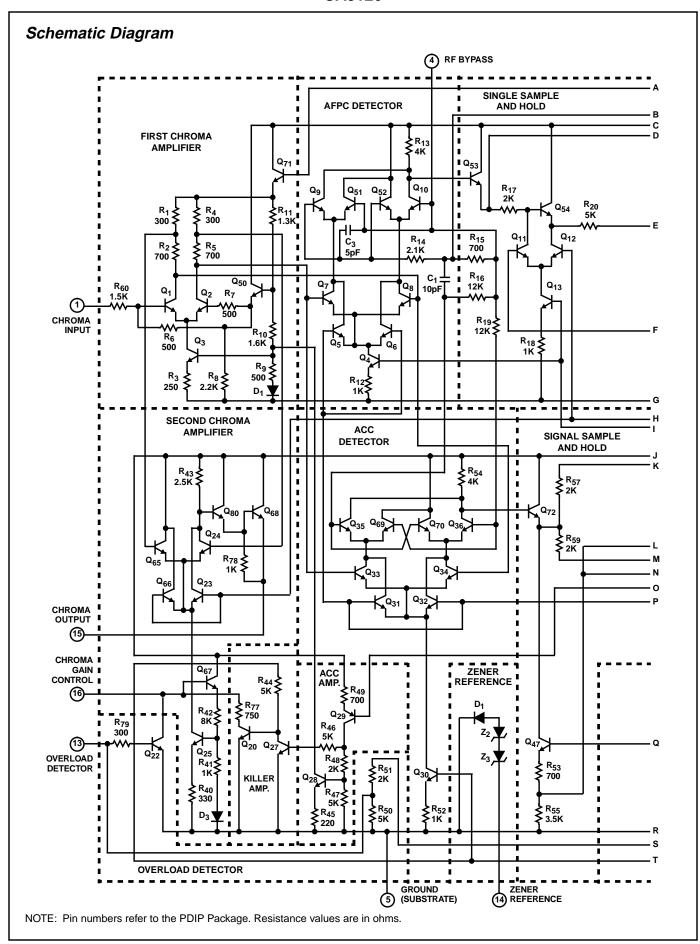

The following paragraphs briefly describe the circuit operation of the CA3126 (shown in the Block Diagram and Schematic Diagram). A detailed description of the operation of various portions of the CA3126 is given in AN6247, "Application of the CA3126 Chroma-Processing IC Using Sample-and-Hold Techniques".

The chroma input is applied to Terminal 1 through the desired band-shaping network. A  $2,450\Omega$  resistor should be placed in series with Terminal 1 to minimize oscillator pickup in the first chroma amplifier. This amplifier supplies signals to the second chroma amplifier and to the ACC and AFPC detectors. The first chroma amplifier is gain-controlled by the ACC amplifier.

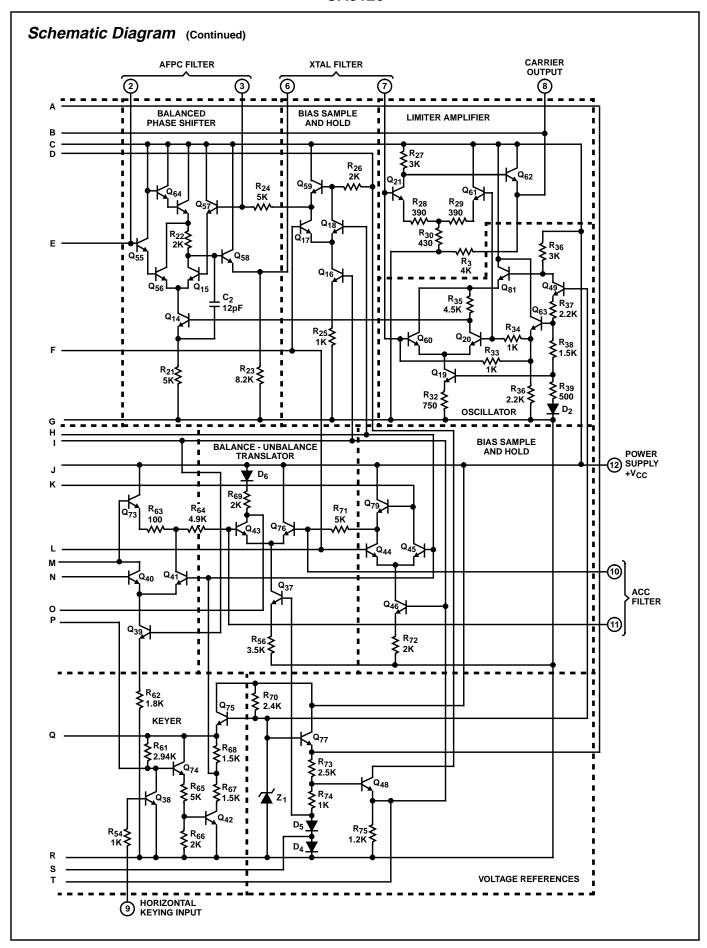

A horizontal keying pulse is applied to Terminal 9. This pulse must be present to ensure proper operation of the oscillator circuit. The subcarrier burst is sampled during the keying interval in the AFPC detector. The error voltage, produced at Terminal 2 and proportional to the burst phase, is compared to the quiescent bias voltage at Terminal 3 by the sample-and-hold circuitry. This "compared" voltage controls the phase-shifting network in the phase-locked loop. The operation of the AFPC loop is independent of any external adjustments or voltages except for an initial capacitor adjustment to set the free-running frequency.

The regenerated oscillator signal at Terminal 8 is applied internally to the AFPC and ACC detectors through +45 and -45-degree phase-shifter networks to establish the proper phase relationship for these detectors. The ACC detector, which also samples the burst during the keying interval, produces a correction voltage proportional to the burst amplitude. The correction voltage is compared to the quiescent bias level using sample-and-hold circuitry similar to that used in the AFPC portion of the circuit. The "compared" voltage is applied internally to the ACC amplifier and killer amplifier. Because the amplifier gains and killer threshold are determined by the ratios of the internal resistors, these functions are independent of external voltages or controls.

The attenuated chroma signal is fed to the second chroma amplifier, where the burst is removed by keyer action. The killer amplifier, the chroma gain control, and the overload detector control the action of the second chroma amplifier, whose gain is proportional to the dc voltage at Terminal 16. The overload detector (Terminal 13) receives a sample of the chroma output (Terminal 15) and detects the peak of the signal. The detected voltage is stored in an external capacitor connected to Terminal 16. This stored voltage on Terminal 16 affects the gain of the second chroma in the same manner as the chroma gain control.

# **General Considerations**

The block diagram shown is typical of the type of circuit used in the practical application of the CA3126. Several items are critical for proper operation of the circuit.

1. A series resistor of approximately  $2,450\Omega$  (or high source impedance) must be used at the chroma input, Terminal 1. This high impedance minimizes pickup of unbalanced currents, particularly of the subcarrier oscillator signal.

- 2. When the overload detector is used, a large resistor (nominally  $47,000\Omega$ ) must be placed in series with Terminal 16 to set the required RC time constant. The same RC network series serves to set the killer time constant.

- 3. The setting of the free-running oscillator frequency requires the presence of the keying pulse. The free-running frequency will be erroneous if Terminal 1 is DC shorted during the setting operation because of the DC offset voltage introduced to the AFPC detector.

- Care must be taken in PC board designs to provide reasonable isolation between the oscillator portion of the circuit (Terminals 6, 7, and 8) and the chroma input (Terminal 1).

#### **Overload Detector**

The overload detector accomplishes two purposes:

- 1. It prevents oversaturation due to low burst-to-chroma ratios.

- 2. It prevents overload conditions due to noise.

Both of these conditions are discussed in more detail in AN6247. The extent to which the overload detector is used depends upon the individual receiver design goals. If greater than  $0.5V_{P-P}$  output is desired, the chroma output at Terminal 15 can be tapped to yield any desired degree of overload detector action.

## **Chroma Gain Control**

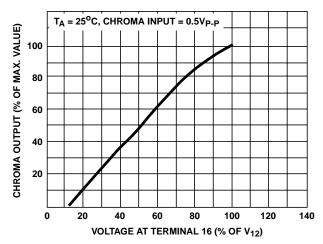

The chroma gain control operates by varying the base bias on current source transistor  $Q_{25}$ . To ensure proper temperature tracking of the chroma gain control, it is essential that the control be operated from a supply source derived from the reference voltage at Terminal 12. Because the control operates from a current source, chroma gain is much more predictable and far less temperature sensitive than controls that steer current by means of a differential amplifier. The typical chroma gain characteristic for the CA3126 is shown in Figure 1.

FIGURE 1. CHROMA GAIN CONTROL

#### **Subcarrier Regenerator Oscillator**

The oscillator filter consists of a 3.579545MHz crystal, a  $680\Omega$  resistor, and a 10pF capacitor connected in series across Terminals 6 and 7. A 33pF capacitor, shunt connected from Terminal 7 to ground, rolls off higher order harmonics, thereby preventing oscillation at the crystal third-harmonic frequency. A

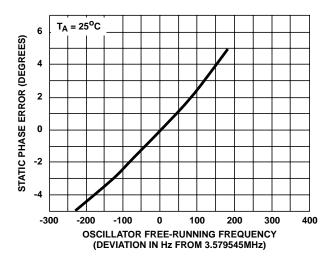

curve of the typical static phase error as a function of the freerunning oscillator frequency is shown in Figure 2. It should be noted that the slope of the curve determines the DC gain of the phase-locked loop, i.e., 40Hz per degree.

FIGURE 2. STATIC PHASE ERROR

## **Thermal Considerations**

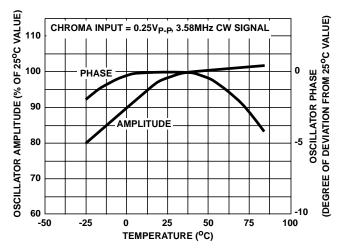

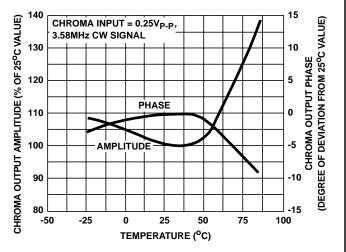

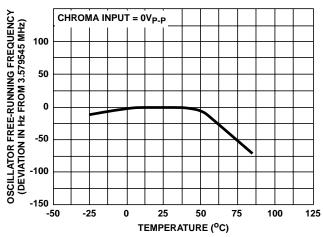

The circuit of the CA3126 is thermally compensated to achieve the optimal operating characteristics over the normal operating temperature range of TV receivers. Figures 3 and 4 show the oscillator and chroma-output amplitudes and phases as a function of temperature (Terminals 8 and 15), respectively.

Both the oscillator and chroma-output amplitudes and phases are measured relative to the chroma-input phase. The performance of the oscillator free-running frequency as a function of temperature is shown in Figure 5. All the temperature plots are characteristic of the test circuit with the indicated component types and values given.

FIGURE 3. AMPLITUDE AND PHASE VARIATIONS OF OSCILLATOR OUTPUT vs TEMPERATURE

FIGURE 4. AMPLITUDE AND PHASE VARIATIONS OF CHROMA OUTPUT vs TEMPERATURE

FIGURE 5. VARIATION OF OSCILLATOR FREE RUNNING FREQUENCY vs TEMPERATURE

FIGURE 6. TYPICAL APPLICATION OF THE CA3126 AS A SUBCARRIER REGENERATOR