# **CAT102**

# Precision, Adjustable Shunt Regulator (600mV Reference)

- ±1% Initial Accuracy - SOT23 Package

### **FEATURES**

- Low voltage reference: 600mV

- Low temperature coefficient reference: 25ppm

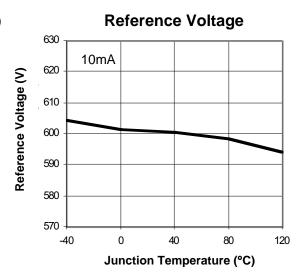

- Accurate 600mV reference voltage: ±6mV at T,=25°C

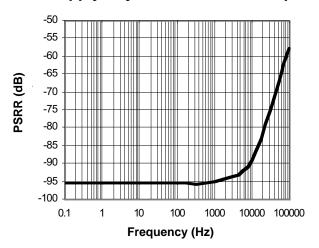

- High PSRR: 45dB at 300kHz

- High line rejection: ±1mV (V<sub>cc</sub> from 2.2V to 18V)

- Low supply current: 300µA

- Open collector output

- Directly drives optocouplers

- Compact 5-lead SOT23 package

- Industrial temperature range: -40°C to 85°C

#### **APPLICATIONS**

- SMPS control loop

- Low temperature coefficient voltage reference

- Power management

- Replaces zener diodes

- Isolated DC-to-DC converters

- Network, telecom and cellular base station power supplies

- Adjustable voltage reference

#### DESCRIPTION

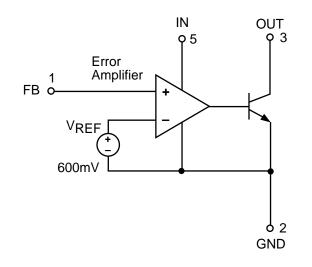

The CAT102 is a low-voltage reference and amplifier. Designed for the control loop of low-voltage power supplies, the reference voltage has been designed for 600mV. Over a junction temperature from -40°C to 105°C the reference voltage is within 8mV of the nominal 600mV. In addition, the error amplifier output and the supply voltage pin are on separate pins.

Power supply rejection is a high 45dB at 300kHz. The output, OUT, can sink 20mA at a maximum saturation voltage of 250mV.

When combined with an optocoupler, the CAT102 can be used as an error amplifier that controls the feedback loop in isolated low-output voltage switching power supplies.

### **FUNCTIONAL DIAGRAM**

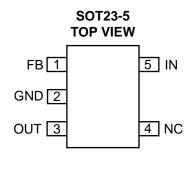

### **PIN CONFIGURATION**

# **PIN DESCRIPTIONS**

| Pin Number | Pin Name | Function                                                             |

|------------|----------|----------------------------------------------------------------------|

| 1          | FB       | Inverting input to error amplifier                                   |

| 2          | GND      | Ground                                                               |

| 3          | OUT      | Output of error amplifier. Source & sink current capability is 20mA. |

| 4          | NC       | No connection                                                        |

| 5          | IN       | Positive supply                                                      |

# **ORDERING INFORMATION**

| Part Number   | Package      | Temperature Range |  |  |

|---------------|--------------|-------------------|--|--|

| CAT102EUK-TE7 | 5-Pin SOT-23 | -40° C to 85° C   |  |  |

TE7 = 7" Reel, 3,000 parts per reel.

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>IN</sub> Voltage              | 20V           |

|--------------------------------------|---------------|

| OUT Voltage                          | 20V           |

| FB Voltage                           | 20V           |

| V <sub>IN</sub> , OUT, FB Current    | 50mA          |

| Operating Junction Temperature       | 150°C         |

| Lead Soldering Temperature (10 sec). | 260°C         |

| Storage Temperature Range6           | 5°C to +150°C |

These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolongued time periods may affect device reliability. All voltages are with respect to ground.

# **ELECTRICAL CHARACTERISTICS**

Electrical characteristics are guaranteed over the full operating temperature range of -40°C to +85°C with a junction temperature from -40°C to +105°C unless otherwise specified. Ambient temperature must be de-rated based upon power dissipation and package thermal characteristics. Unless otherwise stated, test conditions are  $V_{IN}=3V$ , FB=OUT,  $I_{OUT}=1mA$ .

| Symbol                | Parameter                         | Conditions                               | Min  | Тур | Max | Units |

|-----------------------|-----------------------------------|------------------------------------------|------|-----|-----|-------|

| V <sub>IN</sub>       | Supply Voltage Range              |                                          | 2.2  |     | 18  | V     |

| I <sub>IN</sub>       | Quiescent Supply Current          | V <sub>OUT</sub> =1V                     |      | 0.3 | 0.5 | mA    |

| V <sub>FB</sub>       | FB Threshold<br>Reference Voltage | T <sub>J</sub> = 25° C                   | 594  | 600 | 606 | mV    |

|                       |                                   | -40° C <t<sub>J&lt;105° C</t<sub>        | 588  |     | 612 |       |

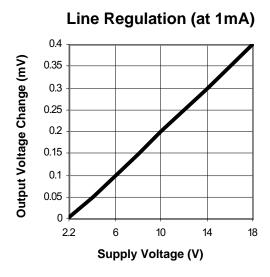

|                       | Line Regulation                   | $V_{IN} = 2.2V \text{ to } V_{IN} = 18V$ |      | 0.5 | 1   | mV    |

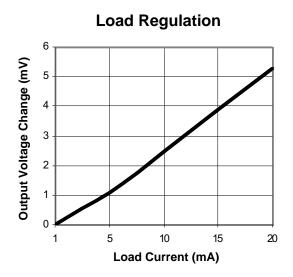

|                       | Load Regulation                   | I <sub>OUT</sub> = 1mA to 10mA           |      | 4   | 8   | mV    |

| I <sub>FB</sub>       | FB Input Current                  |                                          | -500 |     | 500 | nA    |

| PSRR                  | Reference Power Supply Rejection  | Frequency = 300kHz                       | 35   | 45  |     | dB    |

| $A_{V}$               | Error Amplifier Open Loop Gain    | $I_{OUT} = 2mA, V_{OUT} = 1V$            | 60   | 80  |     | dB    |

| BW                    | Unity Gain Frequency              | $I_{OUT} = 2mA, V_{OUT} = 1V$            | 1    | 2   |     | MHz   |

| V <sub>out</sub>      | Output Saturation voltage         | $I_{OUT} = 20$ mA, $V_{FB} = HIGH$       |      | 100 | 250 | mV    |

| TRANSC                | Output Transconductance           | I <sub>OUT</sub> = 1mA to 20mA           |      | 2.5 |     | mA/mV |

| I <sub>LEAK</sub>     | Output Leakage Current            | $V_{OUT} = 16V, V_{FB} = 0$              |      | 200 | 400 | nA    |

| I <sub>OUT(MAX)</sub> | Maximum Output Current            | V <sub>OUT</sub> = 0.3V                  | 20   |     |     | mA    |

<sup>1.</sup> Thermal Characteristics ( $\Theta_{JA}$ ) 5-lead, SOT-23: 255°C/W

# **TYPICAL PERFORMANCE CHARACTERISTICS**

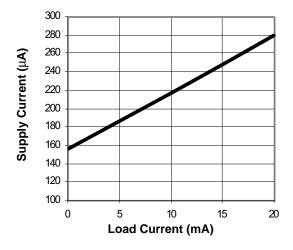

# **Supply Current vs. Load Current**

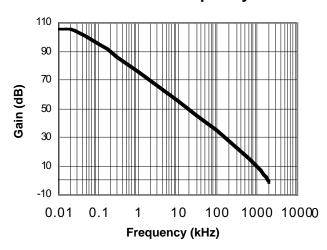

# **Power-Supply Rejection Ratio vs. Frequency**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

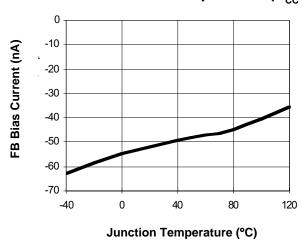

FB Bias Current vs. Temperature ( $V_{cc}$ =2.5V)

Gain vs. Frequency

Doc. No. 4007, Rev. L

5

### APPLICATIONS INFORMATION

The CAT102 adjustable shunt regulator features isolated supply inputs and outputs, ideal for isolated power-supply applications using an optocoupler in the feedback path. The CAT102 sinks 20mA with V<sub>OUT</sub> at 0.3V. The wide input supply range allows the device to operate from 2.2V to 18V. The CAT102 compares the FB input to a precision 600mv reference. If the FB input is low, the OUT pin sinks no current. If FB rises above 600mV, the OUT pin sinks up to 20mA.

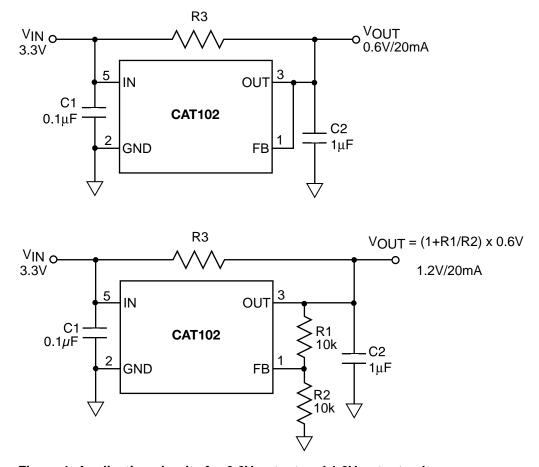

Figure 1 shows the CAT102 configured as a shunt regulator. To generate an output voltage of 0.6V, the FB pin has to be directly connected to the OUT pin. A 1.0μF capacitor from OUT to GND is recommended when the output voltage is 0.6V. A resistor-divider connected from OUT to GND is used to produce a higher output voltage as set by the following equation:

$$V_{OUT} = (1 + R1/R2) \times 0.6V$$

The current limit can be adjusted by using a resistor R3 connected between the IN and OUT pins. For example, a 3.3V supply  $V_{IN}$  is associated with R3 =  $135\Omega$ , and a 10V supply works best with R3 =  $470\Omega$ . The CAT102 shunt regulator is limited to low-current applications with the OUT pin capable of sinking up to 20mA max.

Figure 1. Application circuits for 0.6V output and 1.2V output voltages

# **TYPICAL APPLICATIONS**

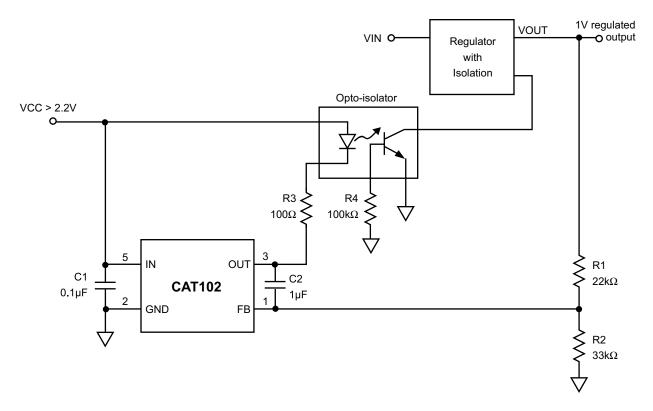

Figure 2. Opto-Feedback Application Circuit

In order to allow proper operation of the optocoupler and the CAT102, the supply voltage VCC must be greater than 2.2V.

# **PACKAGE OUTLINES**

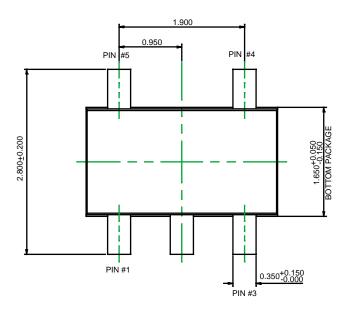

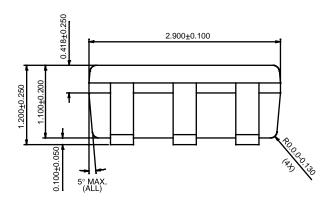

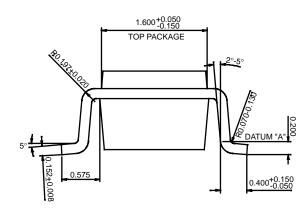

# **5 LEAD SOT-23**

#### NOTES:

- ALL DIMENSIONS ARE IN MM.

- 2. PACKAGE OUTLINE DIMENSIONS INCLUSIVE OF METAL BURR.

- 3. PACKAGE OUTLINE EXCLUSIVE OF MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.076MM.

- 4. ALL PACKAGE SURFACE TO BE MIRROR FINISH.

- 5. MOLDING WITH DIE FACING UP, AND FORMING WITH DIE FACING DOWN.

- 6. FOOT LENGTH TO BE MEASURED AT THE INTERCEPT POINT OF EXTERNAL LEADS AND DATUM "A".

- 7. LEADFINISH PLATING: 0.00762 MM 0.0254 MM. PACKAGE OUTLINE EXCLUSIVE OF LEADFINISH PLATING.

### Copyrights, Trademarks and Patents

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following:

DPP TM AE2 TM

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company's corporate office at 408.542.1000.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 1250 Borregas Avenue Sunnyvale, CA 94089 Phone: 408.542.1000

Fax: 408.542.1200

www.catalyst-semiconductor.com

Publication #: 4007 Revison: L

Issue date: 8/20/03 Type: Final