#### CMOS Quad 2-Input Exclusive-OR gate in bare die form

Rev 1.0 19/09/18

#### Description

The CD4070B provides the system designer with direct implementation of the Exclusive-OR function. The device has equal source and sink current capabilities and conforms to standard B series output drive. Device outputs are buffered which improves transfer characteristics by providing very high gain. The device is capable of driving x2 low power TTL loads or x1 LSTTL load. The CD4070B is primarily used for higher voltage acceptance and where low power dissipation and/or high noise immunity are required.

#### **Ordering Information**

The following part suffixes apply:

- No suffix MIL-STD-883 /2010B Visual Inspection

- "H" MIL-STD-883 /2010B Visual Inspection+ MIL-PRF-38534 Class H LAT

- "K" MIL-STD-883 /2010A Visual Inspection (Space)

+ MIL-PRF-38534 Class K LAT

LAT = Lot Acceptance Test.

For further information on LAT process flows see below.

www.siliconsupplies.com\quality\bare-die-lot-qualification

#### Supply Formats:

- Default Die in Waffle Pack (400 per tray capacity)

- Sawn Wafer on Tape On request

- Unsawn Wafer On request

- Die Thickness <> 635µm(25 Mils) On request

- Assembled into Ceramic Package On request

#### Features:

- High Input Voltage up to 20V

- Symmetrical Output Characteristics

- Max input current 1µA at 18V over full Military Temperature Range

- Low Power TTL compatible

- Specified at 5V, 10V & 15V

- Direct drop-in replacement for obsolete components in long term programs.

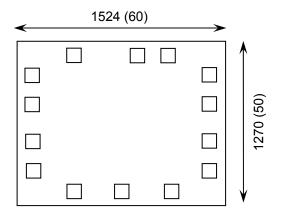

#### Die Dimensions in µm (mils)

#### **Mechanical Specification**

| Die Size (Unsawn)      | 1524 x 1270<br>50 x 37  | μm<br>mils |

|------------------------|-------------------------|------------|

| Minimum Bond Pad Size  | 102 x 102<br>4 x 4      | µm<br>mils |

| Die Thickness          | 635 (±20)<br>25 (±0.79) | μm<br>mils |

| Top Metal Composition  | Al 1%Si 1.1μ            | m          |

| Back Metal Composition | N/A – Bare S            | Si         |

#### Rev 1.0 19/09/18

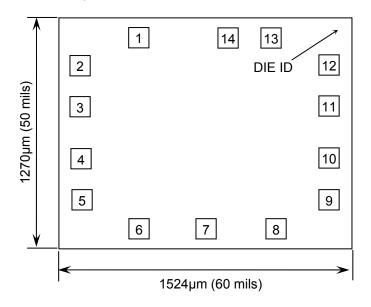

### Pad Layout and Functions

| PAD                                           | FUNCTION        |  |  |  |  |

|-----------------------------------------------|-----------------|--|--|--|--|

| 1                                             | 1A              |  |  |  |  |

| 2                                             | 1B              |  |  |  |  |

| 3                                             | 1Y              |  |  |  |  |

| 4                                             | 2Y              |  |  |  |  |

| 5                                             | 2A              |  |  |  |  |

| 6                                             | 2B              |  |  |  |  |

| 7                                             | V <sub>SS</sub> |  |  |  |  |

| 8                                             | 3A              |  |  |  |  |

| 9                                             | 3B              |  |  |  |  |

| 10                                            | 3Y              |  |  |  |  |

| 11                                            | 4Y              |  |  |  |  |

| 12                                            | 4A              |  |  |  |  |

| 13                                            | 4B              |  |  |  |  |

| 14                                            | $V_{DD}$        |  |  |  |  |

| CONNECT CHIP BACK TO V <sub>DD</sub> OR FLOAT |                 |  |  |  |  |

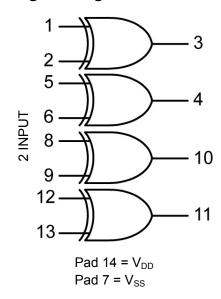

### Logic Diagram

#### **Truth Table**

| INP                           | JTS         | OUTPUT           |  |  |  |  |

|-------------------------------|-------------|------------------|--|--|--|--|

| Α                             | В           | Υ                |  |  |  |  |

| L<br>H<br>L<br>H              | L<br>L<br>H | L<br>H<br>H<br>L |  |  |  |  |

| H = High level (steady state) |             |                  |  |  |  |  |

| L = Low level (steady state)  |             |                  |  |  |  |  |

$$Y = A \oplus B$$

Rev 1.0 19/09/18

## Absolute Maximum Ratings<sup>1</sup>

| PARAMETER                                                   | SYMBOL                             | VALUE                        | UNIT |

|-------------------------------------------------------------|------------------------------------|------------------------------|------|

| DC Supply Voltage (Referenced to V <sub>SS</sub> )          | $V_{DD}$                           | -0.5 to +20                  | V    |

| DC Input or Output Voltage (Referenced to V <sub>SS</sub> ) | V <sub>IN,</sub> V <sub>OUT</sub>  | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Storage Temperature Range                                   | T <sub>STG</sub>                   | -65 to 150                   | °C   |

| Input Current or Output Current (per Pad)                   | I <sub>IN</sub> , I <sub>OUT</sub> | ±10                          | mA   |

| Power Dissipation in Still Air                              | P <sub>D</sub>                     | 500                          | mW   |

<sup>1.</sup> Operation above the absolute maximum rating may cause device failure. Operation at the absolute maximum ratings, for extended periods, may reduce device reliability. 2. Measured in plastic DIP package, results in die form are dependent on die attach and assembly method.

## Recommended Operating Conditions<sup>3</sup> (Voltages referenced to V<sub>SS</sub>)

| PARAMETER                        | SYMBOL           | MIN | MAX      | UNITS |

|----------------------------------|------------------|-----|----------|-------|

| Supply Voltage                   | $V_{DD}$         | 3.0 | 18       | V     |

| DC Input Voltage, Output Voltage | $V_{IN,}V_{OUT}$ | 0   | $V_{DD}$ | V     |

| Operating Temperature Range      | TJ               | -55 | +125     | °C    |

<sup>3.</sup> This device contains protection circuitry against damage due to high static voltages or electric fields. However, any voltage higher than maximum rated voltages to this high-impedance circuit should be avoided. For proper operation,  $V_{IN}$  &  $V_{OUT}$  should be constrained to the range  $V_{SS} \le (V_{IN} \text{ or } V_{OUT})$   $\le V_{DD}$ . Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ). Unused outputs must be left open.

#### DC Electrical Characteristics (Voltages referenced to Vss)

| PARAMETER SYMBO                     | SYMBOL          | YMBOL V <sub>DD</sub> | CONDITIONS                                 |       | UNITS |             |        |

|-------------------------------------|-----------------|-----------------------|--------------------------------------------|-------|-------|-------------|--------|

|                                     | OTHIBOL         |                       | CONDITIONS                                 | 25°C  | 85°C  | FULL RANGE⁴ | 5.4110 |

| Minimum                             |                 | 5V                    | V <sub>OUT</sub> = 0.5V                    | 3.5   | 3.5   | 3.5         |        |

| High-Level                          | V <sub>IH</sub> | 10V                   | V <sub>OUT</sub> = 1.0V                    | 7     | 7     | 7           | V      |

| Input Voltage                       |                 | 15V                   | V <sub>OUT</sub> = 1.5V                    | 11    | 11    | 11          |        |

| Maximum                             |                 | 5V                    | $V_{OUT}$ = 0.5V or $V_{DD}$ -0.5V         | 1.5   | 1.5   | 1.5         |        |

| Low-Level                           | V <sub>IL</sub> | 10V                   | $V_{OUT} = 0.5V \text{ or } V_{DD} - 0.5V$ | 3     | 3     | 3           | V      |

| Input Voltage                       |                 | 15V                   | $V_{OUT}$ = 0.5V or $V_{DD}$ -0.5V         | 4     | 4     | 4           |        |

| Minimum High-Level Output Voltage   |                 | 5V                    |                                            | 4.95  | 4.95  | 4.95        | V      |

|                                     | V <sub>OH</sub> | 10V                   | $V_{IN} = 0$ or $V_{DD}$                   | 9.95  | 9.95  | 9.95        |        |

|                                     |                 | 15V                   |                                            | 14.95 | 14.95 | 14.95       |        |

| Maximum                             |                 | 5V                    | V <sub>IN</sub> = V <sub>DD</sub> or 0     | 0.05  | 0.05  | 0.05        | V      |

| Low-Level                           | V <sub>OL</sub> | 10V                   |                                            | 0.05  | 0.05  | 0.05        |        |

| Output<br>Voltage                   |                 | 15V                   |                                            | 0.05  | 0.05  | 0.05        |        |

| Maximum<br>Input Leakage<br>Current | I <sub>IN</sub> | 18V                   | $V_{IN} = V_{DD}$ or $V_{SS}$              | ±0.1  | ±.0.1 | ±1.0        | μA     |

| Maximum<br>Quiescent<br>Supply      | 5V              | 5V                    | $V_{IN} = V_{DD}$ or $V_{SS}$              | 0.25  | 7.5   | 7.5         | μΑ     |

|                                     | l <sub>DD</sub> | 10V                   |                                            | 0.5   | 15    | 15          |        |

|                                     | 15V<br>20V      | 15V                   | $I_{OUT} = 0\mu A$                         | 1.0   | 30    | 30          |        |

| Current                             |                 |                       | 5.0                                        | 150   | 150   |             |        |

Rev 1.0 19/09/18

### DC Electrical Characteristics Continued (Voltages referenced to Vss)

| PARAMETER                                  | SYMBOL              | V <sub>DD</sub> | CONDITIONS                                               |       | LIMIT | UNITS       |       |

|--------------------------------------------|---------------------|-----------------|----------------------------------------------------------|-------|-------|-------------|-------|

|                                            |                     | ₹ 00            | CONDITIONS                                               | 25°C  | 85°C  | FULL RANGE⁴ | OMITO |

| Minimum Output<br>Low (Sink) Current       |                     | 5V              | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{OL} = 0.4V$  | 0.64  | 0.51  | 0.36        |       |

|                                            | l <sub>OL</sub>     | 10V             | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{OL} = 0.5V$  | 1.6   | 1.3   | 0.9         | mA    |

|                                            |                     | 15V             | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{OL} = 1.5V$  | 4.2   | 3.4   | 2.4         |       |

| Minimum Output<br>High (Source)<br>Current | ce) I <sub>OH</sub> | 5V              | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{OH} = 2.5V$  | -3.0  | -2.4  | -1.7        |       |

|                                            |                     | 5V              | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{OH} = 4.6V$  | -0.64 | -0.51 | -0.36       | mA    |

|                                            |                     | 10V             | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{OH} = 9.5V$  | -1.6  | -1.3  | -0.9        |       |

|                                            |                     | 15V             | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{OH} = 13.5V$ | -4.2  | -3.4  | -2.4        |       |

**<sup>4.</sup>** . −55°C ≤ T<sub>J</sub> ≤ +125°C

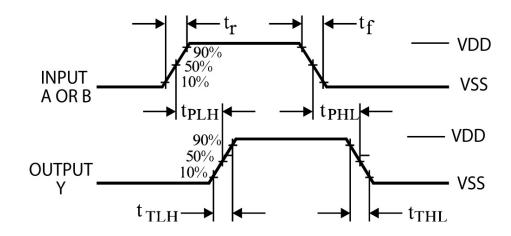

## AC Electrical Characteristics<sup>5</sup>

| PARAMETER                      | SYMBOL                                | V <sub>DD</sub> | CONDITIONS                                                     | TYPICAL | LIMITS |             | UNITS  |

|--------------------------------|---------------------------------------|-----------------|----------------------------------------------------------------|---------|--------|-------------|--------|

|                                |                                       | ₩ 00            | CONDITIONS                                                     | 25°C    | 85°C   | FULL RANGE⁴ | Oitilo |

| Propagation Delay,             |                                       | 5V              | $C_L = 50pF$ ,                                                 | 125     | 250    | 500         |        |

| Input A or B to                | t <sub>PLH</sub> , t <sub>PHL</sub>   | 10V             | $R_L = 200 k\Omega$                                            | 60      | 120    | 240         | ns     |

| Output Y (Figure 1)            |                                       | 15V             | $t_r = t_f = 20$ ns                                            | 45      | 90     | 180         |        |

| Output Transition              | t <sub>TLH</sub> , t <sub>THL</sub> 1 | 5V              | $C_L$ = 50pF,<br>$R_L$ = 200k $\Omega$<br>$t_r$ = $t_f$ = 20ns | 100     | 200    | 400         | ns     |

| Time, Any Output<br>(Figure 1) |                                       | 10V             |                                                                | 50      | 100    | 200         |        |

|                                |                                       | 15V             |                                                                | 40      | 80     | 160         |        |

| Input Capacitance              | C <sub>IN</sub>                       | -               | $C_L = 50 pF,$<br>$R_L = 200 k\Omega$<br>$t_r = t_f = 20 ns$   | 5       | 7.5    | 7.5         | pF     |

<sup>5.</sup> Not production tested in die form, characterized by chip design and tested in package.

Rev 1.0 19/09/18

### **Switching Waveform**

Figure 1 – Propagation Delay, Transition Timing

DISCLAIMER: The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Silicon Supplies Ltd hereby disclaims any and all warranties and liabilities of any kind.

LIFE SUPPORT POLICY: Silicon Supplies Ltd components may be used in life support devices or systems only with the express written approval of Silicon Supplies Ltd, if a failure of such components can reasonably be expected to cause the failure of that life support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.