# Low Power Microprocessor Supervisory Circuits CN705/706/707/708/813

### **Description:**

CN705/706/707/708/813 series is a family of microprocessor (uP) supervisory circuit that monitors microprocessor's supply voltage and battery voltage. CN705/706/707/708/813 series integrates uP reset circuit with 200ms delay, Watchdog, manual reset circuit and a power fail comparator with 1.22V threshold. These devices reduce system complexity, hence improve system reliability.

CN705/706/707/708/813 series has several functional options. Each device generates a reset signal when VCC is lower than reset threshold. In addition, CN705, CN706 and CN813 have a watchdog timer whose timeout period is 1.6s. CN707 and CN708 provide both active low and active high reset signals, but have no watchdog function. CN813 are same as CN705/706 except active high reset is provided instead of active low.

CN705/706/707/708/813 series is ideal for applications in automotive systems, computers, controllers and intelligent instruments. All devices are available in 8 pin DIP and 8 pin SOP package.

### **Applications:**

- Computers

- Controllers

- Intelligent instruments

- Automotive systems

#### **Features:**

- Guaranteed reset valid at V<sub>CC</sub>=1.15V

- Reset threshold can be from 2.6V to 5.0V with 0.1V step.

- Low operating current: 52uA @5V

- Reset pulse width: 200ms

- Independent watchdog timer, 1.6s timeout(CN705/706/813)

- Voltage monitor for power fail or low battery warning

- Pin-to-pin compatible with industry standard 705/706/707/708/813

- Available in DIP8 and SOP8

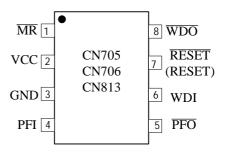

### **Pin Assignment:**

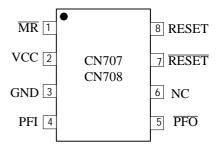

# **Typical Application Circuit:**

Figure 1 Typical Application Circuit

#### **Device Function Reference Table**

| David Ma | Reset     | Reset active | Watchdog | Operating   |  |

|----------|-----------|--------------|----------|-------------|--|

| Part No. | threshold | Low or High  | Function | Temperature |  |

| CN705    | 4.65V     | Low          | Yes      | - 4085      |  |

| CN707    | 4.65V     | Low and High | No       | - 4085      |  |

| CN813L   | 4.65V     | High         | Yes      | - 4085      |  |

| CN706    | 4.4V      | Low          | Yes      | - 4085      |  |

| CN708    | 4.4V      | Low and High | No       | - 4085      |  |

| CN813M   | 4.4V      | High         | Yes      | - 4085      |  |

| CN706J   | 4.0V      | Low          | Yes      | - 4085      |  |

| CN708J   | 4.0V      | Low and High | No       | - 4085      |  |

| CN813J   | 4.0V      | High         | Yes      | - 4085      |  |

| CN706T   | 3.08V     | Low          | Yes      | - 4085      |  |

| CN708T   | 3.08V     | Low and High | No       | - 4085      |  |

| CN813T   | 3.08V     | High         | Yes      | - 4085      |  |

| CN706S   | 2.93V     | Low          | Yes      | - 4085      |  |

| CN708S   | 2.93V     | Low and High | No       | - 4085      |  |

| CN813S   | 2.93V     | High         | Yes      | - 4085      |  |

| CN706R   | 2.63V     | Low          | Yes      | - 4085      |  |

| CN708R   | 2.63V     | Low and High | No       | - 4085      |  |

| CN813R   | 2.621/    | III.ah       | Vac      | 40 95       |  |

| (CN706P) | 2.63V     | High         | Yes      | - 4085      |  |

Note: Please contact our sales office for other reset threshold from 2.6V to 5.0V

2

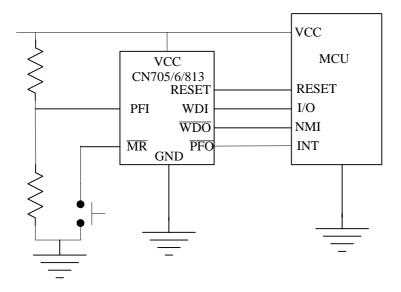

# **Ordering Information:**

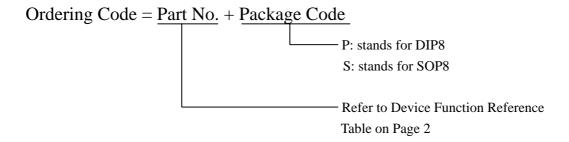

### **Block Diagram:**

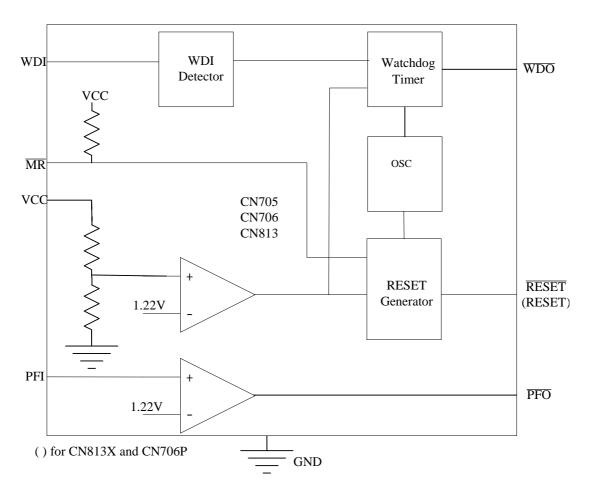

Figure 2 CN705/706/813 block Diagram

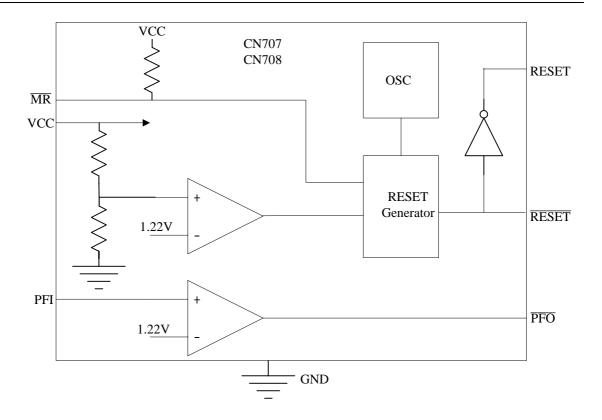

Figure 3 CN707/708 Block Diagram

# **Pin Description:**

|        | Pin No. |        |       |                                                                                                                                                                                                                                                                                                                                |

|--------|---------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CN705  | CN707   | CN813X | Name  | Function Description                                                                                                                                                                                                                                                                                                           |

| CN706X | CN708X  | CN706P |       |                                                                                                                                                                                                                                                                                                                                |

| 1      | 1       | 1      | MR    | Manual reset input. When voltage at MR is pulled low, a reset pulse will be triggered. The active low input has a pull up current. It can be driven by TTL or CMOS logic as well as shorted to GND with a switch.                                                                                                              |

| 2      | 2       | 2      | VCC   | Positive supply input                                                                                                                                                                                                                                                                                                          |

| 3      | 3       | 3      | GND   | Negative supply input                                                                                                                                                                                                                                                                                                          |

| 4      | 4       | 4      | PFI   | Power fail monitor input. When the voltage at PFI is below 1.22V, PFO goes low. Connect PFI to GND or VCC when not used.                                                                                                                                                                                                       |

| 5      | 5       | 5      | PFO   | Power fail monitor output. When the voltage at PFI is less than 1.22V, PFO goes low; otherwise PFO goes high.                                                                                                                                                                                                                  |

| 6      |         | 6      | WDI   | Watchdog input. If WDI remains high or low for 1.6s, the on chip watchdog timer runs out and WDO goes low. Floating WDI or connecting WDI to high impedance three state buffer disables watchdog function. The watchdog timer clears whenever RESET is asserted, or WDI is three stated, or WDI sees a rising or falling edge. |

| 7      | 7       |        | RESET | Active low reset output. $\overline{RESET}$ stays in low if VCC is lower than reset threshold; it remains in low for 200ms after VCC becomes higher than reset threshold or $\overline{MR}$ goes from low to high.(Figure 5)                                                                                                   |

| 8      |         | 8      | WDO   | Watchdog output. WDO goes low if watchdog timer finishes its 1.6s count, and will not go high again until the watchdog timer is cleared. Whenever VCC is below reset threshold, WDO stays low, and as soon as VCC rises above reset threshold, WDO goes high without delay.                                                    |

|        | 8       | 7      | RESET | Active high reset output. RESET stays in high if VCC is lower than reset threshold; it remains in high for 200ms after VCC becomes higher than reset threshold or MR goes from low to high. (Figure 5)                                                                                                                         |

### **Absolute Maximum Ratings:**

| Terminal Voltage(With | respect to GND): | Thermal Resistance (DIP8)120  | ) /W |

|-----------------------|------------------|-------------------------------|------|

| V <sub>CC</sub>       | 0.3V to 6.0V     | Power Dissipation (SOP8)190   | ) /W |

| Other Inputs          | 0.3V to 6.0V     | Maximum Junction Temperature  | 150  |

| Terminal Current      |                  | Operating Temperature 40 to   | 85   |

| V <sub>CC</sub>       | 20mA             | Storage Temperature 65 to     | 150  |

| GND                   | 20mA             | Lead Temperature(Soldering)30 | 00   |

| All Input Pins        | 20mA             | ESD Rating(HBM)               | 2KV  |

| All Output Pins       | 20mA             |                               |      |

Stresses beyond those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{CC}=5V, T_A=-40)$  to 85 , Typical values are measured at  $T_A=25$  ,unless otherwise noted)

| Parameters                    | Symbol            | Test Condition                                       | ons                 | Min                | Тур                  | Max                 | Unit |  |

|-------------------------------|-------------------|------------------------------------------------------|---------------------|--------------------|----------------------|---------------------|------|--|

| Operating Voltage<br>Range    | V <sub>CC</sub>   |                                                      |                     | 1.15               |                      | 5.5                 | V    |  |

| Supply Cumont                 | _                 | CN705/706X                                           | /813X               |                    | 52                   | 105                 | uA   |  |

| Supply Current                | $I_{VCC}$         | CN707/708X                                           |                     |                    | 30                   | 60                  |      |  |

|                               |                   | CN705/707/8                                          | 13L                 | 4.5                | 4.65                 | 4.75                |      |  |

|                               |                   | CN706/708/8                                          | 13M                 | 4.25               | 4.4                  | 4.5                 |      |  |

| Reset Threshold               | V                 | CN706J/708J                                          | 7/813J              | 3.9                | 4.0                  | 4.1                 | V    |  |

| Reset Tilleshold              | V <sub>RES</sub>  | CN706T/708                                           | T/813T              | 3.0                | 3.08                 | 3.15                | V    |  |

|                               |                   | CN706S/708S                                          | S/813S              | 2.85               | 2.93                 | 3.0                 |      |  |

|                               |                   | CN706P/706                                           | 2.55                | 2.63               | 2.70                 |                     |      |  |

| Reset Threshold<br>Hysteresis | H <sub>VRES</sub> |                                                      |                     |                    | 0.01V <sub>RES</sub> |                     | V    |  |

| Reset Pulse Width             | t <sub>RES</sub>  |                                                      |                     | 140                | 200                  | 280                 | ms   |  |

| RESET or RESET                | V <sub>OH1</sub>  | I <sub>SOURCE</sub> =800<br>I <sub>SOURCE</sub> =8uA |                     | V <sub>CC</sub> -1 | 2                    |                     | V    |  |

| Output Voltage                | V <sub>OL1</sub>  | I <sub>SINK</sub> =3.2mA<br>I <sub>SINK</sub> =150uA |                     |                    |                      | 0.3<br>0.3          | V    |  |

| Watchdog timeout period       | $t_{ m WD}$       |                                                      |                     | 1                  | 1.6                  | 2.25                | S    |  |

| WDI Pulse Width               | $t_{\mathrm{WP}}$ | V <sub>CC</sub> =5V                                  |                     | 50                 |                      |                     | 20   |  |

| WDIT tilse Width              |                   | V <sub>CC</sub> <4.5V                                |                     | 120                |                      |                     | ns   |  |

| WDI Input                     |                   | Low                                                  |                     |                    | (                    | 0.16V <sub>CC</sub> |      |  |

| WDI Input Threshold           |                   | High                                                 | V <sub>CC</sub> =5V | 3.5                |                      |                     | V    |  |

|                               |                   | V <sub>CC</sub> <4.5V                                |                     | 0.75V <sub>0</sub> | CC                   |                     |      |  |

# **Electrical Characteristics (Continued)**

| Parameters        | Symbol             | Test Conditi                                           | ons                   | Min.                 | Тур. | Max.                | Unit     |  |

|-------------------|--------------------|--------------------------------------------------------|-----------------------|----------------------|------|---------------------|----------|--|

| WDI Pull up       |                    | X7 . X7                                                |                       | 125                  | 250  | 500                 | K        |  |

| Resistance        |                    | $V_{CC}>V_{RES}$                                       |                       | 123                  | 230  | 300                 | N.       |  |

| WDI Pull down     |                    | W . W                                                  |                       | 88                   | 175  | 350                 | K        |  |

| Resistance        |                    | $V_{CC}>V_{RES}$                                       |                       | 00                   | 1/3  | 330                 | Λ        |  |

| WDO Output        | $V_{\mathrm{OH2}}$ | I <sub>SOURCE</sub> =800                               | )uA                   | V <sub>CC</sub> -1.2 | 2    |                     | V        |  |

| Voltage           | $V_{OL2}$          | I <sub>SINK</sub> =3.2mA                               | 1                     |                      |      | 0.3                 | V        |  |

|                   |                    |                                                        | V <sub>CC</sub> =5V   | 100                  | 250  | 600                 | uA       |  |

| MR Pull up        |                    | MR=0V                                                  | V <sub>CC</sub> =4V   | 60                   | 152  | 360                 | uA       |  |

| Current           |                    | NIK=0 V                                                | V <sub>CC</sub> =3V   | 32                   | 75   | 180                 |          |  |

|                   |                    |                                                        | V <sub>CC</sub> =2.5V | 20                   | 44   | 105                 |          |  |

| MR Pulse Width    | T                  | V <sub>CC</sub> =5V                                    |                       | 150                  |      |                     |          |  |

| Wik Pulse Widdi   | $T_{MR}$           | V <sub>CC</sub> <4.5V                                  |                       | 500                  | 500  |                     | ns       |  |

|                   |                    | V 5V                                                   | Low                   |                      |      | 0.8                 |          |  |

| MR Input          |                    | V <sub>CC</sub> =5V                                    | High                  | 2.0                  |      |                     | V        |  |

| Threshold         |                    | V 45V                                                  | Low                   |                      | (    | 0.16V <sub>CC</sub> | V        |  |

|                   |                    | V <sub>CC</sub> <4.5V                                  | High                  | 0.65V <sub>C</sub>   | С    |                     |          |  |

| MR's Delay to     | 4.00               | V <sub>CC</sub> =5V                                    |                       |                      |      | 250                 | na       |  |

| RESET             | LMD                | $V_{\rm CC}$ <4.5V                                     |                       |                      |      | 750                 | ns       |  |

| PFI Input         | <b>X</b> 7         |                                                        |                       | 1.184                | 1.22 | 1.256               | V        |  |

| Threshold         | $V_{PFI}$          |                                                        |                       | 1.104                | 1.22 | 1.230               | <b>v</b> |  |

| PFI Input Current | I <sub>PFI</sub>   |                                                        |                       |                      | 0    |                     | nA       |  |

| PFO Output        | V <sub>OH3</sub>   | I <sub>SOURCE</sub> =800uA<br>I <sub>SINK</sub> =3.2mA |                       | V <sub>CC</sub> -1.2 | 2    |                     | V        |  |

| Voltage           | V <sub>OL3</sub>   |                                                        |                       | 0.3                  |      | <b>v</b>            |          |  |

Note: Parts are 100% production tested at 25°C. Specifications over full temperature range are guaranteed by 6-sigma statistical process control and by design

Rev.1

7

### Typical Operating Characteristics

**CN706** Operating Current vs. Operating Voltage 55 50 Operating Current(uA) 45 40 35 30 25 20 2.5 3.5 4.5 5 5.5 Operating Voltage(V)

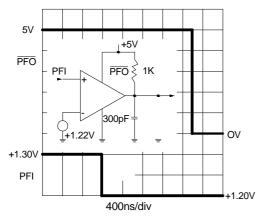

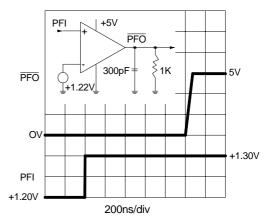

Power-fail Comparator assertion Response Time

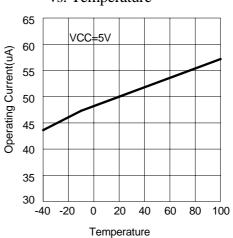

CN706 Operating Current vs. Temperature

Power-fail Comparator De-assertion Response Time

### **Detailed Description:**

CN705/706/707/708/813 series is a microprocessor supervisory circuit that monitors the power supply to digital circuits such as microprocessor, controller and memory . These devices assert reset during power up, power down or brownout condition to prevent code execution errors.

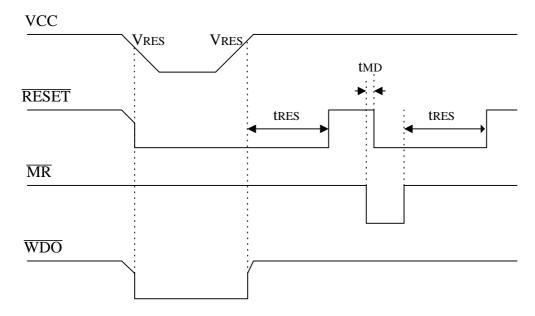

#### **RESET output**

On power up, once VCC reaches 1.15V, CN705/706/707/708/813 series output a reset signal . As VCC increases, the reset signal stays valid; When VCC rises above reset threshold, an internal timer releases RESET ( $\overline{\text{RESET}}$ ) after 200ms. RESET ( $\overline{\text{RESET}}$ ) becomes valid once VCC dips below reset threshold during power down or in brownout condition. If brownout occurs in the middle of a previously initiated

reset pulse, the pulse will continue for at least another 140ms. On power down, once VCC falls below reset threshold, RESET stays valid—and is guaranteed in the correct logic state—until VCC drops below 1.15V for the whole temperature range. Please refer to Figure 5.

CN705/706 series provide active low RESET signal; CN707/708 series provide both active high and active low RESET signals; CN813 series provide active high RESET signal.

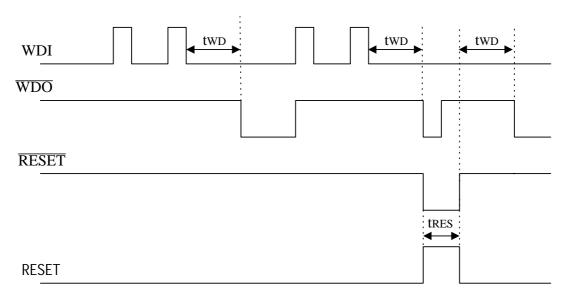

#### **Watchdog Timer**

CN705/706/813 series have an independent watchdog timer that can monitor uP's activity. If uP does not toggle the watchdog input (WDI) within 1.6s and WDI is not three-stated, WDO goes low. As long as RESET is asserted, or WDI is three-stated, or WDI is left floating, the watchdog timer stays cleared and will not count, in this case WDO is in high state. When VCC stays below reset threshold, WDO goes low whether or not the watchdog timer has timed out yet. Please refer to figure 4.

#### **Manual Reset**

Manual reset input allows reset signal to be triggered by push button or switch. The push button or switch is effectively debounced by 140ms minimum reset pulse width.  $\overline{\mathtt{MR}}$  is TTL/CMOS logic compatible.  $\overline{\mathtt{MR}}$  can be used to force a watchdog timeout to generate a reset pulse in CN705/706/813 series by connecting WDO to  $\overline{\mathtt{MR}}$  Please refer to Figure 5.

#### **Power fail Comparator**

The power fail comparator can be used for various purpose because its output and noninverting input are not internally connected. The inverting input is internally connected to a 1.22V reference voltage.

Note 1:  $\overline{RESET}$  (RESET) is triggered by  $\overline{MR}$ Note 2: RESET is for CN813X and CN706P only

Figure 4 Watchdog Timing

Rev.1

Note: Active high RESET is the inverse of the RESET shown

Figure 5  $\overline{RESET}$ , $\overline{MR}$  and  $\overline{WDO}$  timing with WDI floating

#### **Application Information**

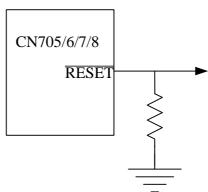

#### Ensuring a Valid $\overline{\text{RESET}}$ Output Down to VCC=0V

When VCC falls below 1.15V, the CN705/706/707/708 series  $\overline{\text{RESET}}$  output no longer sinks current, it becomes an open circuit, hence  $\overline{\text{RESET}}$  output is at undetermined voltage. If a pull-down resistor is added from  $\overline{\text{RESET}}$  pin to GND as shown in Figure 6, then  $\overline{\text{RESET}}$  output will be held at low state. The resistor's value is not critical. it should be about 100K , large enough not to load  $\overline{\text{RESET}}$ , small enough to pull RESET to ground.

Figure 6 RESET Valid to Ground Circuit

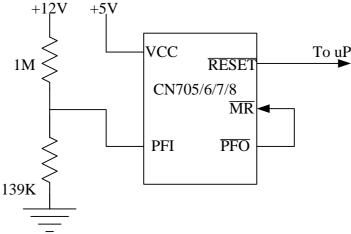

#### Monitoring voltages other than the unregulated DC Input

You can monitor voltages other than the unregulated DC by connecting a voltage divider to PFI and adjusting the ratio appropriately. If required, add a hysteresis by connecting a resistor (with a value approximately 10 times the sum of 2 resistors in voltage divider network) between PFI and PFO. A capacitor between PFI and GND will reduce the power fail circuit's sensitivity to high-frequency noise on

the line being monitored. RESET can be asserted on the other voltage in addition to VCC line by connecting PFO pin to MR pin, in this case, a RESET pulse will be initiated when PFI drops below 1.22V. Figure 7 shows CN705/706/707/708 series configured to assert RESET when VCC falls below reset threshold, or when +12V power supply falls below 10V.

Figure 7 Monitoring Both +5V and +12V

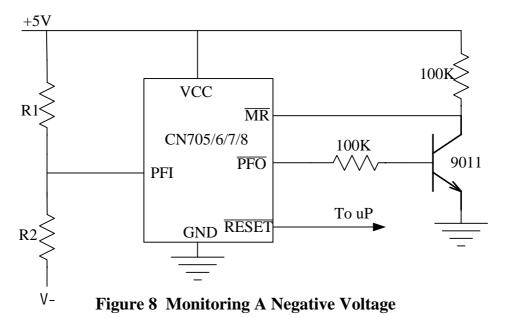

#### Monitoring a Negative Voltage

The power fail comparator can also monitor a negative supply rail as shown in Figure 8. When the negative rail is good (A negative voltage of large magnitude), PFO is low, and when the negative rail is degraded(A negative voltage of less magnitude), PFO is high. By adding the resistors and transistor as shown, a high PFO triggers a RESET pulse. As long as PFO remains high, the CN705/706/707/708/813 series will keep RESET asserted. Note that the circuit's accuracy depends on the PFI threshold tolerance, the VCC line and the resistors.

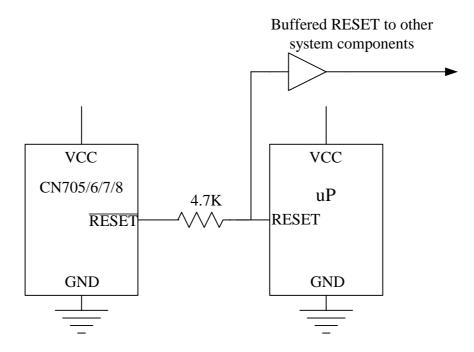

#### **Interfacing to uPs with Bidirectional Reset Pins**

uPs with bi-directional reset pins, such as the MOTOROLA 68HC11 series, can contend with CN705/706/707/708/813 series RESET output. For example, if the RESET output is driven high and uP wants to pull it low, indeterminate logic levels may result. To correct this, connect a 4.7K resistor

between the RESET output and the uP reset I/O as shown in Figure 9. Buffer the RESET output to other system components.

Figure 9 Interfacing to uPs with Bidirectional Reset I/O

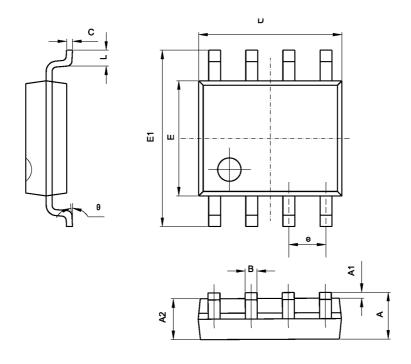

# Package Information

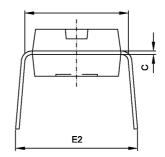

SOP8 Package Outline Dimensions

| Symbol     | Dimensions In Millimeters |       | Dimensions | s In Inches |

|------------|---------------------------|-------|------------|-------------|

|            | Min                       | Max   | Min        | Мах         |

| A          | 1.350                     | 1.750 | 0.053      | 0.069       |

| <b>A</b> 1 | 0.100                     | 0.250 | 0.004      | 0.010       |

| A2         | 1.350                     | 1.550 | 0.053      | 0.061       |

| В          | 0.330                     | 0.510 | 0.013      | 0.020       |

| С          | 0.190                     | 0.250 | 0.007      | 0.010       |

| D          | 4.780                     | 5.000 | 0.188      | 0.197       |

| E          | 3.800                     | 4.000 | 0.150      | 0.157       |

| E1         | 5.800                     | 6.300 | 0.228      | 0.248       |

| 0          | 1.270(TYP)                |       | 0.05       | 0(TYP)      |

| L          | 0.400                     | 1.270 | 0.016      | 0.050       |

| θ          | 0°                        | 8°    | 0°         | 8°          |

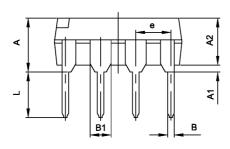

# DIP8 Package Outline Dimensions

| Symbol | Dimensions I | Dimensions In Millimeters |            | ns In Inches |  |

|--------|--------------|---------------------------|------------|--------------|--|

|        | Min          | Max                       | Min        | Max          |  |

| Α      | 3.710        | 4.310                     | 0.146      | 0.170        |  |

| A1     | 0.510        |                           | 0.020      |              |  |

| A2     | 3.200        | 3.600                     | 0.126      | 0.142        |  |

| В      | 0.360        | 0.560                     | 0.014      | 0.022        |  |

| B1     | 1.524(TYP)   |                           | 0.060(TYP) |              |  |

| С      | 0.204        | 0.360                     | 0.008      | 0.014        |  |

| D      | 9.000        | 9.400                     | 0.354      | 0.370        |  |

| E      | 6.200        | 6.600                     | 0.244      | 0.260        |  |

| E1     | 7.620(TYP)   |                           | 0.300(TYP) |              |  |

| е      | 2.54         | IO(TYP)                   | 0.100(TYP) |              |  |

| L      | 3.000        | 3.600                     | 0.118      | 0.142        |  |

| E2     | 8.200        | 9.400                     | 0.323      | 0.370        |  |