# CX81801-7x/8x SmartV.XX Modem V.92/V.34/V.32bis Modem in 128-Pin TQFP with CX20493 SmartDAA® and Optional CX20442 Voice Codec

- -

Data Sheet

## Revision Record

| Revision | Date      | Comments         |

|----------|-----------|------------------|

| A        | 6/2/2003  | Initial release. |

| В        | 7/22/2004 | Rev. B release.  |

© 2003, 2004 Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED 'AS IS' WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant@ and the Conexant C symbol, and SmartDAA@. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at www.conexant.com, which is incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

## **Contents**

| 1. | Intro | duction.                   |                                      | 1-1 |  |  |  |

|----|-------|----------------------------|--------------------------------------|-----|--|--|--|

|    | 1.1   | Overview                   |                                      |     |  |  |  |

|    | 1.2   | Applicat                   | tions                                | 1-2 |  |  |  |

|    | 1.3   | Features                   | S                                    |     |  |  |  |

|    |       | 1.3.1                      | General Modem Features               | 1-4 |  |  |  |

|    |       | 1.3.2                      | SmartDAA Features                    | 1-5 |  |  |  |

|    |       | 1.3.3                      | Applications                         | 1-5 |  |  |  |

|    | 1.4   | Technica                   | al Overview                          | 1-6 |  |  |  |

|    |       | 1.4.1                      | General Description                  |     |  |  |  |

|    |       | 1.4.2                      | MCU Firmware                         | 1-6 |  |  |  |

|    |       | 1.4.3                      | Operating Modes                      | 1-6 |  |  |  |

|    |       |                            | 1.4.3.1 Data/Fax Modes               |     |  |  |  |

|    |       |                            | 1.4.3.2 V.44 Data Compression        |     |  |  |  |

|    |       |                            | 1.4.3.3 Worldwide Operation          |     |  |  |  |

|    |       |                            | 1.4.3.4 TAM Mode                     |     |  |  |  |

|    |       |                            | 1.4.3.5 Speakerphone Mode (S Models) |     |  |  |  |

|    |       | 1.4.4                      | Reference Designs                    |     |  |  |  |

|    | 1.5   | Hardware Description       |                                      |     |  |  |  |

|    |       | 1.5.1 CX81801 Modem Device |                                      |     |  |  |  |

|    |       | 1.5.2                      | Digital Isolation Barrier            |     |  |  |  |

|    |       | 1.5.3                      | CX20493 SmartDAA Line Side Device    |     |  |  |  |

|    |       | 1.5.4                      | CX20442 Voice Codec                  |     |  |  |  |

|    | 1.6   | AT Com                     | Imands                               |     |  |  |  |

| 2. | Tech  | nical Sp                   | ecifications                         | 2-1 |  |  |  |

|    | 2.1   | Serial D                   | TE Interface Operation               |     |  |  |  |

|    |       | 2.1.1                      | Automatic Speed/Format Sensing       |     |  |  |  |

|    | 2.2   | Parallel                   | Host Bus Interface Operation         |     |  |  |  |

|    | 2.3   | Establis                   | hing Data Modem Connections          |     |  |  |  |

|    |       | 2.3.1                      | Dialing                              |     |  |  |  |

|    |       | 2.3.2                      | Telephone Number Directory           |     |  |  |  |

|    |       | 2.3.3                      | Modem Handshaking Protocol           |     |  |  |  |

|    |       | 2.3.4                      | Call Progress Tone Detection         |     |  |  |  |

|    |       | 2.3.5                      | Answer Tone Detection                |     |  |  |  |

|    |       | 2.3.6                      | Ring Detection                       |     |  |  |  |

|    |       | 2.3.7                      | Billing Protection                   |     |  |  |  |

|    |       | 2.3.8                      | Connection Speeds                    |     |  |  |  |

|    |       | 2.3.9                      | Automode                             |     |  |  |  |

|    | 2.4   | Data Mo                    | ode                                  |     |  |  |  |

|    |       |                            |                                      |     |  |  |  |

|    |      | 2.4.1    | Speed Buf    | fering (Normal Mode)                           |  |

|----|------|----------|--------------|------------------------------------------------|--|

|    |      | 2.4.2    | Flow Conti   | rol                                            |  |

|    |      | 2.4.3    | Escape Se    | quence Detection                               |  |

|    |      | 2.4.4    | BREAK De     | tection                                        |  |

|    |      | 2.4.5    | Telephone    | Line Monitoring                                |  |

|    |      | 2.4.6    | Fall Forwa   | rd/Fallback (V.92/V.90/V.34/V.32 bis/V.32)     |  |

|    |      | 2.4.7    | Retrain      |                                                |  |

|    |      | 2.4.8    | Programm     | able Inactivity Timer                          |  |

|    |      | 2.4.9    | DTE Signa    | I Monitoring (Serial DTE Interface Only)       |  |

|    | 2.5  | V.92 Fea | tures        |                                                |  |

|    |      | 2.5.1    | Modem-or     | n-Hold                                         |  |

|    |      | 2.5.2    | Quick Con    | nect                                           |  |

|    |      | 2.5.3    | PCM Upst     | ream                                           |  |

|    | 2.6  | Error Co | rrection and | Data Compression                               |  |

|    |      | 2.6.1    | V.42 Error   | Correction                                     |  |

|    |      | 2.6.2    | MNP 2-4 E    | Fror Correction                                |  |

|    |      | 2.6.3    | V.44 Data    | Compression                                    |  |

|    |      | 2.6.4    | V.42 bis D   | ata Compression                                |  |

|    |      | 2.6.5    | MNP 5 Dat    | ta Compression                                 |  |

|    | 2.7  | Telepho  | ny Extension | S                                              |  |

|    |      | 2.7.1    | •            | e Detection                                    |  |

|    |      | 2.7.2    | Extension    | Pickup Detection                               |  |

|    |      | 2.7.3    |              | angup Detection                                |  |

|    | 2.8  | Fax Clas |              | Class 1.0 Operation                            |  |

|    | 2.9  |          |              | ort                                            |  |

|    | 2.10 |          |              |                                                |  |

|    |      | 2.10.1   |              | ce Command Mode                                |  |

|    |      | 2.10.2   |              | eive Mode                                      |  |

|    |      | 2.10.3   |              | ismit Mode                                     |  |

|    |      | 2.10.4   |              | x Receive and Transmit Mode                    |  |

|    |      | 2.10.5   | •            | le                                             |  |

|    |      | 2.10.6   |              | ctors                                          |  |

|    |      | 2.10.7   |              | ione Mode                                      |  |

|    | 2.11 |          |              | ccess Mode (SAM) - Video Conferencing          |  |

|    | 2.12 | -        |              | phone (FDSP) Mode (S Models)                   |  |

|    | 2.13 |          |              | ()                                             |  |

|    | 2.14 |          |              | Support                                        |  |

|    | 2.15 |          | 5            |                                                |  |

|    |      | 2.15.1   |              | ed Tests                                       |  |

|    |      | 2.15.2   |              | Reset Tests                                    |  |

|    | 2.16 | Low Pov  |              | ode                                            |  |

| 3. |      |          |              |                                                |  |

| 0. |      |          |              |                                                |  |

|    | 3.1  |          |              | Irdware Pins and Signals                       |  |

|    |      | 3.1.1    |              | o Parallel and Serial Interface Configurations |  |

|    |      |          | 3.1.1.1      | LSD Interface (Through DIB)                    |  |

|    |      |          | 3.1.1.2      | Call Progress Speaker Interface                |  |

|    |      |          | 3.1.1.3      | Voice Relay Interface (S Models)               |  |

|    |      |          | 3.1.1.4      | Serial EEPROM Interface                        |  |

|    |      |          | 3.1.1.5      | External Bus Interface                         |  |

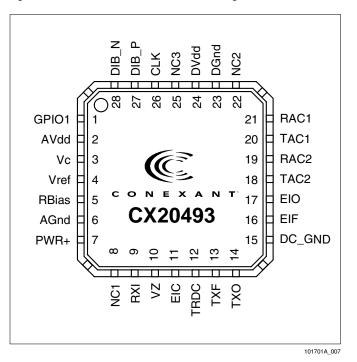

|    |        | 3.1.2      | Serial Inter  | face Configuration Only                                      |     |

|----|--------|------------|---------------|--------------------------------------------------------------|-----|

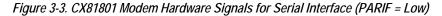

|    |        |            | 3.1.2.1       | Serial DTE Interface and Indicator Outputs (PARIF = Low)     |     |

|    |        | 3.1.3      | Parallel Inte | erface Configuration Only (PARIF = High)                     |     |

|    |        |            | 3.1.3.1       | Parallel Host Bus Interface                                  |     |

|    |        | 3.1.4      | CX81801 N     | Nodem Interface Signals                                      |     |

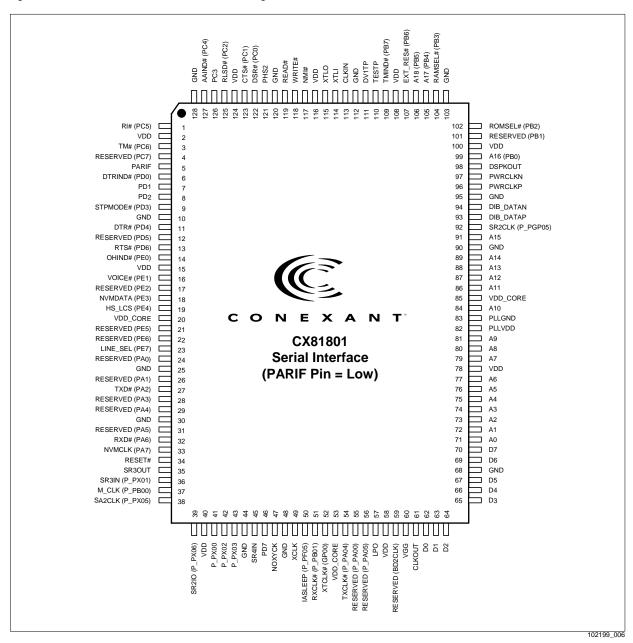

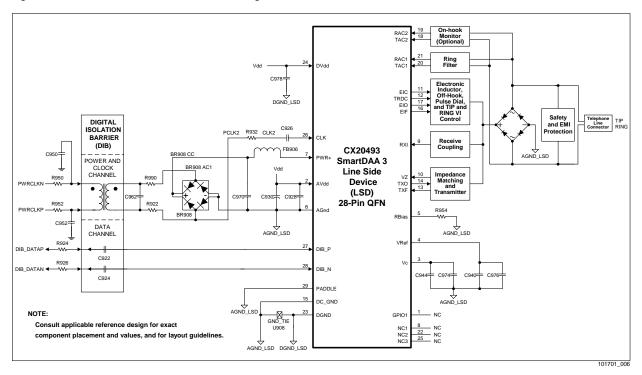

|    | 3.2    | CX20493    | LSD Hardw     | are Pins and Signals                                         |     |

|    |        | 3.2.1      | CX20493 L     | SD Signal Summary                                            |     |

|    |        |            | 3.2.1.1       | Smart Modem Interface (Through DIB)                          |     |

|    |        |            | 3.2.1.2       | Telephone Line Interface                                     |     |

|    |        |            | 3.2.1.3       | Voltage References                                           |     |

|    |        |            | 3.2.1.4       | General Purpose Input/Output                                 |     |

|    |        |            | 3.2.1.5       | No Connects                                                  |     |

|    |        | 3.2.2      | CX20493 L     | SD Pin Assignments and Signal Definitions                    |     |

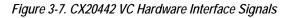

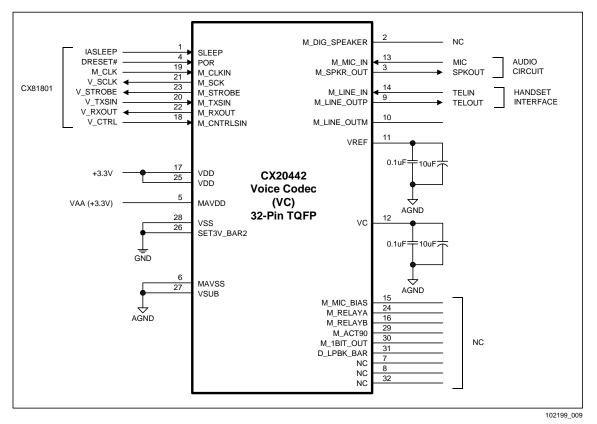

|    | 3.3    | CX20442    | VC Hardwar    | re Pins and Signals (S Models)                               |     |

|    |        | 3.3.1      | CX20442 V     | C Signal Summary                                             |     |

|    |        |            | 3.3.1.1       | Speakerphone Interface                                       |     |

|    |        |            | 3.3.1.2       | Telephone Handset/Headset Interface                          |     |

|    |        |            | 3.3.1.3       | CX81801 Modem Interface                                      |     |

|    |        |            | 3.3.1.4       | Host Interface                                               |     |

|    |        | 3.3.2      | CX20442 V     | C Pin Assignments and Signal Definitions                     |     |

|    | 3.4    | Electrical | and Environ   | nmental Specifications                                       |     |

|    |        | 3.4.1      | Operating (   | Conditions, Absolute Maximum Ratings, and Power Requirements |     |

|    |        | 3.4.2      | Interface ar  | nd Timing Waveforms                                          |     |

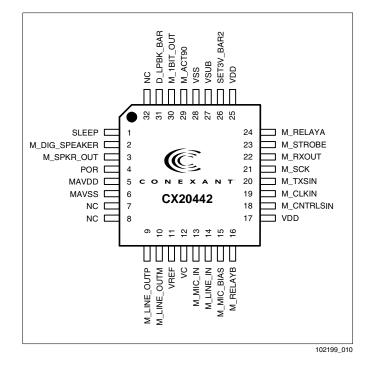

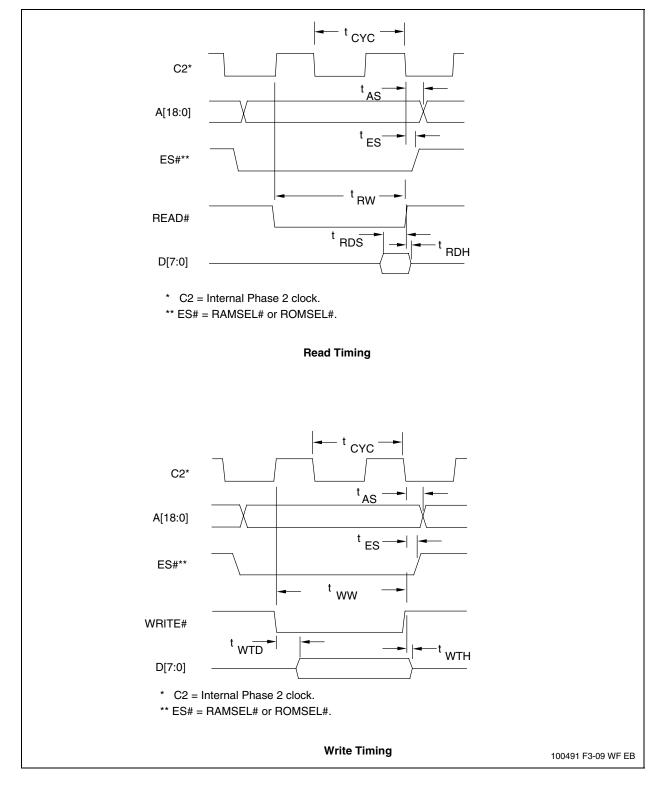

|    |        |            | 3.4.2.1       | External Memory Bus Timing                                   |     |

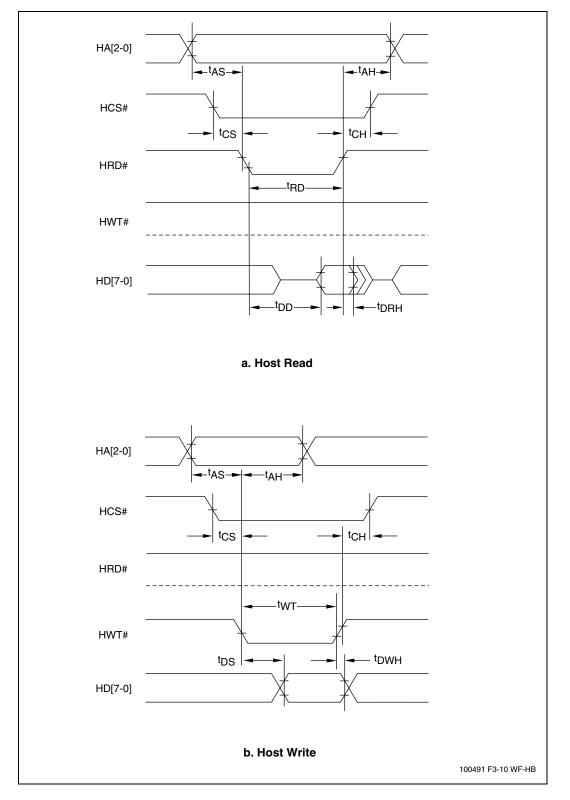

|    |        |            | 3.4.2.2       | Parallel Host Bus Timing                                     |     |

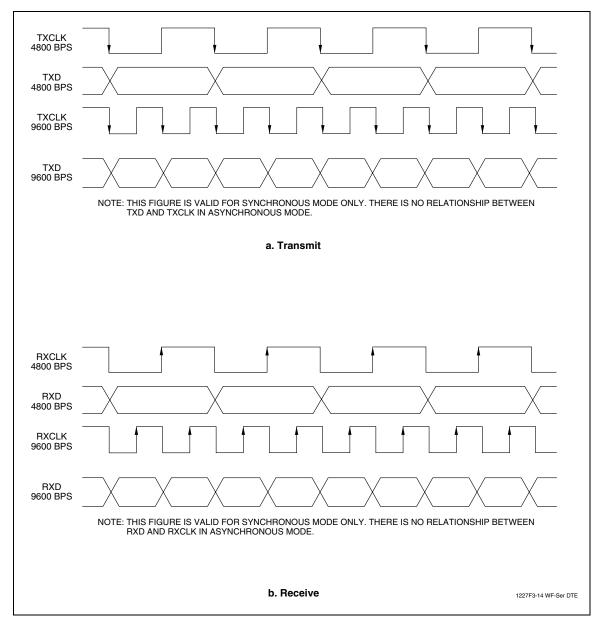

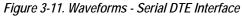

|    |        |            | 3.4.2.3       | Serial DTE Interface                                         |     |

|    | 3.5    | Crystal S  | pecifications | 3                                                            |     |

| 4. | Packa  | age Dime   | ensions       |                                                              | 4-1 |

| 5. | Parall | el Host I  | nterface      |                                                              | 5-1 |

|    | 5.1    | Overview   |               |                                                              |     |

|    | 5.2    | Register   | Signal Defini | itions                                                       |     |

|    |        | 5.2.1      | -             | rupt Enable Register (Addr = 1, DLAB = 0)                    |     |

|    |        | 5.2.2      |               | Control Register (Addr = 2, Write Only)                      |     |

|    |        | 5.2.3      |               | upt Identifier Register (Addr = 2)                           |     |

|    |        | 5.2.4      |               | Control Register (Addr = 3)                                  |     |

|    |        | 5.2.5      |               | dem Control Register (Addr = 4)                              |     |

|    |        | 5.2.6      |               | Status Register (Addr = 5)                                   |     |

|    |        | 5.2.7      |               | dem Status Register (Addr = 6)                               |     |

|    |        | 5.2.8      |               | Buffer (Receiver Buffer Register) (Addr = 0, DLAB = 0)       |     |

|    |        | 5.2.9      |               | Buffer (Transmitter Holding Register) (Addr = 0, DLAB = 0)   |     |

|    |        | 5.2.10     |               | gisters (Addr = 0 and 1, DLAB = 1)                           |     |

|    | 5.3    | Receiver   |               | pt Operation                                                 |     |

|    |        | 5.3.1      |               | ata Available Interrupt                                      |     |

|    |        | 5.3.2      |               | haracter Timeout Interrupts                                  |     |

|    | 5.4    | Transmit   |               | rrupt Operation                                              |     |

|    |        | 5.4.1      |               | r Empty Interrupt                                            |     |

## **Figures**

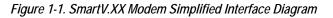

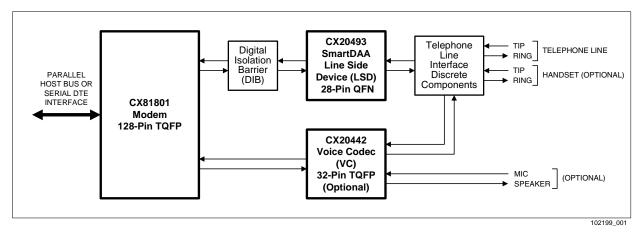

| Figure 1-1. SmartV.XX Modem Simplified Interface Diagram                                 | 1-3  |

|------------------------------------------------------------------------------------------|------|

| Figure 1-2. SmartV.XX Modem Major Interfaces                                             |      |

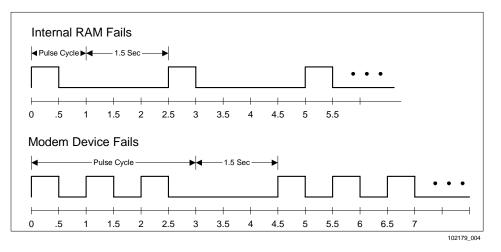

| Figure 2-1. TMIND# Test Results Pulse Cycles                                             |      |

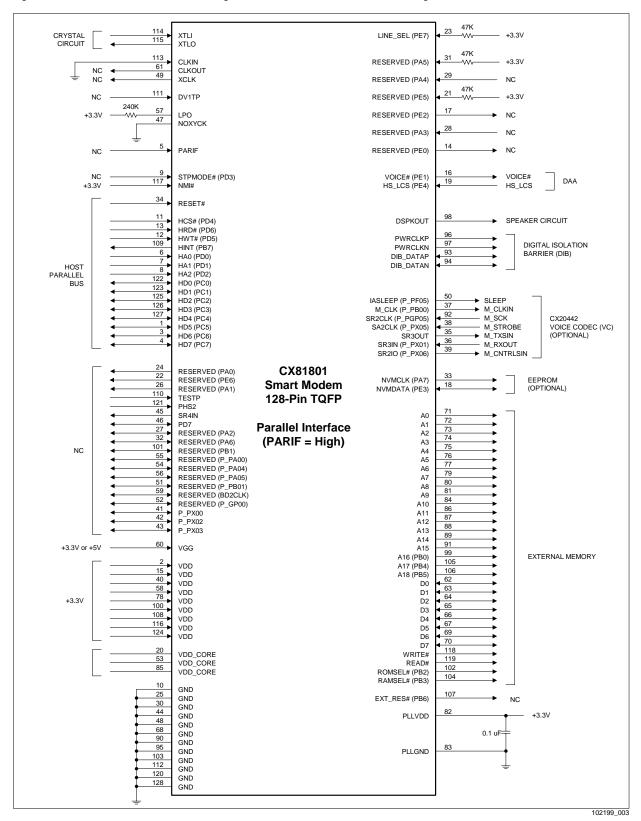

| Figure 3-1. CX81801 Modem Hardware Signals for Parallel Interface (PARIF = High)         | 3-4  |

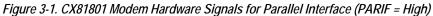

| Figure 3-2. CX81801 Modem 128-Pin TQFP Pin Signals for Parallel Interface (PARIF = High) | 3-5  |

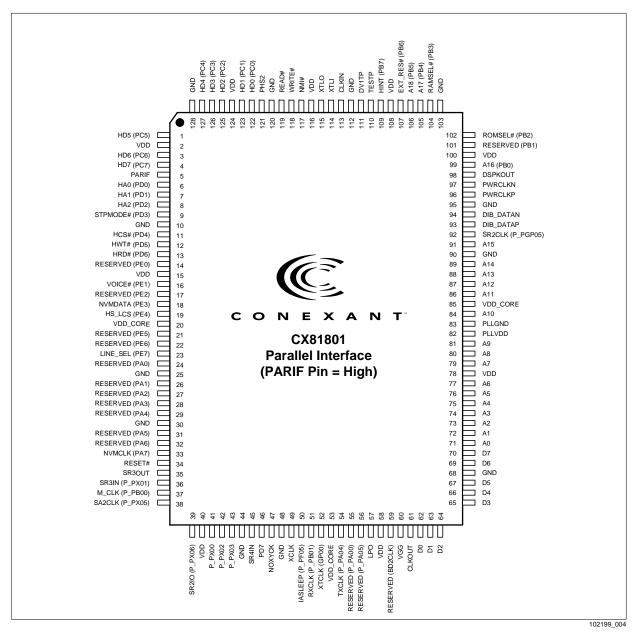

| Figure 3-3. CX81801 Modem Hardware Signals for Serial Interface (PARIF = Low)            |      |

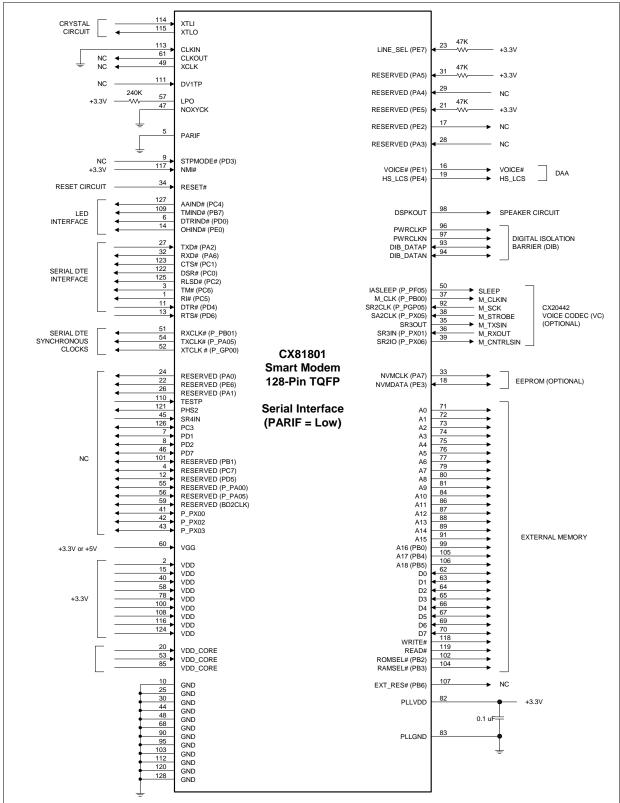

| Figure 3-4. CX81801 Modem 128-Pin TQFP Pin Signals for Serial Interface (PARIF = Low)    | 3-13 |

| Figure 3-5. CX20493 LSD Hardware Interface Signals                                       | 3-23 |

| Figure 3-6. CX20493 LSD 28-Pin QFN Pin Signals                                           | 3-24 |

| Figure 3-7. CX20442 VC Hardware Interface Signals                                        | 3-30 |

| Figure 3-8. CX20442 VC 32-Pin TQFP Pin Signals                                           | 3-30 |

| Figure 3-9. Waveforms - External Memory Bus                                              | 3-38 |

| Figure 3-10. Waveforms - Parallel Host Bus                                               | 3-40 |

| Figure 3-11. Waveforms - Serial DTE Interface                                            | 3-41 |

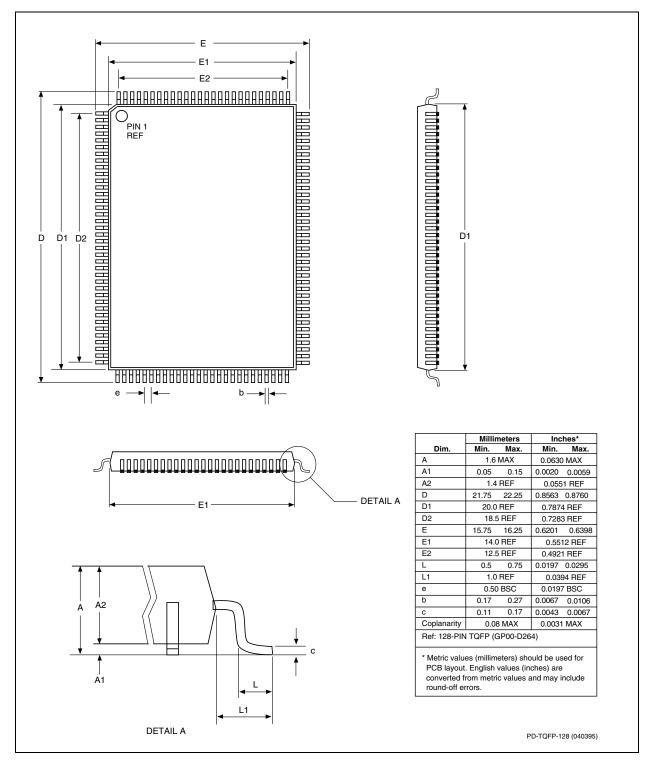

| Figure 4-1. Package Dimensions - 128-Pin TQFP                                            | 4-2  |

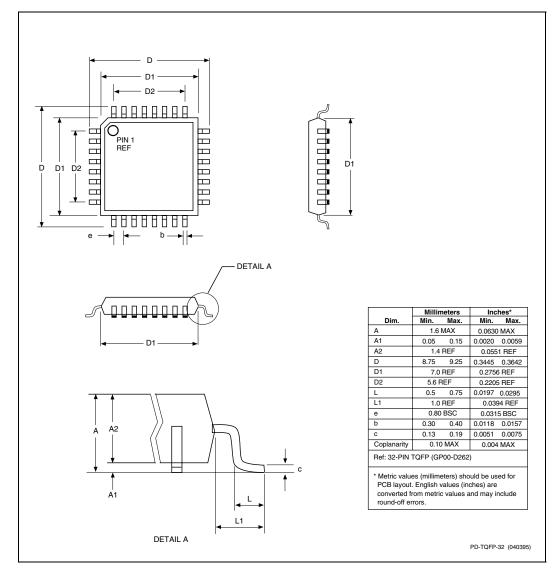

| Figure 4-2. Package Dimensions - 32-pin TQFP                                             | 4-3  |

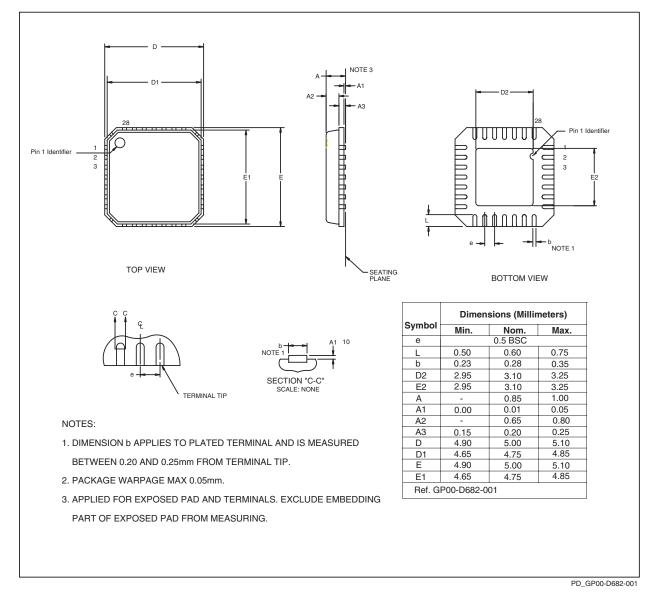

| Figure 4-3. Package Dimensions - 28-Pin QFN                                              | 4-4  |

## **Tables**

| Table 1-1. SmartV.XX Modem Models and Functions                                         | 1-2  |

|-----------------------------------------------------------------------------------------|------|

| Table 1-2. Default Countries Supported                                                  | 1-8  |

| Table 2-1. +MS Command Automode Connectivity                                            | 2-3  |

| Table 3-1. CX81801 Modem 128-Pin TQFP Pin Signals for Parallel Interface (PARIF = High) | 3-6  |

| Table 3-2. CX81801 Modem Pin Signal Definitions for Parallel Interface (PARIF = High)   | 3-8  |

| Table 3-3. CX81801 Modem 128-Pin TQFP Pin Signals for Serial Interface (PARIF = Low)    | 3-14 |

| Table 3-4. CX81801 Modem Pin Signal Definitions for Serial Interface (PARIF = Low)      | 3-16 |

| Table 3-5. CX81801 Modem I/O Type Definitions                                           | 3-21 |

| Table 3-6. CX81801 Modem DC Electrical Characteristics                                  | 3-21 |

| Table 3-7. CX20493 LSD 28-Pin QFN Pin Signals                                           | 3-24 |

| Table 3-8. CX20493 LSD Hardware Signal Definitions                                      | 3-25 |

| Table 3-9. CX20493 LSD GPIO DC Electrical Characteristics                               | 3-27 |

| Table 3-10. CX20493 AVdd DC Electrical Characteristics                                  | 3-27 |

| Table 3-11. CX20442 VC 32-Pin TQFP Pin Signals                                          | 3-31 |

| Table 3-12. CX20442 VC Pin Signal Definitions                                           | 3-32 |

| Table 3-13. CX20442 VC DC Electrical Characteristics                                    |      |

| Table 3-14. CX20442 VC Analog Electrical Characteristics                                |      |

| Table 3-15. Operating Conditions                                                        | 3-35 |

| Table 3-16. CX81801 Absolute Maximum Ratings                                            | 3-35 |

| Table 3-17. CX20493 Absolute Maximum Ratings                                            | 3-35 |

| Table 3-18. CX20442 Absolute Maximum Ratings                                            | 3-36 |

| Table 3-19. Current and Power Requirements                                              | 3-36 |

| Table 3-20. Timing - External Memory Bus                                                | 3-37 |

| Table 3-21. Timing - Parallel Host Bus                                                  |      |

| Table 3-22. Crystal Specifications                                                      |      |

| Table 5-1. Parallel Interface Registers                                                 | 5-2  |

| Table 5-2. Interrupt Sources and Reset Control                                          |      |

| Table 5-3. Programmable Baud Rates                                                      | 5-10 |

## 1. Introduction

#### 1.1 Overview

The Conexant® SmartV.XX Modem is a full-featured, worldwide, controller-based modem that integrates modem controller (MCU), modem data pump (MDP), 256 KB ROM, 32 KB RAM, and SmartDAA system side device (SSD) functions onto a single die.

The modem operates by executing firmware from internal ROM and RAM. Optional customized firmware is supported with optional external flash ROM memory. Additionally, added/modified country profiles are supported by internal SRAM patch (maximum of one profile) or serial EEPROM. Downloadable architecture supports downloading of customized MCU firmware from the host/DTE to the SmartV.XX modem.

The SmartV.XX Modem device set consists of a CX81801 modem device in a 128-pin TQFP and a CX20493 SmartDAA Line Side Device (LSD) in a 28-pin QFN.

Conexant's SmartDAA® technology eliminates the need for a costly analog transformer, relays and opto-isolations typically used in discrete DAA (Data Access Arrangement) implementations. The SmartDAA architecture also simplifies product implementation by eliminating the need for country-specific board configurations enabling worldwide homologation of a single modem board design and a single bill of materials (BOM).

Low profile, small TQFP and QFN packages with reduced voltage operation and low power consumption makes this device set an ideal solution for embedded and palmtop application using parallel host or serial DTE interface.

The SmartV.XX Modem supports data rates up to V.92, data compression, error correction, fax rates up to 14.4 kbps and speakerphone mode.

In V.92 and V.90 (V.92 models) data modes, the modem can receive data at speeds up to 56 kbps. In V.34 data mode (V.92 and V.34 models), the modem can receive data at speeds up to 33.6 kbps. In V.32 bis data mode, the modem can receive data at speeds up to 14.4 kbps.

Data compress (V.44/V.42bis/MNP5) and error correction (V.42/MNP 2-4) modes are supported to maximize data throughput and data transfer integrity. Non-error-correction mode is also supported.

Fax Group 3 send and receive rates are supported up to 14.4 kbps with T.30 protocol.

The SmartV.XX modem operates with PSTN telephone lines worldwide.

S models, using the optional CX20442 Voice Codec (VC) in a 32-pin TQFP, support position independent, full-duplex speakerphone (FDSP) operation using microphone and speaker, as well as other voice/TAM applications using handset or headset.

Table 1-1 lists the available models. A simplified device interface drawing is shown in Figure 1-1. A functional interface drawing showing optional memory is shown in Figure 1-2.

## 1.2 Applications

- Set top boxes

- Gaming devices

- Point of sale terminals

- Remote monitoring and data collections systems

- Handheld computers

- Other embedded systems

Table 1-1. SmartV.XX Modem Models and Functions

| Model/Order/Part Numbers |                         |                                            |                                                       |                                                  |                       | Supported Functions |                                                                            |                |

|--------------------------|-------------------------|--------------------------------------------|-------------------------------------------------------|--------------------------------------------------|-----------------------|---------------------|----------------------------------------------------------------------------|----------------|

| Marketing Name           | Device Set Order<br>No. | Modem Device<br>[128-Pin TQFP]<br>Part No. | Line Side<br>Device (LSD)<br>[28-Pin QFN]<br>Part No. | Voice Codec<br>(VC)<br>[32-Pin TQFP]<br>Part No. | V.90 Data,<br>QC, MOH | V.34 Data           | V.32 bis Data,<br>V.44 Data<br>Compression,<br>V.17 Fax, TAM,<br>Worldwide | Voice/<br>FDSP |

| SmartV.92                | DS56-L147-203           | CX81801-74                                 | CX20493-21                                            | —                                                | Y                     | Y                   | Y                                                                          | _              |

| SmartV.92/S              | DS56-L147-204           | CX81801-74                                 | CX20493-21                                            | CX20442-11                                       | Y                     | Y                   | Y                                                                          | Y              |

| SmartV.92/LF             | DS56-L147-206           | CX81801-84                                 | CX20493-31                                            | —                                                | Y                     | Y                   | Y                                                                          | _              |

| SmartV.34                | DS28-L147-203           | CX81801-72                                 | CX20493-21                                            | —                                                | _                     | Y                   | Y                                                                          | _              |

| SmartV.34/S              | DS28-L147-204           | CX81801-72                                 | CX20493-21                                            | CX20442-11                                       | _                     | Y                   | Y                                                                          | Y              |

| SmartV.34/LF             | DS28-L147-206           | CX81801-82                                 | CX20493-31                                            | —                                                | _                     | Y                   | Y                                                                          | _              |

| SmartV.32bis             | DS96-L147-203           | CX81801-73                                 | CX20493-21                                            |                                                  | _                     | _                   | Y                                                                          | _              |

| SmartV.32bis/S           | DS96-L147-204           | CX81801-73                                 | CX20493-21                                            | CX20442-11                                       | —                     | _                   | Y                                                                          | Y              |

| SmartV.32bis/LF          | DS96-L147-206           | CX81801-83                                 | CX20493-31                                            | _                                                | _                     | _                   | Y                                                                          | _              |

Notes:

1. Supported functions (Y = Supported; — = Not supported).

QC, MOH, PCM Quick connect, Modem-on-Hold, PCM upstream

TAM Telephone answering machine (Voice playback and record through telephone line)

FDSP Full-duplex speakerphone and voice playback and record through telephone line, handset, and mic/speaker

2. For ordering purposes, the CX prefix may not be included in the part number for some devices. Also, the CX prefix may not appear in the part number as branded on some devices.

3. LF = Lead-free (Pb-free) devices.

Figure 1-2. SmartV.XX Modem Major Interfaces

102199\_002

## **1.3 Features**

#### 1.3.1 General Modem Features

- Data modem

- Quick connect, Modem-on-Hold, and PCM upstream functions (V.92 models)

- ITU-T V.92/V.90 (V.92 models), V.34 (V.92 and V.34 models), V.32bis, V.32,

V.29, FastPOS (V.29), V.22 bis, V.22, V.22 Fast Connect, V.23, V.21,

- Bell 212A, and Bell 103

- V.250 and V.251 commands

- Data compression and error correction

- V.44 data compression

- V.42 bis and MNP 5 data compression

- V.42 LAPM and MNP 2-4 error correction

- Fax modem send and receive rates up to 14.4 kbps

- V.17, V.29, V.27 ter, and V.21 channel 2

- EIA/TIA 578 Class 1 and T.31 Class 1.0

- V.80 synchronous access mode supports host-controlled communication protocols with H.324 interface support

- Interfaces to optional external ROM/flash ROM, RAM, and/or optional serial EEPROM

- Data/Fax/Voice call discrimination

- Hardware-based modem controller

- Hardware-based digital signal processor (DSP)

- Worldwide operation

- Complies to TBR21 and other country requirements

- On-hook and/or off-hook Caller ID detection for selected countries

- Call progress, blacklisting

- Internal ROM includes default values for 29 countries

- Additional and modified country profile can be stored in internal SRAM

- Caller waiting detection

- Caller ID detect

- On-hook Caller ID detection

- Off-hook Call Waiting Caller ID detection during data mode in V.92, V.90, V.34, V.32bis, and V.32

- Distinctive ring detect

- Modem customization available through patch code that can be stored in optional serial EEPROM or internal SRAM

- Telephony/TAM

- V.253 commands

- 2-bit and 4-bit Conexant ADPCM, 8-bit linear PCM, and 4-bit IMA coding

- 8 kHz sample rate

- Concurrent DTMF, ring, and Caller ID detection

- Full-duplex speakerphone (FDSP) mode using optional CX20442 Voice Codec (S models)

- Microphone and speaker interface

- Telephone handset or headset interface

- Acoustic and line echo cancellation

- Microphone gain and muting

- Speaker volume control and muting

- Built-in host/DTE interface

- Parallel 16550A UART-compatible interface up to 230.4 kbps

- Serial ITU-T V.24 (EIA/TIA-232-E) logical interface up to 115.2 kbps

- Downloadable architecture

- Direct mode (serial DTE interface)

- Flow control and speed buffering

- Automatic format/speed sensing

- Serial async/sync data; parallel async data

- Thin packages support low profile designs (1.6 mm max. height)

- CX81801 Modem device in 128-pin TQFP

- CX20493 LSD in 28-pin QFN

- CX20442 VC in 32-pin TQFP

- +3.3V operation with +5V tolerant digital inputs

- Typical power use

- CX81801 and CX20493: 209 mW (Normal Mode); 59 mW (Sleep Mode)

- CX20442: 5 mW (Normal Mode)

#### **1.3.2 SmartDAA Features**

- System side powered DAA operates under poor line current supply conditions

- Modem Wake-on-Ring

- Ring detection

- Line current loss detection

- Pulse dialing

- Line-in-use detection during on-hook operation

- Remote hang-up detection for efficient call termination

- Extension pickup detection

- Digital PBX line protection

- Meets worldwide DC Voltage/Current (VI) masks requirements

#### 1.3.3 Applications

- Set top boxes

- Gaming devices

- Point of sale terminals

- Remote monitoring and data collections systems

- Handheld computers

- Other embedded systems

## 1.4 Technical Overview

#### 1.4.1 General Description

Modem operation, including dialing, call progress, telephone line interface, telephone handset interface, optional voice/speakerphone interface, and host interface functions are supported and controlled through the V.250, V.251, and V.253-compatible command set.

The modem hardware connects to the host via a parallel or serial interface as selected by the PARIF input. The OEM adds a crystal circuit, DIB components, telephone line interface, telephone handset/telephony extension interface, voice/speakerphone interface, optional external serial EEPROM, optional external ROM/flash ROM, optional external RAM, and other supporting discrete components as supported by the modem model (Table 1-1) and required by the application to complete the system.

Customized modem firmware can be supported by the use of external memory in various combinations, e.g., either external ROM/flash ROM (up to 256 KB), or external serial EEPROM (256 to 32 KB) and external RAM (up to 128 KB). To support country profile addition or modification, external serial EEPROM (256 to 32 KB) can be installed. Customized code can include OEM-defined commands, i.e., identification codes (I3), identifier string (I4), manufacturer identification (+GMI), model identification (+GMM), and revision identification (+GMR), as well as code modification.

Parallel interface operation is selected by PARIF input high.

Serial interface operation is selected by PARIF input low.

#### 1.4.2 MCU Firmware

MCU firmware performs processing of general modem control, command sets, data modem, error correction and data compression (ECC), fax class 1, fax class 1.0, voice/audio/TAM/speakerphone, worldwide, V.80, and serial DTE/parallel host interface functions according to modem models (Table 1-1).

MCU firmware can be customized to include OEM-defined commands, i.e., identification codes (I3), identifier string (I4), manufacturer identification (+GMI), model identification (+GMM), and revision identification (+GMR), as well as code modification.

The modem firmware is provided in object code form for the OEM to program into external ROM/flash ROM. The modem firmware may also be provided in source code form under a source code addendum license agreement. External ROM/Flash ROM and RAM must be installed in order to operate the modem with customized firmware.

#### **1.4.3 Operating Modes**

#### 1.4.3.1 Data/Fax Modes

Data modem modes perform complete handshake and data rate negotiations. Using modem modulations to optimize modem configuration for line conditions, the modem can connect at the highest data rate that the channel can support from 56 kbps down to 2400 bps with automatic fallback.

In V.92/V.90 data modem modes (V.92 models), the modem can receive data from a digital source using a V.92-compatible central site modem at line speeds up to 56 kbps. With PCM upstream enabled (V.92 only), data transmission supports sending data at line

speeds up to 48 kbps. When PCM upstream is disabled, data transmission supports sending data at line speeds up to V.34 rates. This mode can fallback to V.34 mode and to lower rates as dictated by line conditions.

The following modes are supported in V.92 models when connected to a V.92-compatible server supporting the feature listed.

- Quick connect: Allows quicker subsequent connections to a server by using stored line parameters obtained during the initial connection.

- Modem-on-Hold: Allows detection and reporting of incoming phone calls on the PSTN with enabled Call Waiting. If the incoming call is accepted by the user, the user has a pre-defined amount of time of holding the data connection for a brief conversation. The data connection resumes upon incoming call termination.

- PCM upstream: Boosts the upstream data rates. A maximum of 48 kbps is supported when connected to a V.92 server that supports PCM upstream.

In V.34 data modem mode (V.92 and V.34 models), the modem can operate in fullduplex, asynchronous modes at line rates up to 33.6 kbps. Automode operation in V.34 is provided in accordance with PN3320 and in V.32 bis in accordance with PN2330. All tone and pattern detection functions required by the applicable ITU or Bell standards are supported.

In V.32 bis data modem mode, the modem can operate at line speeds up to 14.4 kbps.

In fax modem mode, the modem can operate in half-duplex, synchronous modes and can support Group 3 facsimile send and receive speeds of 14400, 12000, 9600, 7200, 4800, and 2400 bps. Fax data transmission and reception performed by the modem are controlled and monitored through the EIA/TIA-578 Fax Class 1, or T.31 Fax Class 1.0 command interface. Full HDLC formatting, zero insertion/deletion, and CRC generation/checking are provided.

#### 1.4.3.2 V.44 Data Compression

V.44 provides efficient data compression that minimizes the download time for the types of files associated with Internet use. This improvement is most noticeable when browsing and searching the web since HTML text files are highly compressible. (The improved performance amount varies both with the actual format and with the content of individual pages and files.)

#### 1.4.3.3 Worldwide Operation

SmartDAA technology allows a single PCB design and single BOM to be homologated worldwide. Advanced features such as extension pickup detection, remote hang-up detection, line-in-use detection, and digital PBX detection are supported.

Country-dependent modem parameters for functions such as dialing, carrier transmit level, calling tone, call progress tone detection, answer tone detection, blacklisting, caller ID, and relay control are programmable.

Country code IDs are defined by ITU-T T.35.

Embedded ROM code includes default profiles for 29 countries. Additional country profiles can be stored in internal SRAM or external serial EEPROM (request additional country profiles from a Conexant Sales Office). Duplicate country profiles stored in internal SRAM or external serial EEPROM will override the profiles in embedded ROM code. The default countries supported are listed in Table 1-2. Country profiles for CTR-21 countries are TBR-21 compliant.

| Country        | Country<br>Code | Call Waiting Tone<br>Detection (CW)<br>Supported | On-Hook Type 1<br>Caller ID (CID)<br>Supported | Off-Hook Type 2<br>Called ID (CID2)<br>Supported |

|----------------|-----------------|--------------------------------------------------|------------------------------------------------|--------------------------------------------------|

| Australia      | 09              | Х                                                | Х                                              |                                                  |

| Austria        | 0A              | Х                                                | Х                                              |                                                  |

| Belgium        | 0F              | Х                                                |                                                |                                                  |

| Brazil         | 16              | Х                                                |                                                |                                                  |

| China          | 26              | Х                                                | Х                                              |                                                  |

| Denmark        | 31              | Х                                                | Х                                              |                                                  |

| Finland        | 3C              | Х                                                | Х                                              |                                                  |

| France         | 3D              | Х                                                | Х                                              | Х                                                |

| Germany        | 42              | Х                                                | Х                                              |                                                  |

| Hong Kong      | 50              | Х                                                | Х                                              | Х                                                |

| India          | 53              |                                                  | Х                                              |                                                  |

| Ireland        | 57              |                                                  | Х                                              |                                                  |

| Italy          | 59              | Х                                                | Х                                              |                                                  |

| Japan          | 00              | Х                                                | Х                                              | Х                                                |

| Korea          | 61              | Х                                                |                                                |                                                  |

| Malaysia       | 6C              | Х                                                |                                                |                                                  |

| Mexico         | 73              |                                                  |                                                |                                                  |

| Netherlands    | 7B              |                                                  | Х                                              |                                                  |

| Norway         | 82              | Х                                                | Х                                              |                                                  |

| Poland         | 8A              | Х                                                |                                                |                                                  |

| Portugal       | 8B              | Х                                                |                                                |                                                  |

| Singapore      | 9C              | Х                                                | Х                                              | Х                                                |

| South Africa   | 9F              | Х                                                |                                                |                                                  |

| Spain          | A0              | Х                                                | Х                                              |                                                  |

| Sweden         | A5              | Х                                                | Х                                              |                                                  |

| Switzerland    | A6              | Х                                                |                                                |                                                  |

| Taiwan         | FE              | Х                                                | Х                                              |                                                  |

| United Kingdom | B4              | Х                                                | Х                                              | Х                                                |

| United States  | B5              | Х                                                | Х                                              | Х                                                |

| Reserved       | FD              | Х                                                | Х                                              | Х                                                |

#### Table 1-2. Default Countries Supported

#### 1.4.3.4 TAM Mode

TAM Mode features include 8-bit linear coding at 8 kHz sample rate. Tone detection/ generation, call discrimination, and concurrent DTMF detection are also supported.

TAM Mode is supported by four submodes:

- Online Voice Command Mode supports connection to the telephone line or, for S models, a microphone/speaker/handset/headset.

- Voice Receive Mode supports recording voice or audio data input from the telephone line or, for S models, a microphone/handset/headset.

- Voice Transmit Mode supports playback of voice or audio data to the telephone line or, for S models, a speaker/handset/headset.

- Full-duplex Receive and Transmit Mode.

#### 1.4.3.5 Speakerphone Mode (S Models)

S models include additional telephone handset, external microphone, and external speaker interfaces which support voice and full-duplex speakerphone (FDSP) operation.

Hands-free full-duplex telephone operation is supported in Speakerphone Mode under host control. Speakerphone Mode features an advanced proprietary speakerphone algorithm which supports full-duplex voice conversation with acoustic, line, and handset echo cancellation. Parameters are constantly adjusted to maintain stability with automatic fallback from full-duplex to pseudo-duplex operation. The speakerphone algorithm allows position independent placement of microphone and speaker. The host can separately control volume, muting, and AGC in microphone and speaker channels.

#### **1.4.4 Reference Designs**

A data/fax/TAM/speakerphone reference design for external modems is available to minimize application design time, reduce development cost, and accelerate market entry. This designs is:

• For CX81801 and CX20493: RD01-D660-1xx

A design package is available in electronic form. This package includes schematics, bill of materials (BOM), vendor part list (VPL), board layout files in Gerber format, and complete documentation.

### **1.5 Hardware Description**

SmartDAA technology eliminates the need for a costly analog transformer, relays, and opto-isolators that are typically used in discrete DAA implementations. The programmable SmartDAA architecture simplifies product implementation in worldwide markets by eliminating the need for country-specific components.

#### 1.5.1 CX81801 Modem Device

The CX81801 Modem, packaged in a 128-pin TQFP, includes a Microcontroller (MCU), a Modem Data Pump (MDP), 256 KB internal ROM, 32 KB internal RAM, and SmartDAA interface functions.

The CX81801 Modem connects to host via a parallel host (PARIF = high) or a logical V.24 (EIA/TIA-232-E) serial DTE interface (PARIF = low).

The CX81801 Modem performs the command processing and host interface functions. The crystal frequency is 28.224 MHz  $\pm$  50 ppm.

The CX81801 Modem optionally connects to an external OEM-supplied serial EEPROM over a dedicated 2-line serial interface. The capacity of the EEPROM can be 256 bytes up to 32 KB. The EEPROM can hold information such as firmware configuration customization, and country code parameters.

The CX81801 Modem performs telephone line signal modulation/demodulation in a hardware digital signal processor (DSP) which reduces computational load on the host processor.

The SmartDAA interface communicates with, and supplies power and clock to, the LSD through the DIB.

The CX81801 optionally connects to external OEM-supplied ROM/flash ROM and RAM over a non-multiplexed 19-bit address bus and 8-bit data bus.

#### **1.5.2 Digital Isolation Barrier**

The OEM-supplied Digital Isolation Barrier (DIB) electrically DC isolates the CX81801 from the LSD and telephone line. The modem is connected to a fixed digital ground and operates with standard CMOS logic levels. The LSD is connected to a floating ground and can tolerate high voltage input (compatible with telephone line and typical surge requirements).

The DIB transformer couples power and clock from the CX81801 to the LSD.

The DIB data channel supports bidirectional half-duplex serial transfer of data, control, and status information between the CX81801 and the LSD over two lines.

#### 1.5.3 CX20493 SmartDAA Line Side Device

The CX20493 SmartDAA Line Side Device (LSD) includes a Line Side DIB Interface (LSDI), a coder/decoder (codec), and a Telephone Line Interface (TLI).

The LSDI communicates with, and receives power and clock from, the SmartDAA interface in the CX81801 through the DIB.

LSD power is received from the MDP PWRCLKP and PWRCLKN pins via the DIB through a full-wave rectified bridge and capacitive power filter circuit connected to the DIB transformer secondary winding.

The CLK input is also accepted from the DIB transformer secondary winding through a capacitor and a resistor in series.

Information is transferred between the LSD and the CX81801 through the DIB\_P and DIB\_N pins. These pins connect to the CX81801 DIB\_DATAP and DIB\_DATAN pins, respectively, through the DIB.

The TLI integrates DAA and direct telephone line interface functions and connects directly to the line TIP and RING pins, as well as to external line protection components.

Direct LSD connection to TIP and RING allows real-time measurement of telephone line parameters, such as the telephone central office (CO) battery voltage, individual telephone line (copper wire) resistance, and allows dynamic regulation of the off-hook TIP and RING voltage and total current drawn from the central office (CO). This allows the modem to maintain compliance with U.S. and worldwide regulations and to actively control the DAA power dissipation.

#### 1.5.4 CX20442 Voice Codec

The optional CX20442 Voice Codec (VC), packaged in a 32-pin TQFP, supports voice/full-duplex speakerphone (FDSP) operation with interfaces to a microphone and speaker and to a telephone handset/headset.

### **1.6 AT Commands**

The SmartV.XX Modem supports AT commands for data mode, fax class 1 or 1.0, voice/audio, full-duplex speakerphone (FDSP), V.80 commands, and S Register. See Doc. No. 102184 for a description of the commands.

**Data Mode Operation.** Data functions operate in response to the AT commands when +FCLASS=0. Default parameters support U.S./Canada operation.

**Fax Mode Operation.** Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or to fax class 1.0 commands when +FCLASS=1.0.

**Voice/Audio Operation.** Voice/audio functions operate in response to voice/audio commands when +FCLASS=8.

**Speakerphone Operation.** FDSP functions operate in response to speakerphone commands when +FCLASS=8 and +VSP=1 is selected.

This page is intentionally blank.

## 2. Technical Specifications

## 2.1 Serial DTE Interface Operation

#### 2.1.1 Automatic Speed/Format Sensing

**Command Mode and Data Mode.** The modem can automatically determine the speed and format of the data sent from the DTE. The modem can sense speeds of 300, 600, 1200, 2400, 4800, 7200, 9600, 12000, 14400, 16800, 19200, 21600, 24000, 26400, 28800, 38400, 57600, and 115200 bps and the following data formats:

| Parity                                                                                                                           | Data Length<br>(No. of Bits) | No. of<br>Stop Bits | Character Length<br>(No. of Bits) |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|-----------------------------------|--|--|

| None                                                                                                                             | 7                            | 2                   | 10                                |  |  |

| Odd                                                                                                                              | 7                            | 1                   | 10                                |  |  |

| Even                                                                                                                             | 7                            | 1                   | 10                                |  |  |

| None                                                                                                                             | 8                            | 1                   | 10                                |  |  |

| Odd                                                                                                                              | 8                            | 1                   | 11*                               |  |  |

| Even                                                                                                                             | 8                            | 1                   | 11*                               |  |  |

| *11-bit characters are sensed, but the parity bit is stripped off during data transmission in Normal and Error Correction modes. |                              |                     |                                   |  |  |

The modem can speed sense data with mark or space parity and configures itself as follows:

| DTE Configuration | Modem Configuration |

|-------------------|---------------------|

| 7 mark            | 7 none              |

| 7 space           | 8 none              |

| 8 mark            | 8 none              |

| 8 space           | 8 even              |

Fax Mode. In V.17 fax mode, the modem can sense speeds up to 115.2 kbps.

## 2.2 Parallel Host Bus Interface Operation

**Command Mode and Data Mode.** The modem can operate at rates up to 230.4 kbps by programming the Divisor Latch in the parallel interface registers if supported by communications software and/or driver.

**Fax Mode.** In V.17 mode, the modem can operate at rates up to 230.4 kbps by programming the Divisor Latch in the parallel interface registers if supported by communications software and/or driver.

## 2.3 Establishing Data Modem Connections

#### 2.3.1 Dialing

**DTMF Dialing.** DTMF dialing using DTMF tone pairs is supported in accordance with ITU-T Q.23. The transmit tone level complies with Bell Publication 47001.

Pulse Dialing. Pulse dialing is supported in accordance with EIA/TIA-496-A.

**Blind Dialing.** The modem can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

#### 2.3.2 Telephone Number Directory

The modem supports four telephone number entries in a directory that can be saved in a serial EEPROM. Each telephone number can be up to 32 characters (including the command line terminating carriage return) in length. A telephone number can be saved using the &Zn=x command, and a saved telephone number can be dialed using the DS=n command.

#### 2.3.3 Modem Handshaking Protocol

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

#### 2.3.4 Call Progress Tone Detection

Ringback, equipment busy, congested tone, warble tone, and progress tones can be detected in accordance with the applicable standard.

#### 2.3.5 Answer Tone Detection

Answer tone can be detected over the frequency range of  $2100 \pm 40$  Hz in ITU-T modes and  $2225 \pm 40$  Hz in Bell modes.

#### 2.3.6 Ring Detection

A ring signal can be detected from a TTL-compatible 15.3 Hz to 68 Hz square wave input.

#### 2.3.7 Billing Protection

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for 2 seconds (data modem) or 4 seconds (fax adaptive answer) to allow transmission of the billing tone signal.

#### 2.3.8 Connection Speeds

The modem functions as a data modem when the +FCLASS=0 command is active.

Line connection can be selected using the +MS command. The +MS command selects modulation, enables/disables automode, and selects minimum and maximum line speeds (Table 2-1).

#### 2.3.9 Automode

Automode detection can be enabled by the +MS command to allow the modem to connect to a remote modem in accordance with draft PN-3320 for V.34 (Table 2-1).

| Modulation      | <carrier></carrier> | Possible ( <min_rx_rate>, <min_rx_rate>, (<min_tx_rate>),<br/>and <max_tx_rate>) Rates (bps)</max_tx_rate></min_tx_rate></min_rx_rate></min_rx_rate>     |

|-----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bell 103        | B103                | 300                                                                                                                                                      |

| Bell 212        | B212                | 1200 Rx/75 Tx or 75 Rx/1200 Tx                                                                                                                           |

| V.21            | V21                 | 300                                                                                                                                                      |

| V.22            | V22                 | 1200                                                                                                                                                     |

| V.22 bis        | V22B                | 2400 or 1200                                                                                                                                             |

| V.23            | V23C                | 1200                                                                                                                                                     |

| V.32            | V32                 | 9600 or 4800                                                                                                                                             |

| V.32 bis        | V32B                | 14400, 12000, 9600, 7200, or 4800                                                                                                                        |

| V.34            | V34                 | 33600, 31200, 28800, 26400, 24000, 21600, 19200, 16800, 14400, 12000, 9600, 7200, 4800, or 2400                                                          |

| V.90            | V90                 | 56000, 54667, 53333, 52000, 50667, 49333, 48000, 46667, 45333, 44000, 42667, 41333, 40000, 38667, 37333, 36000, 34667, 33333, 32000, 30667, 29333, 28000 |

| V.92 downstream | V92                 | 56000, 54667, 53333, 52000, 50667, 49333, 48000, 46667, 45333, 44000, 42667, 41333, 40000, 38667, 37333, 36000, 34667, 33333, 32000, 30667, 29333, 28000 |

| V.92 upstream   | V92                 | 48000, 46667, 45333, 44000, 42667, 41333, 40000, 38667, 37333, 36000, 34667, 33333, 32000, 30667, 29333, 28000, 26667, 25333, 24000                      |

Table 2-1. +MS Command Automode Connectivity

## 2.4 Data Mode

The modem enters data mode when a telephone line connection has been established between modems and all handshaking has been completed.

#### 2.4.1 Speed Buffering (Normal Mode)

Speed buffering allows a DTE to send data to, and receive data from, a modem at a speed different than the line speed. The modem supports speed buffering at all line speeds.

#### 2.4.2 Flow Control

**DTE-to-Modem Flow Control.** If the modem-to-line speed is less than the DTE-to-modem speed, the modem supports XOFF/XON or RTS/CTS flow control with the DTE to ensure data integrity.

#### 2.4.3 Escape Sequence Detection

The +++ escape sequence can be used to return control to the command mode from the data mode. Escape sequence detection is disabled by an S2 Register value greater than 127.

#### 2.4.4 BREAK Detection

The modem can detect a BREAK signal from either the DTE or the remote modem. The \Kn command determines the modem response to a received BREAK signal.

#### 2.4.5 Telephone Line Monitoring

GSTN Cleardown (V.90, V.34, V.32 bis, V.32). Upon receiving GSTN Cleardown from the remote modem in a non-error correcting mode, the modem cleanly terminates the call.

**Loss of Carrier (V.22 bis and Below).** If carrier is lost for a time greater than specified by the S10 register, the modem disconnects.

#### 2.4.6 Fall Forward/Fallback (V.92/V.90/V.34/V.32 bis/V.32)

During initial handshake, the modem will fallback to the optimal line connection within V.92/V.90/V.34/V.32 bis/V.32 mode depending upon signal quality if automode is enabled by the +MS or N1 command.

When connected in V.92/V.90/V.34/V.32 bis/V.32 mode, the modem will fall forward or fallback to the optimal line speed within the current modulation depending upon signal quality if fall forward/fallback is enabled by the %E2 command.

#### 2.4.7 Retrain

The modem may lose synchronization with the received line signal under poor or changing line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to retrain until an acceptable connection is achieved, or until 30 seconds elapse resulting in line disconnect.

#### 2.4.8 Programmable Inactivity Timer

The modem disconnects from the line if data is not sent or received for a specified length of time. In normal or error-correction mode, this inactivity timer is reset when data is received from either the DTE or from the line. This timer can be set to a value between 0 and 255 seconds by using register S30. A value of 0 disables the inactivity timer.

#### 2.4.9 DTE Signal Monitoring (Serial DTE Interface Only)

**DTR#.** When DTR# is asserted, the modem responds in accordance with the &Dn and &Qn commands.

**RTS#.** RTS# is used for flow control if enabled by the &K command in normal or errorcorrection mode.

### 2.5 V.92 Features

Modem-on-Hold, quick connect, and PCM upstream are only available in V.92 models when connecting in V.92 data mode. V.92 features are only available when the server called is a V.92 server that supports that particular feature.

#### 2.5.1 Modem-on-Hold

The Modem-on-Hold (MOH) function enables the modem to place a data call to the Internet on hold while using the same line to accept an incoming or place an outgoing voice call. This feature is available only with a connection to a server supporting MOH. MOH can be executed through either of two methods:

- One method is to enable MOH through the +PMH command. With Call Waiting Detection (+PCW command) enabled, an incoming call can be detected while online. Using a string of commands, the modem negotiates with the server to place the data connection on hold while the line is released so that it can be used to conduct a voice call. Once the voice call is completed, the modem can quickly renegotiate with the server back to the original data call.

- An alternative method is to use communications software that utilizes the Conexant Modem-on-Hold drivers under Windows PC operating systems. Using this method, the software can detect an incoming call, place the data connection on hold, and switch back to a data connection.

#### 2.5.2 Quick Connect

The quick connect function enables the modem to shorten the connect time of subsequent calls to a server supporting quick connect. The quick connect feature is supported by the +PQC command.

#### 2.5.3 PCM Upstream

PCM upstream boosts the upstream data rates between the user and ISP to reduce upload times for large files and email attachments. A maximum of 48 kbps upstream rate is supported with PCM upstream enabled, in contrast to a maximum of 32.2 kbps upstream rate with PCM upstream not enabled. PCM upstream is supported by the +PIG command. PCM upstream is disabled by default.

## 2.6 Error Correction and Data Compression

#### 2.6.1 V.42 Error Correction

V.42 supports two methods of error correction: LAPM and, as a fallback, MNP 4. The modem provides a detection and negotiation technique for determining and establishing the best method of error correction between two modems.

#### 2.6.2 MNP 2-4 Error Correction

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. Supporting stream mode, the modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

#### 2.6.3 V.44 Data Compression

V.44 data compression mode, enabled by the +DS44 command, encodes pages and files associated with Web pages. These files include WEB pages, graphics and image files, and document files. V.44 can provide an effective data throughput rate up to DTE rate for a 56-kbps connection. The improved performance amount varies both with the actual format and with the content of individual pages and files.

#### 2.6.4 V.42 bis Data Compression

V.42 bis data compression mode, enabled by the %Cn command or S46 register, operates when a LAPM connection is established.

The V.42 bis data compression employs a "string learning" algorithm in which a string of characters from the DTE is encoded as a fixed length codeword. Two 2-KB dictionaries are used to store the strings. These dictionaries are dynamically updated during normal operation.

#### 2.6.5 MNP 5 Data Compression

MNP 5 data compression mode, enabled by the %Cn command, operates during an MNP connection.

In MNP 5, the modem increases its throughput by compressing data into tokens before transmitting it to the remote modem, and by decompressing encoded received data before sending it to the DTE.

## 2.7 Telephony Extensions

The following telephony extension features are supported and are typically implemented in designs for set-top box applications and TAM software applications to enhance enduser experience:

- Line In Use detection

- Extension Pickup detection

- Remote Hang-up detection

The telephony extension features are enabled through the -STE command. The -TTE command can be used to adjust the voltage thresholds for the telephony extension features.

#### 2.7.1 Line In Use Detection

The Line In Use Detection feature can stop the modem from disturbing the phone line when the line is already being used. When an automated system tries to dial using ATDT and the phone line is in use, the modem will not go off hook and will respond with the message "LINE IN USE". In the case where no phone line is connected to the modem, the modem will respond with the message "NO LINE".

#### 2.7.2 Extension Pickup Detection

The Extension Pickup Detection feature (also commonly referred as PPD or Parallel phone detection) allows the modem to detect when another telephony device (i.e., fax machine, phone, satellite/cable box) is attempting to use the phone line. When an extension pickup has been detected, the modem will go on-hook and respond with the message "OFF-HOOK INTRUSION".

The Remote Hangup Detection feature will cause the modem to go back on-hook and respond with the message "LINE REVERSAL DETECTED" during a data connection when the remote modem is disconnected for abnormal termination reasons (remote phone line unplugged, remote server/modem shutdown). For Voice applications, this method can be used in addition to silence detection to determine when a remote caller has hung up to terminate a voice recording.

This feature can be used to quickly drop a modem connection in the event when a user picks up a extension phone line. For example, this feature allows set top boxes with an integrated SmartV.XX modem to give normal voice users the highest priority over the telephone line.

This feature can also be used in Telephone Answering Machine applications (TAM). Its main use would be to stop the TAM operation when a phone is picked up.

#### 2.7.3 Remote Hangup Detection

The Remote Hangup Detection feature will cause the modem to go back on-hook and respond with the message "LINE REVERSAL DETECTED" during a data connection when the remote modem is disconnected for abnormal termination reasons (remote phone line unplugged, remote server/modem shutdown). For Voice applications, this method can be used in addition to silence detection to determine when a remote caller has hung up to terminate a voice recording.

### 2.8 Fax Class 1 and Fax Class 1.0 Operation

Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or to fax class 1.0 commands when +FCLASS=1.0.

In the fax mode, the on-line behavior of the modem is different from the data (non-fax) mode. After dialing, modem operation is controlled by fax commands. Some AT commands are still valid but may operate differently than in data modem mode.

Calling tone is generated in accordance with T.30.

### 2.9 Point-of-Sales Support

Point-of-Sales (POS) terminals usually need to exchange a small amount of data in the shortest amount of time. Low speed modulations such as Bell212A or V.22 are still mainly used in POS applications. Additionally, new non-standard sequences have been developed to better support POS applications.

Industry standard and shortened answer tone B103 and V.21 are supported, as well as FastPOS (V.29) and V.22 Fast Connect. POS terminal modulations are supported by the \$F command.

## 2.10 Voice/Audio Mode

Voice and audio functions are supported by the Voice Mode. Voice Mode includes four submodes: Online Voice Command Mode, Voice Receive Mode, Voice Transmit Mode and Full-Duplex Receive and Transmit Mode.

#### 2.10.1 Online Voice Command Mode

This mode results from the connection to the telephone line or a voice/audio I/O device (e.g., microphone, speaker, or handset) through the use of the +FCLASS=8 and +VLS commands. After mode entry, AT commands can be entered without aborting the connection.

#### 2.10.2 Voice Receive Mode

This mode is entered when the +VRX command is active in order to record voice or audio data input at the RIN pin, typically from a microphone/handset or the telephone line.

Received analog voice samples are converted to digital form and compressed for reading by the host. AT commands control the codec bits-per-sample rate.

Received analog mono audio samples are converted to digital form and formatted into 8bit unsigned linear PCM format for reading by the host. AT commands control the bit length and sampling rate. Concurrent DTMF/tone detection is available at the 8 kHz sample rate.

#### 2.10.3 Voice Transmit Mode

This mode is entered when the +VTX command is active in order to playback voice or audio data to the TXA output, typically to a speaker/handset or to the telephone line.

Digitized voice data is decompressed and converted to analog form at the original compression quantization sample-per-bits rate then output to the TXA output.

Digitized audio data is converted to analog form then output to the TXA output.

#### 2.10.4 Full-Duplex Receive and Transmit Mode

This mode is entered when the +VTR command is active in order to concurrently receive and transmit voice.

#### 2.10.5 Audio Mode

The audio mode enables the host to transmit and receive 8-bit audio signals. In this mode, the modem directly accesses the internal analog-to-digital (A/D) converter (ADC) and the digital-to-analog (D/A) converter (DAC). Incoming analog audio signals can then be converted to digital format and digital signals can be converted to analog audio output.

#### 2.10.6 Tone Detectors

The tone detector signal path is separate from the main received signal path thus enabling tone detection to be independent of the configuration status. In Tone Mode, all three tone detectors are operational.

#### 2.10.7 Speakerphone Mode

Speakerphone mode is controlled in voice mode with the following commands:

**Use Speakerphone After Dialing or Answering** (+**VSP=1**). +VSP=1 selects speakerphone mode while in +FCLASS=8 mode. Speakerphone operation is entered during Voice Online Command mode after completing dialing or answering.

**Speakerphone Settings.** The +VGM and +VGS commands can be used to control the microphone gain and speaker volume, respectively. VGM and +VGS commands are valid only after the modem has entered the Voice Online mode while in the +VSP=1 setting.

## 2.11 V.80 Synchronous Access Mode (SAM) - Video Conferencing

V.80 Synchronous Access Mode between the modem and the host/DTE is provided for host-controlled communication protocols, e.g., H.324 video conferencing applications.

Voice-call-first (VCF) before switching to a videophone call is also supported.

## 2.12 Full-Duplex Speakerphone (FDSP) Mode (S Models)

The modem operates in FDSP mode when +FCLASS=8 and +VSP=1 (Section 2.10.7).

In FDSP Mode, speech from a microphone or handset is converted to digital form, shaped, and output to the telephone line through the line interface circuit. Speech received from the telephone line is shaped, converted to analog form, and output to the speaker or handset. Shaping includes both acoustic and line echo cancellation.

### 2.13 Caller ID

Both Type I Caller ID (On-Hook Caller ID) and Type II Caller ID (Call Waiting Caller ID) are supported for U.S. and many other countries (see Section 2.14). Both types of Caller ID are enabled/disabled using the +VCID command. Call Waiting Tone detection must be enabled using the +PCW command to detect and decode Call Waiting Caller ID. When enabled, caller ID information (date, time, caller code, and name) can be passed to the DTE in formatted or unformatted form. Inquiry support allows the current caller ID mode and mode capabilities of the modem to be retrieved from the modem.

Type II Caller ID (Call Waiting Caller ID) detection operates only during data mode in V.92, V.90, V.34, V.32bis, or V.32.

## 2.14 Worldwide Country Support

Internal modem firmware supports 29 country profiles (see Section 1.3.2). These country profiles include the following country-dependent parameters:

- Dial tone detection levels and frequency ranges.

- DTMF dialing parameters: Transmit output level, DTMF signal duration, and DTMF interdigit interval.

- Pulse dialing parameters: Make/break times, set/clear times, and dial codes are programmable

- Ring detection frequency range.

- Type I and Type II Caller ID detection are supported for many countries. Contact your local Conexant sales office for additional country support.

- Blind dialing enabled/disable.

- Carrier transmit level (through S91 for data and S92 for fax). The maximum, minimum, and default values can be defined to match specific country and DAA requirements.

- Calling tone is generated in accordance with V.25. Calling tone may be toggled (enabled/disabled) by inclusion of a "^" character in a dial string. It may also be disabled.

- Frequency and cadence of tones for busy, ringback, congested, warble, dial tone 1, and dial tone 2.

- Answer tone detection period.

• Blacklist parameters. The modem can operate in accordance with requirements of individual countries to prevent misuse of the network by limiting repeated calls to the same number when previous call attempts have failed. Call failure can be detected for reasons such as no dial tone, number busy, no answer, no ringback detected, voice (rather than modem) detected, and key abort (dial attempt aborted by user). Actions resulting from such failures can include specification of minimum inter-call delay, extended delay between calls, and maximum numbers of retries before the number is permanently forbidden ("blacklisted").

These country profiles may be altered or customized by modifying the country-dependent parameters. Additional profiles may also be included. There are two ways to add or modify profiles:

- Incorporating additional or modified profiles into external flash ROM containing the entire modem firmware code.

- Linking additional or modified profiles from an external serial EEPROM (needed only if the external flash ROM capacity is exceeded.