# 3-Mode Surround and Vocal Cancellation

## **Description**

The CXA1842S is a bipolar IC which combines 3-mode surround, bass boosting and vocal cancellation function into a single chip.

#### **Features**

- 3-mode surround (surround A, surround B, simulated stereo)

- Vocal cancellation function

- · Bass boosting function

### **Applications**

CD Radio-cassette tape recorders, equipment with Karaoke functions

#### **Structure**

Bipolar silicon monolithic IC

# **Absolute Maximum Ratings** (Ta=25°C)

| <ul> <li>Supply voltage</li> </ul>      | Vcc  | 14          | V  |

|-----------------------------------------|------|-------------|----|

| Operating temperature                   | Topr | -20 to +75  | °C |

| <ul> <li>Storage temperature</li> </ul> | Tstg | -65 to +150 | °C |

| • Allowable power dissipa               | tion |             |    |

|                                         | Pp   | 880         | mW |

## **Recommended Operating Conditions**

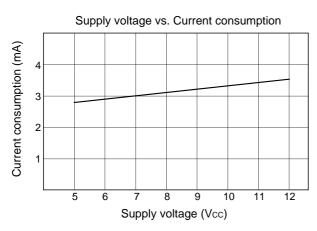

Supply voltage Vcc 5 to 12 V

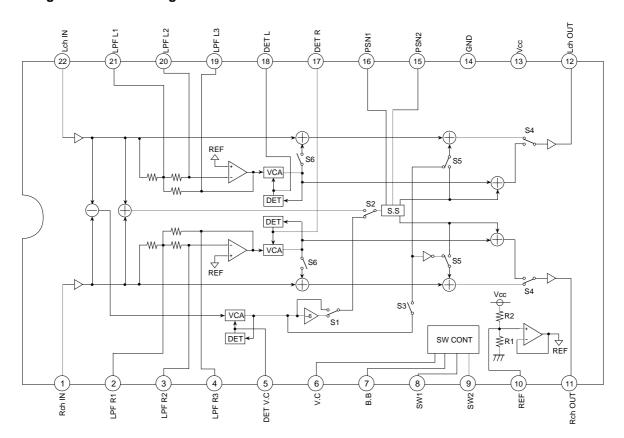

### **Block Diagram and Pin Configuration**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Pin Description**

(Vcc=10V, Ta=25°C)

| Pin<br>No.                    | Symbol                                         | Pin<br>Voltage | Equivalent Circuit                                      | Description                                           |

|-------------------------------|------------------------------------------------|----------------|---------------------------------------------------------|-------------------------------------------------------|

| 1 22                          | Rch IN                                         | 5.0V           | Vcc  1  W 129  ≤56K  AGND  777 GND                      | Channel L input pin Channel R                         |

| 2<br>21<br>3<br>20<br>4<br>19 | LPF R1<br>LPF L1<br>LPF R2<br>LPF L2<br>LPF L3 | 5.0V           | 32K<br>64K 80K AGND<br>21 7///<br>3 4<br>4 4<br>19 7/// | Time constants for L.P.F.                             |

| 5<br>17<br>18                 | DET V.C  DET R  DET L                          | 0.5V           | Vcc  5 17 18 100K \$≥200  100K \$≥200                   | Level detector pin.  To be connected with a capacitor |

| Pin<br>No.       | Symbol             | Pin<br>Voltage | Equivalent Circuit                                       | Description                                                                |  |

|------------------|--------------------|----------------|----------------------------------------------------------|----------------------------------------------------------------------------|--|

| 6<br>7<br>8<br>9 | V.C<br>B.B<br>SW 1 |                | Vcc Vcc AGND 7 129 9                                     | SW is turned ON when this pin is connected to GND                          |  |

| 10               | REF                | 5.0V           | Vcc                                                      | Reference voltage<br>(1/2 Vcc)                                             |  |

| 11               | Rch OUT            | 5.0V           | 297 Vcc  111 W 129 297 V                                 | Channel R Channel L output pin                                             |  |

| 13               | Vcc                | 10V            |                                                          | Power supply                                                               |  |

| 14               | GND                | 0              |                                                          | GND pin                                                                    |  |

| 15               | PSN 2<br>PSN 1     | 5.0V           | Vcc W 15 16 16 16 17 17 17 17 17 17 17 17 17 17 17 17 17 | The pin to be connected with a capacitor for time constants of phase shift |  |

### **Electrical Characteristics**

(Vcc=10V, Ta=25°C)

| No.  | ltem                          | Conditions          | SW conditions |    |    |    |    | Min. | Тур. | Max.     | Unit |        |       |

|------|-------------------------------|---------------------|---------------|----|----|----|----|------|------|----------|------|--------|-------|

| INO. | ite iii                       | Conditions          |               | S2 | S3 | S4 | S5 | S6   | S7   | IVIII I. | тур. | IVIAA. | OTILL |

| 1    | No signal current             | Vin=GND             |               |    | 0  |    |    | 0    |      | 1.6      | 3.35 | 5.1    | mA    |

| 2    | Lch gain                      | Vin=2Vrms, f=1kHz   |               |    | 0  |    |    |      |      | - 3      | 0    | 3      | dB    |

| 3    | Rch gain                      | <b>\</b>            |               |    | 0  |    | 0  |      | 0    | - 3      | 0    | 3      | dB    |

| 4    | Channel balance               | Lch gain - Rch gain | _             | _  | _  | _  | _  | _    | _    | - 3      | 0    | 3      | dB    |

| 5    | Lch total harmonic distortion | Vin=2Vrms, f=1kHz   |               |    | 0  |    |    |      |      | _        | 0.07 | 0.1    | %     |

| 6    | Rch total harmonic distortion | <b>\</b>            |               |    | 0  |    | 0  |      | 0    | _        | 0.07 | 0.1    | %     |

| 7    | Lch noise level               | Vin=GND             |               |    | 0  |    |    | 0    |      | _        | - 90 | - 80   | dBm   |

| 8    | Rch noise level               | <b>\</b>            |               |    | 0  |    |    | 0    | 0    | _        | - 90 | - 80   | dBm   |

| 9    | Channel separation            | Vin=2Vrms, f=1kHz   |               |    | 0  |    |    |      | 0    | 55       | 63   | _      | dB    |

O…indicates "ON".

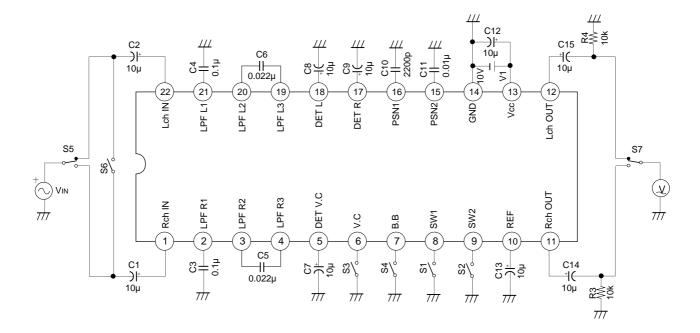

### **Electrical Characteristics Measurement Circuit**

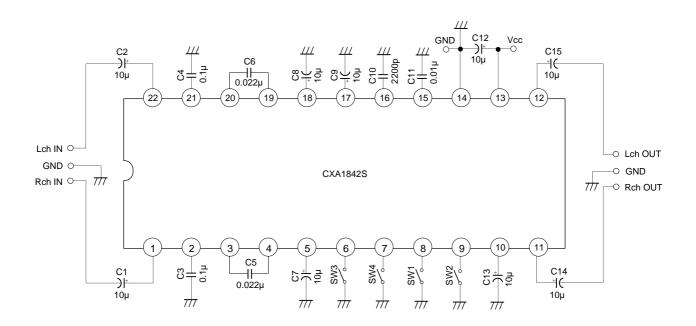

# **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

# Mode Switch Correspondence

| No. | MODE             | SW1 | SW2 | SW3 |

|-----|------------------|-----|-----|-----|

| 1   | Simulated Stereo | ON  | ON  | ON  |

| 2   | Surround A       | ON  | OFF | ON  |

| 3   | Surround B       | OFF | ON  | ON  |

| 4   | Pass             | OFF | OFF | ON  |

| 5   | Vocal cancel     | _   | _   | OFF |

----don't care

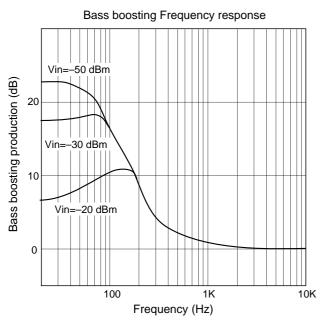

Bass boosting ON when SW4=ON (Invalid during vocal cancellation)

VTH for SW ... VTH (H) = VCC to 3 V, VTH (L) = 2 V to GND

### **Description of Functions**

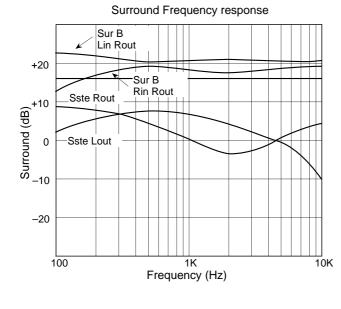

### (1) Simulated Stereo

The sum of the L and R signals is input to the Simulated Stereo\* (hereafter S.S) block, and a simulated stereo signal is generated.

### (2) Surround A (matrix surround)

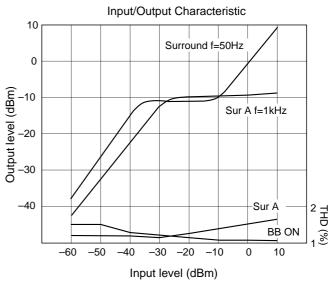

The difference of the L and R signals is raised in level by the VCA (maximum 18 dB (typ.)), and is added to the raw signal.

#### (3) Surround B

The difference of the L and R signals is raised in level by the VCA (maximum 18 dB (typ.)), is input to the S.S block, and is then added to the raw signal.

### (4) Pass

The L and R signals are output without modification.

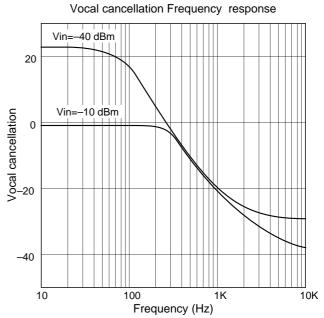

### (5) Vocal Cancellation

The difference of the L and R signals is input to the S.S block after first passing through the AGC circuit, and is then output to L and R. In contrast with conventional products, the vocal cancel signal (L-R signal) is raised in level by the VCA (max. 12 dB typ.), and low frequency part is enhanced, to prevent reduction in the acoustic pressure level when vocal cancellation is ON.

#### \* Simulated Stereo circuit:

Phases in the audio band are divided into two separate orthogonal channels and treated as L+R and L-R signals, and are added and subtracted to produce simulated L and R signals. All-pass network.

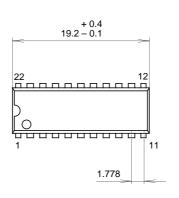

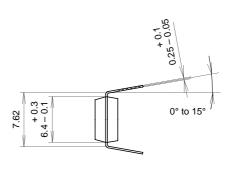

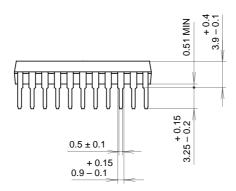

# Package Outline Unit: mm

# 22PIN SDIP (PLASTIC)

# PACKAGE STRUCTURE

| SONY CODE  | SDIP-22P-01    |

|------------|----------------|

| EIAJ CODE  | SDIP022-P-0300 |

| JEDEC CODE |                |

| MOLDING COMPOUND | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER ALLOY   |

| PACKAGE WEIGHT   | 0.95g          |