# 64K x 18 Synchronous Cache RAM

#### **Features**

- Supports 66-MHz Pentium<sup>™</sup> microprocessor cache systems with zero wait states

- 64K by 18 common I/O

- · Fast clock-to-output times

- —8.5 ns

- Two-bit wraparound counter supporting Pentium microprocessor and 486 burst sequence (7C1031)

- · Two-bit wraparound counter supporting linear burst sequence (7C1032)

- Separate processor and controller address strobes

- · Synchronous self-timed write

- Direct interface with the processor and external cache controller

- · Asynchronous output enable

- I/Os capable of 3.3V operation

- JEDEC-standard pinout

- 52-pin PLCC and PQFP packaging

#### **Functional Description**

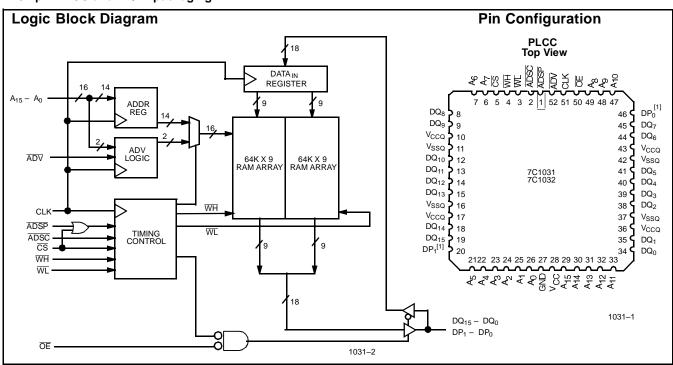

The CY7C1031 and CY7C1032 are 64K by 18 synchronous cache RAMs designed to interface with high-speed microprocessors with minimum glue logic. Maximum access delay from clock rise is 8.5 ns. A 2-bit on-chip counter captures the first address in a burst and increments the address automatically for the rest of the burst access.

The CY7C1031 is designed for Intel Pentium and i486 CPU-based systems; its counter follows the burst sequence of the Pentium and the i486 processors. The CY7C1032 is architected for processors with linear burst sequences. Burst accesses can be initiated with the processor address strobe (ADSP) or the cache controller address strobe (ADSC) inputs. Address advancement is controlled by the address advancement (ADV) input.

A synchronous self-timed write mechanism is provided to simplify the write interface. A synchronous chip select input and an asynchronous output enable input provide easy control for bank selection and output three-state control.

#### **Selection Guide**

|                          | 7C1031-7<br>7C1032-7 | 7C1031-8<br>7C1032-8 | 7C1031-10<br>7C1032-10 | 7C1031-12<br>7C1032-12 |     |

|--------------------------|----------------------|----------------------|------------------------|------------------------|-----|

| Maximum Access Time (ns) |                      | 7                    | 8.5                    | 10                     | 12  |

| Maximum Operating        | Commercial           | 300                  | 280                    | 280                    | 230 |

| Current (mA)             | Military             |                      |                        |                        | 235 |

Shaded area contains advanced information.

Pentium is a trademark of Intel Corporation.

1. DP<sub>0</sub> and DP<sub>1</sub> are functionally equivalent to DQ<sub>v</sub>.

#### Functional Description (continued)

#### Single Write Accesses Initiated by ADSP

This access is initiated when the following conditions are satisfied at clock rise: (1)  $\overline{CS}$  is LOW and (2)  $\overline{ADSP}$  is LOW.  $\overline{ADSP}$ -triggered write cycles are completed in two clock periods. The address at  $A_0$  through  $A_{15}$  is loaded into the address register and address advancement logic and delivered to the RAM core. The write signal is ignored in this cycle because the cache tag or other external logic uses this clock period to perform address comparisons or protection checks. If the write is allowed to proceed, the write input to the CY7C1031 and CY7C1032 will be pulled LOW before the next clock rise.  $\overline{ADSP}$  is ignored if  $\overline{CS}$  is HIGH.

If  $\overline{WH}$ ,  $\overline{WL}$ , or both are LOW at the next clock rise, information presented at DQ $_0$  – DQ $_{15}$  and DP $_0$  – DP $_1$  will be written into the location specified by the address advancement logic.  $\overline{WL}$  controls the writing of DQ $_0$  – DQ $_7$  and DP $_0$  while  $\overline{WH}$  controls the writing of DQ $_8$  – DQ $_{15}$  and DP $_1$ . Because the CY7C1031 and CY7C1032 are common-I/O devices, the output enable signal ( $\overline{OE}$ ) must be deasserted before data from the CPU is delivered to DQ $_0$  – DQ $_{15}$  and DP $_0$  – DP $_1$ . As a safety precaution, the appropriate data lines are three-stated in the cycle where  $\overline{WH}$ ,  $\overline{WL}$ , or both are sampled LOW, regardless of the state of the  $\overline{OE}$  input.

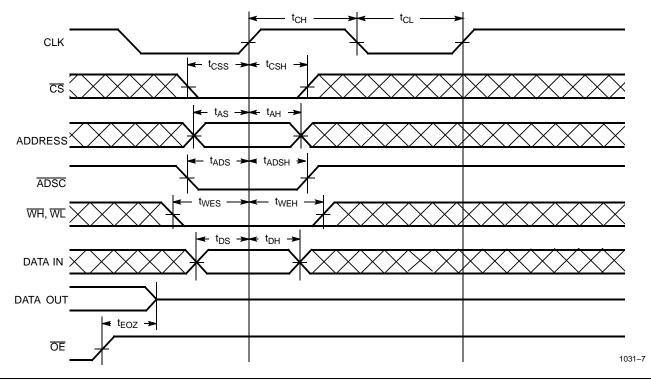

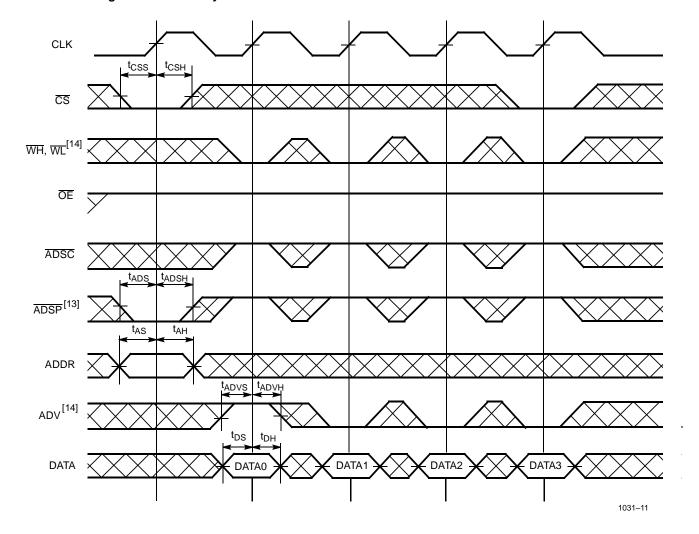

#### Single Write Accesses Initiated by ADSC

This write access is initiated when the following conditions are satisfied at rising edge of the clock: (1)  $\overline{CS}$  is LOW, (2)  $\overline{ADSC}$  is LOW, and (3)  $\overline{WH}$  or  $\overline{WL}$  are LOW.  $\overline{ADSC}$  triggered accesses are completed in a single clock cycle.

The address at  $A_0$  through  $A_{15}$  is loaded into the address register and address advancement logic and delivered to the RAM core. Information presented at  $DQ_0 - DQ_{15}$  and  $DP_0 - DP_1$  will be written into the location specified by the address advancement logic. Since the CY7C1031 and the CY7C1032 are common-I/O devices, the output enable signal  $(\overline{OE})$  must be deasserted before data from the cache controller is delivered to the data and parity lines. As a safety precaution, the appropriate data and parity lines are three-stated in the cycle where  $\overline{WH}$  and  $\overline{WL}$  are sampled LOW regardless of the state of the  $\overline{OE}$  input.

#### Single Read Accesses

A single read access is initiated when the following conditions are satisfied at clock rise: (1)  $\overline{CS}$  is LOW, (2)  $\overline{ADSP}$  or  $\overline{ADSC}$

is LOW, and (3)  $\overline{\text{WH}}$  and  $\overline{\text{WL}}$  are HIGH. The address at  $A_0$  through  $A_{15}$  is stored into the address advancement logic and delivered to the RAM core. If the output enable ( $\overline{\text{OE}}$ ) signal is asserted (LOW), data will be available at the data outputs a maximum of 8.5 ns after clock rise.  $\overline{\text{ADSP}}$  is ignored if  $\overline{\text{CS}}$  is HIGH.

#### **Burst Sequences**

The CY7C1031 provides a 2-bit wraparound counter, fed by pins  $A_0 - A_1$ , that implements the Intel 80486 and Pentium processor's address burst sequence (see *Table 1*). Note that the burst sequence depends on the first burst address.

Table 1. Counter Implementation for the Intel Pentium/80486 Processor's Sequence

| First<br>Address | Address Address  |                | Fourth<br>Address |

|------------------|------------------|----------------|-------------------|

| $A_{X+1}, A_{X}$ | $A_{X+1}, A_{X}$ | $A_{X+1}, A_X$ | $A_{X+1}, A_X$    |

| 00               | 01               | 10             | 11                |

| 01               | 00               | 11             | 10                |

| 10               | 11               | 00             | 01                |

| 11               | 10               | 01             | 00                |

The CY7C1032 provides a two-bit wraparound counter, fed by pins  $A_0 - A_1$ , that implements a linear address burst sequence (see *Table 2*).

Table 2. Counter Implementation for a Linear Sequence

| First<br>Address | Second<br>Address | Third<br>Address | Fourth<br>Address |

|------------------|-------------------|------------------|-------------------|

| $A_{X+1}, A_X$   | $A_{X+1}, A_X$    | $A_{X+1}, A_X$   | $A_{X+1}, A_X$    |

| 00               | 01                | 10               | 11                |

| 01               | 10                | 11               | 00                |

| 10               | 11                | 00               | 01                |

| 11               | 00                | 01               | 10                |

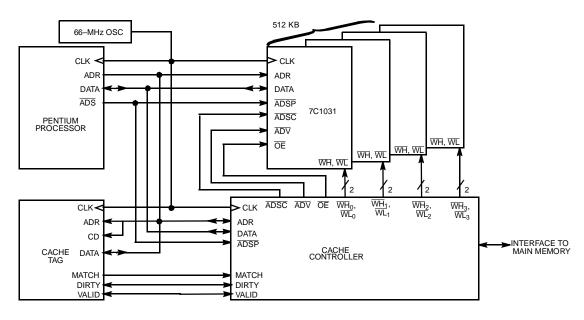

#### **Application Example**

Figure 1 shows a 512-Kbyte secondary cache for the Pentium microprocessor using four CY7C1031 cache RAMs.

Figure 1. Cache Using Four CY7C1031s

#### **Pin Definitions**

| Signal Name                       | Туре         | # of Pins | Description                          |

|-----------------------------------|--------------|-----------|--------------------------------------|

| V <sub>CC</sub>                   | Input        | 1         | +5V Power                            |

| V <sub>CCQ</sub>                  | Input        | 4         | +5V or 3.3V (Outputs)                |

| GND                               | Input        | 1         | Ground                               |

| $V_{SSQ}$                         | Input        | 4         | Ground (Outputs)                     |

| CLK                               | Input        | 1         | Clock                                |

| $A_{15} - A_0$                    | Input        | 16        | Address                              |

| ADSP                              | Input        | 1         | Address Strobe from Processor        |

| ADSC                              | Input        | 1         | Address Strobe from Cache Controller |

| WH                                | Input        | 1         | Write Enable – High Byte             |

| WL                                | Input        | 1         | Write Enable – Low Byte              |

| ADV                               | Input        | 1         | Advance                              |

| OE                                | Input        | 1         | Output Enable                        |

| CS                                | Input        | 1         | Chip Select                          |

| DQ <sub>15</sub> -DQ <sub>0</sub> | Input/Output | 16        | Regular Data                         |

| DP <sub>1</sub> –DP <sub>0</sub>  | Input/Output | 2         | Parity Data                          |

### **Pin Descriptions**

| Signal<br>Name                  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Signa                     | als |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLK                             | 1   | Clock signal. It is used to capture the address, the data to be written, and the following control signals: ADSP, ADSC, CS, WH, WL, and ADV. It is also used to advance the on-chip auto-address-increment logic (when the appropriate control signals have been set).                                                                                                                                                                                                                                                                                                                                                        |

| A <sub>15</sub> -A <sub>0</sub> | I   | Sixteen address lines used to select one of 64K locations. They are captured in an on-chip register on the rising edge of CLK if $\overline{\text{ADSP}}$ or $\overline{\text{ADSC}}$ is LOW. The rising edge of the clock also loads the lower two address lines, $A_1 - A_0$ , into the on-chip auto-address-increment logic if $\overline{\text{ADSP}}$ or $\overline{\text{ADSC}}$ is LOW.                                                                                                                                                                                                                                |

| ADSP                            | I   | Address strobe from processor. This signal is sampled at the rising edge of CLK. When this input and/or $\overline{ADSC}$ is asserted, $A_0$ – $A_{15}$ will be captured in the on-chip address register. It also allows the lower two address bits to be loaded into the on-chip auto-address-increment logic. If both $\overline{ADSP}$ and $\overline{ADSP}$ are asserted at the rising edge of CLK, only $\overline{ADSP}$ will be recognized. The $\overline{ADSP}$ input should be connected to the $\overline{ADS}$ output of the processor. $\overline{ADSP}$ is ignored when $\overline{CS}$ is HIGH.                |

| ADSC                            | 1   | Address strobe from cache controller. This signal is sampled at the rising edge of CLK. When this input and/or $\overline{\text{ADSP}}$ is asserted, $\text{A}_0$ – $\text{A}_{15}$ will be captured in the on-chip address register. It also allows the lower two address bits to be loaded into the on-chip auto-address-increment logic. The $\overline{\text{ADSC}}$ input should <i>not</i> be connected to the $\overline{\text{ADS}}$ output of the processor.                                                                                                                                                         |

| WH                              | I   | Write signal for the high-order half of the RAM array. This signal is sampled by the rising edge of CLK. If $\overline{WH}$ is sampled as LOW, i.e., asserted, the control logic will perform a self-timed write of DQ <sub>15</sub> – DQ <sub>8</sub> and DP <sub>1</sub> from the on-chip data register into the selected RAM location. There is one exception to this. If $\overline{ADSP}$ , $\overline{WH}$ , and $\overline{CS}$ are asserted (LOW) at the rising edge of CLK, the write signal, $\overline{WH}$ , is ignored. Note that $\overline{ADSP}$ has no effect on $\overline{WH}$ if $\overline{CS}$ is HIGH. |

| WL                              | I   | Write signal for the low-order half of the RAM array. This signal is sampled by the rising edge of CLK. If $\overline{WL}$ is sampled as LOW, i.e., asserted, the control logic will perform a self-timed write of DQ <sub>7</sub> – DQ <sub>0</sub> and DP <sub>0</sub> from the on-chip data register into the selected RAM location. There is one exception to this. If $\overline{ADSP}$ , $\overline{WL}$ , and $\overline{CS}$ are asserted (LOW) at the rising edge of CLK, the write signal, $\overline{WL}$ , is ignored. Note that $\overline{ADSP}$ has no effect on $\overline{WL}$ if $\overline{CS}$ is HIGH.   |

### Pin Descriptions (continued)

| Signal<br>Name                    | 1/0   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-----------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ADV                               | I     | Advance. This signal is sampled by the rising edge of CLK. When it is asserted, it automatically increments the 2-bit on-chip auto-address-increment counter. In the CY7C1032, the address will be incremented linearly. In the CY7C1031, the address will be incremented according to the Pentium/486 burst sequence. This signal is ignored if ADSP or ADSC is asserted concurrently with CS. Note that ADSP has no effect on ADV if CS is HIGH. |  |  |  |  |  |

| CS                                | I     | Chip select. This signal is sampled by the rising edge of CLK. If $\overline{CS}$ is HIGH and $\overline{ADSC}$ is LOW, the SRAM is deselected. If $\overline{CS}$ is LOW and $\overline{ADSC}$ or $\overline{ADSP}$ is LOW, a new address is captured by the address register. If $\overline{CS}$ is HIGH, $\overline{ADSP}$ is ignored.                                                                                                          |  |  |  |  |  |

| ŌĒ                                | I     | Output enable. This signal is an asynchronous input that controls the direction of the data I/O pins. If $\overline{OE}$ is asserted (LOW), the data pins are outputs, and the SRAM can be read (as long as $\overline{CS}$ was asserted when it was sampled at the beginning of the cycle). If $\overline{OE}$ is deasserted (HIGH), the data I/O pins will be three-stated, functioning as inputs, and the SRAM can be written.                  |  |  |  |  |  |

| Bidirectional Signals             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| DQ <sub>15</sub> -DQ <sub>0</sub> | ) I/O | Sixteen bidirectional data I/O lines. $DQ_{15} - DQ_8$ are inputs to and outputs from the high-order half of the RAM array, while $DQ_7 - DQ_0$ are inputs to and outputs from the low-order half of the RAM array. As inputs, they feed into an on-chip data                                                                                                                                                                                      |  |  |  |  |  |

DQ $_{15}$ –DQ $_0$  I/O Sixteen bidirectional data I/O lines. DQ $_{15}$  – DQ $_8$  are inputs to and outputs from the high-order half of the RAM array, while DQ $_7$  – DQ $_0$  are inputs to and outputs from the low-order half of the RAM array. As inputs, they feed into an on-chip data register that is triggered by the rising edge of CLK. As outputs, they carry the data read from the selected location in the RAM array. The direction of the data pins is controlled by  $\overline{\text{OE}}$ : when  $\overline{\text{OE}}$  is high, the data pins are three-stated and can be used as inputs; when  $\overline{\text{OE}}$  is low, the data pins are driven by the output buffers and are outputs. DQ $_{15}$  – DQ $_8$  and DQ $_7$  – DQ $_0$  are also three-stated when  $\overline{\text{WH}}$  and  $\overline{\text{WL}}$ , respectively, is sampled LOW at clock rise.

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature .....-65°C to +150°C

Ambient Temperature with

Power Applied......–55°C to +125°C Supply Voltage on  $V_{CC}$  Relative to GND.....-0.5V to +7.0V

DC Voltage Applied to Outputs

in High Z State<sup>[2]</sup>......-0.5V to V<sub>CC</sub> + 0.5V DC Input Voltage<sup>[2]</sup>.....-0.5V to V<sub>CC</sub> + 0.5V

Current into Outputs (LOW)......20 mA

| Static Discharge Voltage       | . >2001V |

|--------------------------------|----------|

| (per MIL-STD-883, Method 3015) |          |

| Latch-Up Current               | >200 mA  |

## **Operating Range**

| Range | Ambient<br>Temperature <sup>[3]</sup> | v <sub>cc</sub> | V <sub>CCQ</sub>        |

|-------|---------------------------------------|-----------------|-------------------------|

| Com'l | 0°C to +70°C                          | 5V ± 5%         | 3.0V to V <sub>CC</sub> |

| Mil   | −55°C to +125°C                       | 5V ± 5%         | 5V ±5%                  |

# Electrical Characteristics Over the Operating Range<sup>[4]</sup>

|                  |                                             |                                                                                                                                        |                    |      | 031–7<br>032–7            |      | 031–8<br>032–8            |      | 031–10<br>032–10          |      | 031–12<br>032–12          |      |

|------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|---------------------------|------|---------------------------|------|---------------------------|------|---------------------------|------|

| Parameter        | Description                                 | Test Condi                                                                                                                             | tions              | Min. | Max.                      | Min. | Max.                      | Min. | Max.                      | Min. | Max.                      | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage                         | $V_{CC} = Min.,$<br>$I_{OH} = -4.0 \text{ mA}$                                                                                         |                    | 2.4  | V <sub>CCQ</sub>          | 2.4  | $V_{CCQ}$                 | 2.4  | V <sub>CCQ</sub>          | 2.4  | V <sub>CCQ</sub>          | V    |

| V <sub>OL</sub>  | Output LOW Voltage                          | V <sub>CC</sub> = Min,<br>I <sub>OL</sub> =8.0 mA                                                                                      |                    |      | 0.4                       |      | 0.4                       |      | 0.4                       |      | 0.4                       | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                          |                                                                                                                                        |                    | 2.2  | V <sub>CC</sub><br>+ 0.3V | V    |

| V <sub>IL</sub>  | Input LOW Voltage <sup>[2]</sup>            |                                                                                                                                        |                    | -0.3 | 0.8                       | -0.3 | 0.8                       | -0.3 | 0.8                       | -0.3 | 0.8                       | V    |

| I <sub>X</sub>   | Input Load Current                          | $GND \le V_I \le V_C$                                                                                                                  | С                  | -1   | 1                         | -1   | 1                         | -1   | 1                         | -1   | 1                         | μΑ   |

| I <sub>OZ</sub>  | Output Leakage<br>Current                   | $GND \le V_1 \le V_{CC_1}$<br>Output Disabled                                                                                          |                    | -5   | 5                         | -5   | 5                         | -5   | 5                         | -5   | 5                         | μА   |

| Ios              | Output Short Circuit Current <sup>[5]</sup> | V <sub>CC</sub> =Max., V <sub>Ol</sub>                                                                                                 | <sub>JT</sub> =GND |      | -300                      |      | -300                      |      | -300                      |      | -300                      | mA   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating                   | V <sub>CC</sub> =Max.,                                                                                                                 | Com'l              |      | 300                       |      | 280                       |      | 280                       |      | 230                       | mA   |

|                  | Supply Current                              | lout=0mA,<br>f=f <sub>MAX</sub> =1/t <sub>CYC</sub>                                                                                    | Mil                |      |                           |      |                           |      |                           |      | 250                       |      |

| I <sub>SB1</sub> | Automatic CE                                | Max. $V_{CC}$ , $\overline{CS}$                                                                                                        | Com'l              |      | 90                        |      | 80                        |      | 80                        |      | 60                        | mA   |

|                  | Power-Down<br>Current—TTL Inputs            | $ \geq V_{IH}, V_{IN} \geq V_{IH} $ or $V_{IN} \leq V_{IL},$ $f=f_{MAX}$                                                               | Mil                |      |                           |      |                           |      |                           |      | 70                        | mA   |

| I <sub>SB2</sub> | Automatic CE                                | Max. V <sub>CC</sub> , CS                                                                                                              | Com'l              |      | 30                        |      | 30                        |      | 30                        |      | 30                        | mA   |

|                  | Power-Down Current — CMOS Inputs            | $\geq$ V <sub>CC</sub> $-$ 0.3V,<br>V <sub>IN</sub> $\geq$ V <sub>CC</sub> $-$ 0.3V or V <sub>IN</sub> $\leq$ 0.3V, f=0 <sup>[6]</sup> | Mil                |      |                           |      |                           |      |                           |      | 50                        |      |

Shaded area contains advanced information.

- Minimum voltage equals -2.0V for pulse durations of less than 20 ns.

- T<sub>A</sub> is the "instant on" case temperature.

- See the last page for Group A subgroup testing information.

Not more than one output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds. Inputs are disabled, clock is allowed to run at speed.

## Capacitance<sup>[7]</sup>

| Parameter                      | Description        | Description Test Conditions                           |       |     | Unit |

|--------------------------------|--------------------|-------------------------------------------------------|-------|-----|------|

| C <sub>IN</sub> : Addresses    | Input Capacitance  | $T_A = 25^{\circ}C$ , $f = 1$ MHz,<br>$V_{CC} = 5.0V$ | Com'l | 4.5 | pF   |

|                                |                    | $V_{CC} = 5.0V$                                       | Mil   | 6   | pF   |

| C <sub>IN</sub> : Other Inputs |                    |                                                       | Com'l | 5   | pF   |

|                                |                    |                                                       | Mil   | 8   | pF   |

| OUT                            | Output Capacitance |                                                       | Com'l | 8   | pF   |

|                                |                    |                                                       | Mil   | 10  | pF   |

Shaded areas contain advanced information

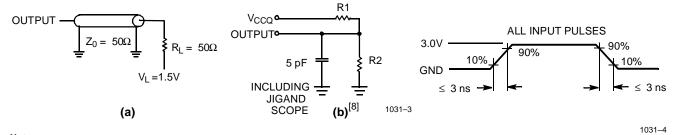

#### **AC Test Loads and Waveforms**

- Tested initially and after any design or process changes that may affect these parameters. Resistor values for  $V_{CCQ}$ =5V are: R1=1179 $\Omega$  and R2=868 $\Omega$ . Resistor values for  $V_{CCQ}$ =3.3V are R1=317 $\Omega$  and R2=348 $\Omega$ .

# Switching Characteristics Over the Operating Range<sup>[9]</sup>

|                   |                                                           |      | )31–7<br>)32–7 |      | )31–8<br>)32–8 | 7C1031-10<br>7C1032-10 |      | 7C1031-12<br>7C1032-12 |      |      |

|-------------------|-----------------------------------------------------------|------|----------------|------|----------------|------------------------|------|------------------------|------|------|

| Parameter         | Description                                               | Min. | Max.           | Min. | Max.           | Min.                   | Max. | Min.                   | Max. | Unit |

| t <sub>CYC</sub>  | Clock Cycle Time                                          | 13.3 |                | 15   |                | 15                     |      | 20                     |      | ns   |

| t <sub>CH</sub>   | Clock HIGH                                                | 5    |                | 5    |                | 6                      |      | 8                      |      | ns   |

| t <sub>CL</sub>   | Clock LOW                                                 | 5    |                | 5    |                | 6                      |      | 8                      |      | ns   |

| t <sub>AS</sub>   | Address Set-Up Before CLK Rise                            | 2.5  |                | 2.5  |                | 2.5                    |      | 2.5                    |      | ns   |

| t <sub>AH</sub>   | Address Hold After CLK Rise                               | 0.5  |                | 0.5  |                | 0.5                    |      | 0.5                    |      | ns   |

| t <sub>CDV</sub>  | Data Output Valid After CLK Rise                          |      | 7              |      | 8.5            |                        | 10   |                        | 12   | ns   |

| t <sub>DOH</sub>  | Data Output Hold After CLK Rise                           | 2    |                | 3    |                | 3                      |      | 3                      |      | ns   |

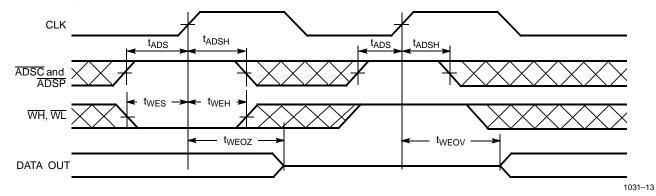

| t <sub>ADS</sub>  | ADSP, ADSC Set-Up Before CLK Rise                         | 2.5  |                | 2.5  |                | 2.5                    |      | 2.5                    |      | ns   |

| t <sub>ADSH</sub> | ADSP, ADSC Hold After CLK Rise                            | 0.5  |                | 0.5  |                | 0.5                    |      | 0.5                    |      | ns   |

| t <sub>WES</sub>  | WH, WL Set-Up Before CLK Rise                             | 2.5  |                | 2.5  |                | 2.5                    |      | 2.5                    |      | ns   |

| t <sub>WEH</sub>  | WH, WL Hold After CLK Rise                                | 0.5  |                | 0.5  |                | 0.5                    |      | 0.5                    |      | ns   |

| t <sub>ADVS</sub> | ADV Set-Up Before CLK Rise                                | 2.5  |                | 2.5  |                | 2.5                    |      | 2.5                    |      | ns   |

| t <sub>ADVH</sub> | ADV Hold After CLK Rise                                   | 0.5  |                | 0.5  |                | 0.5                    |      | 0.5                    |      | ns   |

| t <sub>DS</sub>   | Data Input Set-Up Before CLK Rise                         | 2.5  |                | 2.5  |                | 2.5                    |      | 2.5                    |      | ns   |

| t <sub>DH</sub>   | Data Input Hold After CLK Rise                            | 0.5  |                | 0.5  |                | 0.5                    |      | 0.5                    |      | ns   |

| t <sub>CSS</sub>  | Chip Select Set-Up                                        | 2.5  |                | 2.5  |                | 2.5                    |      | 2.5                    |      | ns   |

| t <sub>CSH</sub>  | Chip Select Hold After CLK Rise                           | 0.5  |                | 0.5  |                | 0.5                    |      | 0.5                    |      | ns   |

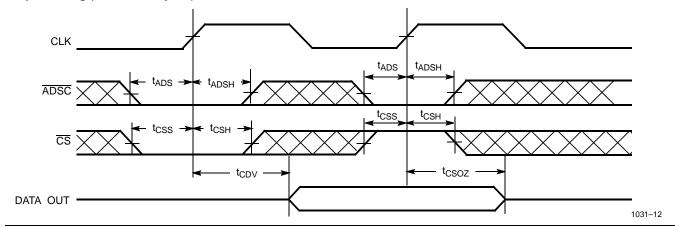

| t <sub>CSOZ</sub> | Chip Select Sampled to Output High Z <sup>[10]</sup>      | 2    | 6              | 2    | 6              | 2                      | 6    | 2                      | 7    | ns   |

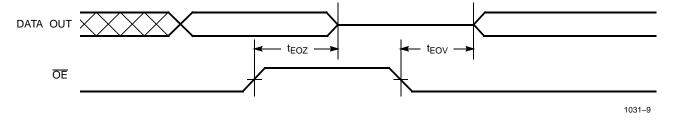

| t <sub>EOZ</sub>  | OE HIGH to Output High Z <sup>[10]</sup>                  | 2    | 6              | 2    | 6              | 2                      | 6    | 2                      | 7    | ns   |

| t <sub>EOV</sub>  | OE LOW to Output Valid                                    |      | 5              |      | 5              |                        | 5    |                        | 6    | ns   |

| t <sub>WEOZ</sub> | WH or WL Sampled LOW to Output High Z <sup>[10, 11]</sup> |      | 5              |      | 5              |                        | 6    |                        | 7    | ns   |

| t <sub>WEOV</sub> | WH or WL Sampled HIGH to Output Valid <sup>[11]</sup>     |      | 7              |      | 8.5            |                        | 10   |                        | 12   | ns   |

Shaded areas contain advanced information

Unless otherwise noted, test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified l<sub>OL</sub>/l<sub>OH</sub> and load capacitance. Shown in (a) and (b) os AC test loads.

t<sub>CSOZ</sub>, t<sub>EOZ</sub>, and t<sub>WEOZ</sub> are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.

At any given voltage and temperature, t<sub>WEOZ</sub> min. is less than t<sub>WEOV</sub> min.

# **Switching Waveforms**

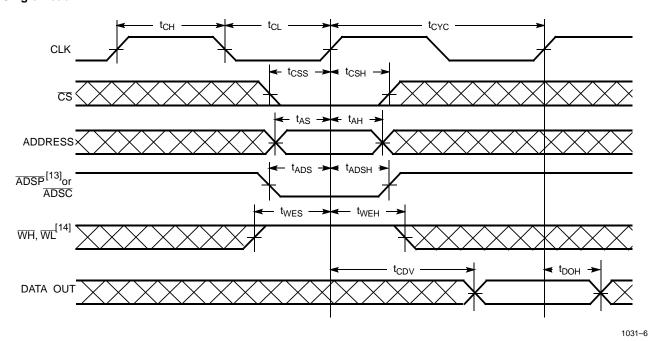

## Single Read<sup>[12]</sup>

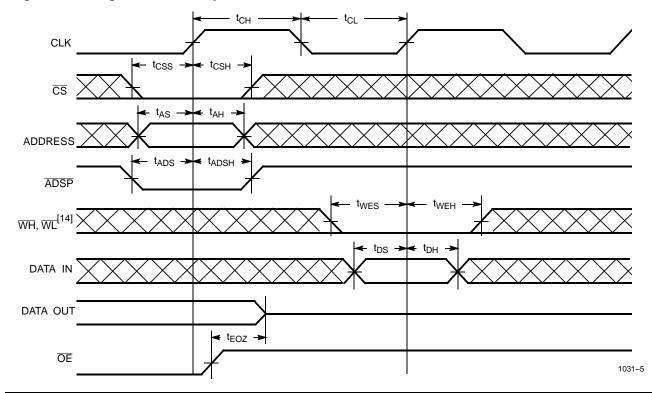

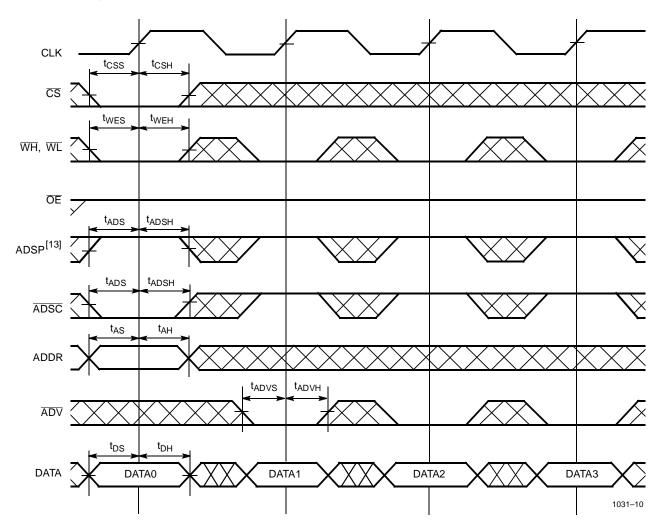

#### Single Write Timing: Write Initiated by ADSP

- DE is LOW throughout this operation.

If ADSP is asserted while CS is HIGH, ADSP will be ignored.

ADSP has no effect on ADV, WL, and WH if CS is HIGH.

## Single Write Timing: Write Initiated by ADSC

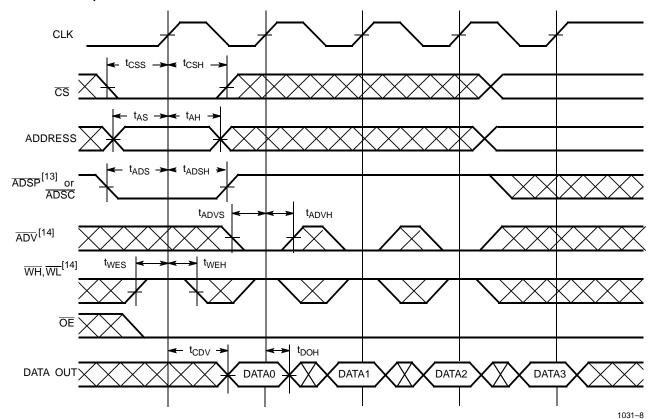

#### **Burst Read Sequence with Four Accesses**

9

## Output (Controlled by OE)

# Write Burst Timing: Write Initiated by ADSC

## Write Burst Timing: Write Initiated by ADSP

#### Output Timing (Controlled by CS)

## Output Timing (Controlled by WH/WL)

## **Truth Table**

| Input |      |      |     |          |     |                                |                                               |

|-------|------|------|-----|----------|-----|--------------------------------|-----------------------------------------------|

| CS    | ADSP | ADSC | ADV | WH or WL | CLK | Address                        | Operation                                     |

| Н     | Х    | L    | Х   | Х        | L→H | N/A                            | Chip deselected                               |

| Н     | L    | Н    | Н   | Н        | L→H | Same address as previous cycle | Read cycle (ADSP ignored)                     |

| Н     | L    | Н    | L   | Н        | L→H | Incremented burst address      | Read cycle, in burst sequence (ADSP ignored)  |

| Н     | L    | Н    | Н   | L        | L→H | Same address as previous cycle | Write cycle (ADSP ignored)                    |

| Н     | L    | Н    | L   | L        | L→H | Incremented burst address      | Write cycle, in burst sequence (ADSP ignored) |

| L     | L    | Х    | Х   | Х        | L→H | External                       | Read cycle, begin burst                       |

| L     | Н    | L    | Х   | Н        | L→H | External                       | Read cycle, begin burst                       |

| L     | Н    | L    | Х   | L        | L→H | External                       | Write cycle, begin burst                      |

| Х     | Н    | Н    | L   | L        | L→H | Incremented burst address      | Write cycle, in burst sequence                |

| Х     | Н    | Н    | L   | Н        | L→H | Incremented burst address      | Read cycle, in burst sequence                 |

| Х     | Н    | Н    | Н   | L        | L→H | Same address as previous cycle | Write cycle                                   |

| Х     | Н    | Н    | Н   | Н        | L→H | Same address as previous cycle | Read cycle                                    |

# **Ordering Information**

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|----------------|-----------------|-------------------------------------|--------------------|

| 7             | CY7C1031-7JC   | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7C1031-7NC   | TBD             | 52-Lead Plastic Quad Flatpack       |                    |

| 8             | CY7C1031-8JC   | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7C1031-8NC   | TBD             | 52-Lead Plastic Quad Flatpack       |                    |

| 10            | CY7C1031-10JC  | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7C1031-10NC  | TBD             | 52-Lead Plastic Quad Flatpack       |                    |

| 12            | CY7C1031-12JC  | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7C1031-12NC  | TBD             | 52-Lead Plastic Quad Flatpack       |                    |

|               | CY7C1031-12YMB | Y59             | 52-Pin Ceramic Leaded Chip Carrier  | Military           |

| Speed (ns) | Ordering Code  | Package<br>Name | Package Type                        | Operating<br>Range |

|------------|----------------|-----------------|-------------------------------------|--------------------|

| 7          | CY7C1032-7JC   | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|            | CY7C1032-7NC   | TBD             | 52-Lead Plastic Quad Flatpack       | 1                  |

| 8          | CY7C1032-8JC   | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|            | CY7C1032-8NC   | TBD             | 52-Lead Plastic Quad Flatpack       |                    |

| 10         | CY7C1032-10JC  | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|            | CY7C1032-10NC  | TBD             | 52-Lead Plastic Quad Flatpack       |                    |

| 12         | CY7C1032-12JC  | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|            | CY7C1032-12NC  | TBD             | 52-Lead Plastic Quad Flatpack       |                    |

|            | CY7C1032-12YMB | Y59             | 52-Pin Ceramic Leaded Chip Carrier  | Military           |

Shaded areas contain advanced information.

Document #: 38-00219-B

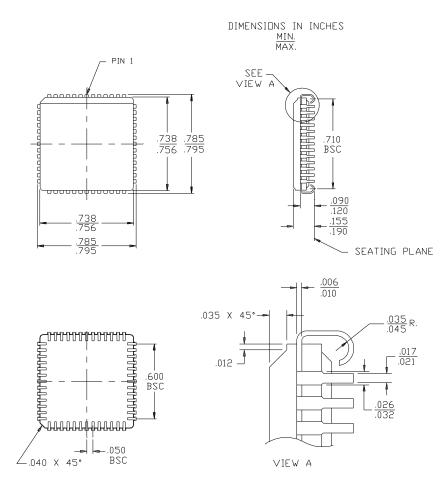

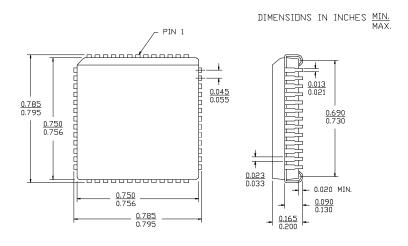

## **Package Diagrams**

#### 52-Lead Plastic Leaded Chip Carrier J69

#### 52-Pin Ceramic Leaded Chip Carrier Y59